USB

Posted QIYUEXIN

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了USB相关的知识,希望对你有一定的参考价值。

1. USB

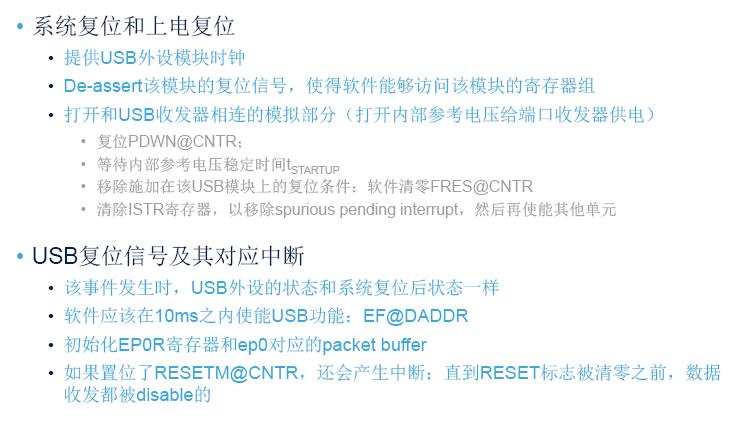

1.1 复位

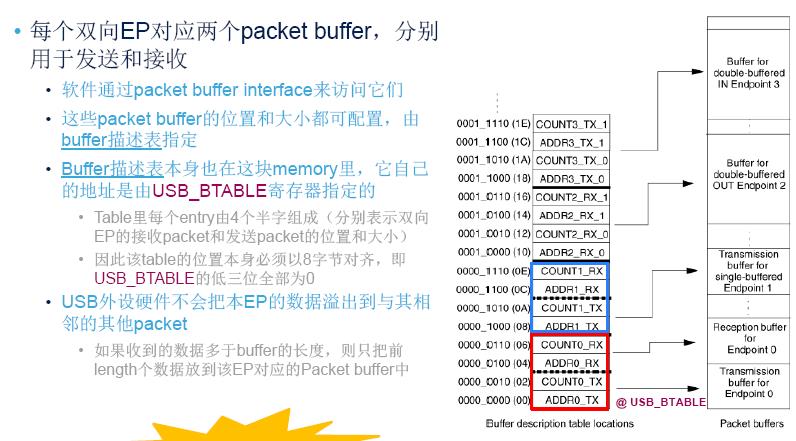

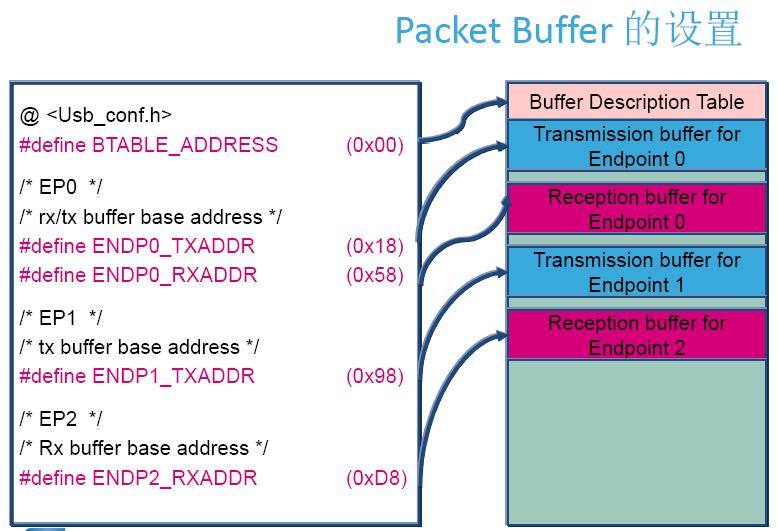

1.2 Packet Buffer的使用(硬件缓冲区)

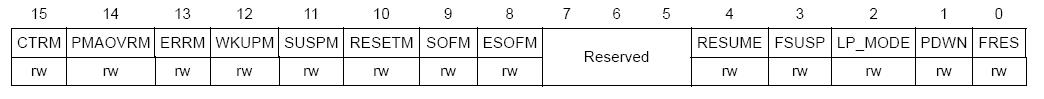

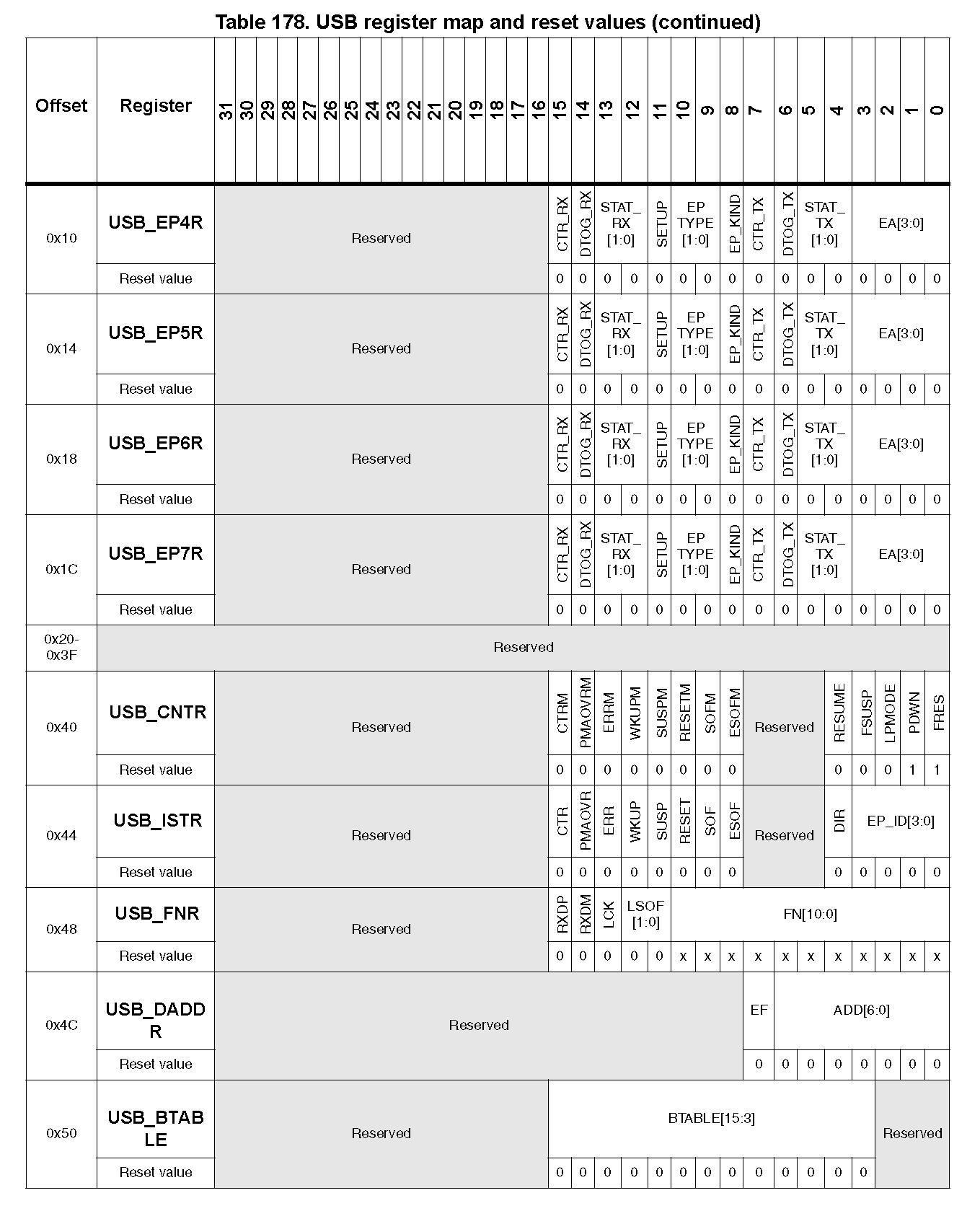

23.5.1 Common registers

USB control register (USB_CNTR)

Bit 15 CTRM: Correct transfer interrupt mask

0: Correct Transfer (CTR) Interrupt disabled.

1: CTR Interrupt enabled, an interrupt request is generated when the corresponding bit in the USB_ISTR register is set.

Bit 14 PMAOVRM: Packet memory area over / underrun interrupt mask

Bit 13 ERRM: Error interrupt mask

Bit 12 WKUPM: Wakeup interrupt mask

Bit 11 SUSPM: Suspend mode interrupt mask

Bit 10 RESETM: USB reset interrupt mask

Bit 9 SOFM: Start of frame interrupt mask

Bit 8 ESOFM: Expected start of frame interrupt mask

Bits 7:5 Reserved.

Bit 4 RESUME: Resume request

The microcontroller can set this bit to send a Resume signal to the host. It must be activated, according to USB specifications, for no less than 1 mS and no more than 15 mS after which the Host PC is ready to drive the resume sequence up to its end.

Bit 3 FSUSP: Force suspend

Software must set this bit when the SUSP interrupt is received, which is issued when no traffic is received by the USB peripheral for 3 mS.

0: No effect.

1: Enter suspend mode. Clocks and static power dissipation in the analog transceiver are left unaffected. If suspend power consumption is a requirement (bus-powered device), the application software should set the LP_MODE bit after FSUSP as explained below.

Bit 2 LP_MODE: Low-power mode

This mode is used when the suspend-mode power constraints require that all static power dissipation is avoided, except the one required to supply the external pull-up resistor. This condition should be entered when the application is ready to stop all system clocks, or reduce their frequency in order to meet the power consumption requirements of the USB suspend condition. The USB activity during the suspend mode (WKUP event) asynchronously resets this bit (it can also be reset by software).

0: No Low-power mode.

1: Enter Low-power mode

Bit 1 PDWN: Power down

This bit is used to completely switch off all USB-related analog parts if it is required to completely disable the USB peripheral for any reason. When this bit is set, the USB peripheral is disconnected from the transceivers and it cannot be used.

0: Exit Power Down.

1: Enter Power down mode.

Bit 0 FRES: Force USB Reset

0: Clear USB reset.

1: Force a reset of the USB peripheral, exactly like a RESET signalling on the USB. The USB peripheral is held in RESET state until software clears this bit. A “USB-RESET” interrupt is generated, if enabled.

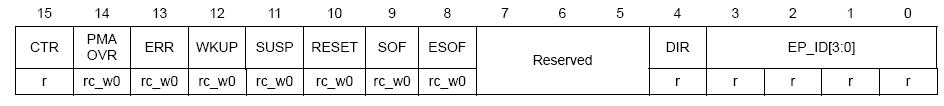

USB interrupt status register (USB_ISTR)

该寄存器包含了所有支持的中断状态,如果在USB_CNTR使能了相应的中断,当中断被触发时就会进入中断,通过查询该寄存器掩码确定是哪个中断。

每当Endpoint传输完成,硬件都会将CTR置位,如果相应的使能位在USB_CNTR被设置时,还会触发中断。

需要注意,写1不变,写0会清零;读的话也会清零。可以参考官方库的操作方式:

void USB_Istr(void) { wIstr = _GetISTR(); // 举一个例子 if (wIstr & ISTR_SOF & wInterrupt_Mask) { _SetISTR((uint16_t)CLR_SOF); bIntPackSOF++; SOF_Callback(); // 中断处理函数 } }

Bit 15 CTR: Correct transfer

This bit is set by the hardware to indicate that an endpoint has successfully completed a transaction; using DIR and EP_ID bits software can determine which endpoint requested the interrupt. This bit is read-only.

Bit 14 PMAOVR: Packet memory area over / underrun

如果微控制器未能及时响应USB内存请求,则设置此位。

USB外围设备以下列方式处理此事件:没有发送握手数据包,在传输期间,传输流上会强制出现一个比特错误;在这两种情况下,主机都会重试事务。PMAOVR中断不应发生在正常操作中。由于失败的事务由主机重试,应用程序软件有机会在此中断处理期间加速设备操作,以便为下一次事务重试做好准备;然而,在此情况下,这种情况不会在等时传输(无论如何都不会重新尝试等时事务)期间发生,从而导致数据丢失。这个位是读/写的,但是只有‘0’可以写,而写‘1’没有任何效果。

Bit 13 ERR: Error

This flag is set whenever one of the errors listed below has occurred:

NANS: 没有回答。主机响应的超时已过期。

CRC: 循环冗余校验错误。无论是在令牌上还是在数据中,接收到的一个CRCs是错误的。

BST: Bit Stuffing error.位填充错误。 在PID、数据和/或CRC中的任何位置都检测到位填充错误。

FVIO: Framing format Violation. 帧格式冲突。接收到一个非标准帧(EOP不在正确的位置,错误的令牌序列等)。

USB软件通常可以忽略错误,因为USB外围设备和PC主机以完全透明的方式管理错误的重传。此中断在软件开发阶段非常有用,也可用于监视传输的质量。USB总线将可能出现的问题(如连接器松动、环境噪音过大、USB电缆中导体断裂等)通知用户。

Bit 12 WKUP: Wakeup

当在挂起模式下检测到唤醒USB外围设备的活动时,硬件将此位设置为1。此事件异步清除ctlr寄存器中的lp_mode位并激活usb_wakeup line,该行可用于通知设备的其余部分(例如唤醒单元)恢复进程的启动。这个位是读/写的,但是只有‘0’可以写,而写‘1’没有任何效果。

Bit 11 SUSP: Suspend mode request 挂起模式请求

当3MS没有接收到流量时,该位由硬件设置,指示来自USB总线的暂停模式请求。在任何USB重置之后立即启用挂起条件检查,当挂起模式处于活动状态(FSUSP=1)时,硬件会禁用它,直到恢复序列结束。

Bit 10 RESET: USB reset request

当USB外围设备在其输入端检测到活动USB复位信号时设置。USB外围设备响应重置,只是重置其内部协议状态机,如果在USB_CNTR寄存器中设置RESETM启用位,则生成中断。接收和传输被禁用,直到重置位被清除。所有配置寄存器都不重置:微控制器必须显式清除这些寄存器(这是为了确保重置中断能够安全地传递,并且紧接重置后的任何事务都可以完成)。功能地址和端点寄存器由USB重置事件重置。

Bit 9 SOF: Start of frame

此位指示一个新的USB帧的开始,它是在SOF数据包通过USB总线到达时设置的。中断服务例程可以监视SOF事件,使其具有到USB主机的1 ms同步事件,并安全地读取在SOF数据包接收处更新的 USB_FNR 寄存器(这可能对等时应用有用)。

Bit 8 ESOF: Expected start of frame

该比特由硬件设置,当期望SOF包未接收时。主机每毫秒都会发送的SOF包,但如果集线器没有正确接收,则暂停计时器发出此中断。如果产生三个连续ESOF中断(即三个SOF分组丢失),而在其间不发生任何业务,则产生SUMP中断。即使丢失的SOF包在挂起计时器尚未锁定时发生,此位也被设置。

Bit 4 DIR: Direction of transaction

该位由硬件根据成功事务的方向编写,从而产生中断请求。

如果DIR位=0,则在与中断端点相关的USB_EPnR寄存器中设置CTR_TX位。中断事务为IN类型(由USB外围设备向主机PC传输的数据)。

如果DIR位=1,则在USB_EPnR寄存器中设置CTR_RX位或同时设置CTR_TX/CTR_RX。与中断端点相关。中断事务是OUT类型的(USB外围设备从主机PC接收的数据)或两个待处理的事务。

应用软件可以使用此信息访问与触发事务相关的USB_EPnR位,因为它表示中断挂起的方向。这个位是只读的。

Bits 3:0 EP_ID[3:0]: Endpoint Identifier

这些位是由硬件根据端点号编写的,从而产生中断请求。

如果有几个端点事务挂起,硬件将写入与具有最高优先级的端点相关的端点标识符,其定义方式如下:

两个端点集按优先级顺序定义:首先考虑等时和双缓冲的批量端点,然后检查其他端点。

如果来自同一组的多个端点请求中断,则根据最低请求端点寄存器分配USB_ISTR寄存器中的EP_ID位,具有最高优先级的EP0R,其次是EP1R等等。应用软件可以根据该优先级方案向每个端点分配寄存器,以便以适当的方式对并发端点请求进行排序。这些位元是只读的。

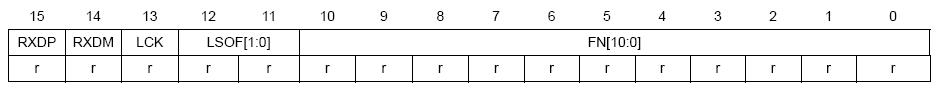

USB frame number register (USB_FNR)

Bit 15 RXDP: Receive data + line status

该位可以用来观察接收数据(+)上行端口数据线的状态。它可以用于终止挂起例程,以帮助确定唤醒事件。

Bit 14 RXDM: Receive data - line status

此位可用于观察接收数据(-)上游端口数据线的状态。它可以用于终止挂起例程,以帮助确定唤醒事件。

Bit 13 LCK: Locked

当在usb重置条件结束后或在usb恢复序列结束后接收到至少两个连续的sof分组时,该位由硬件设置。一旦锁定,帧计时器将保持此状态,直到USB重置或USB暂停事件发生。

Bits 12:11 LSOF[1:0]: Lost SOF

当产生ESOF中断时,这些位是由硬件编写的,计算连续SOF数据包丢失的数量。在接收SOF分组时,清除这些比特。

Bits 10:0 FN[10:0]: Frame number

此位字段包含上次接收的SOF数据包中包含的11位帧号。对于主机发送的每一个帧,帧号都是递增的,并且对于等时传输非常有用。在生成SOF中断时更新此位字段。

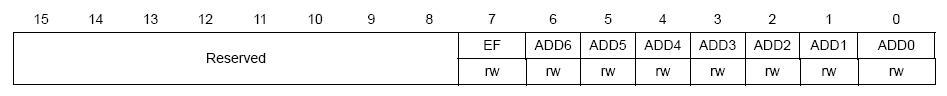

USB device address (USB_DADDR)

Bits 15:8 Reserved

Bit 7 EF: Enable function

此位由软件设置,以启用USB设备。此设备的地址包含在以下[6:0]位中。如果此位为‘0,则不处理任何事务,而不管USB_EPnR寄存器的设置如何。

Bits 6:0 ADD[6:0]: Device address

这些位包含在枚举过程中由主机PC分配的USB功能地址。关联的 USB_EPnR 寄存器中的这个字段和端点地址(EA)字段必须与USB令牌中包含的信息相匹配,以便处理到所需端点的事务。

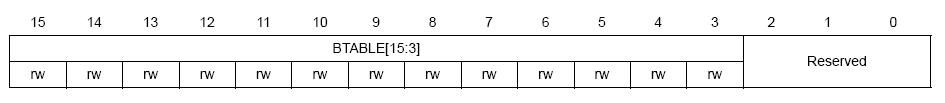

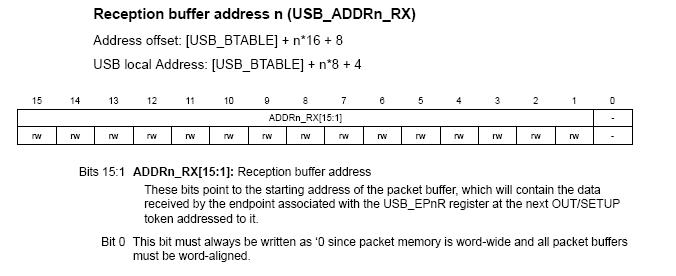

Buffer table address (USB_BTABLE)

Bits 15:3 BTABLE[15:3]: Buffer table

这些位在专用分组存储器中包含缓冲器分配表的起始地址。这个表描述了每个端点缓冲区的位置和大小,并且它必须对齐到一个8字节的边界(3个最不重要的位总是‘0’)。在发送到该设备的每个事务开始时,USP外围设备读取此表中与已寻址端点相关的元素,以获取其缓冲区启动位置和缓冲区大小。

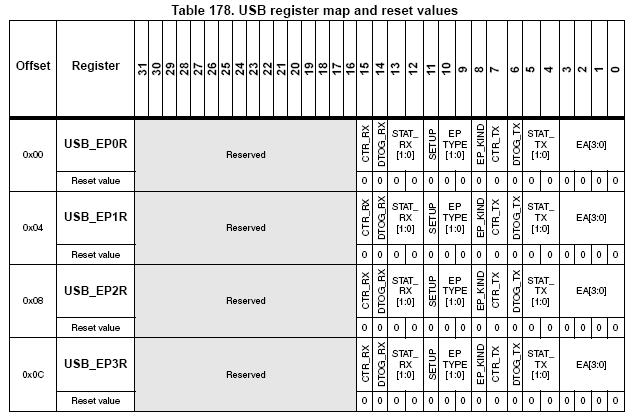

23.5.2 Endpoint-specific registers

这些寄存器的数量取决于USB外围设备要处理的端点数。USB外围设备支持多达8个双向端点。每个USB设备必须支持一个控制端点,其地址(EA位)必须设置为0。如果启用具有相同端点号值的多个端点,则USB外围设备以未定义的方式工作。对于每个端点,可以使用一个USB_EPnR寄存器来存储端点特定的信息。

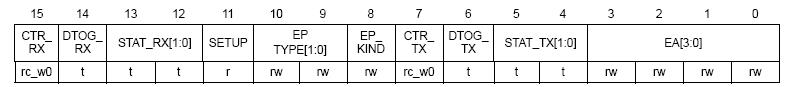

USB endpoint n register (USB_EPnR), n=[0..7]

当从USB总线接收到USB重置或强制通过ctlr寄存器中的位FRES时,它们也会被重置,这两个比特(CTR_RX和CTR_TX位除外)保持不变,以避免丢失正确的数据包通知,紧接着是USB重置事件。每个端点都有它的USB_EPnR寄存器,其中n是端点标识符。

应该避免这些寄存器上的读-修改-写周期,因为在读操作和写操作之间,硬件可以设置一些位,下一次写将在CPU有时间检测更改之前修改它们。为此,所有受此问题影响的位都具有一个“不变”值,在不需要修改时必须使用该值。建议使用LOAD指令修改这些寄存器,其中只能由硬件修改的所有位元都是用它们的“不变”值编写的。

Bit 15 CTR_RX: Correct Transfer for reception

当在此端点上成功完成Out/Setup事务时,硬件将设置此位;软件只能清除此位。如果相应地设置了USB_CNTR寄存器中的CTRM位,则会生成一个通用中断条件以及始终被激活的与端点相关的中断条件。发生的事务的类型,Out或Setup,可以从下面描述的安装位中确定。以NAK或延迟握手结束的事务不会设置此位,因为没有实际传输数据,例如协议错误或数据切换不匹配。This bit is read/write but only ‘0 can be written, writing 1 has no effect.

Bit 14 DTOG_RX: Data Toggle, for reception transfers

如果端点不是同步性的,则此位包含要接收的下一个数据包的数据切换位(0=DATA 0,1=data 1)的期望值。当ACK握手发送到USB主机时,硬件切换此位,跟踪具有匹配数据PID值的数据包接收;如果端点被定义为控制端点,则硬件在接收发送到该端点的设置PID时清除此位。

如果端点使用双缓冲功能,则此位也用于支持数据包缓冲区交换(参见23.4.3节:双缓冲端点)。

如果端点是等时的,则此位仅用于支持数据包缓冲区交换,因为此类端点不使用数据切换,只传输DATA 0数据包(参见23.4.4节:等时传输)。硬件在数据包接收结束后切换此位,因为没有用于等时传输的握手。

软件还可以切换此位,以初始化其值(在端点不是控制端点时强制),或强制特定数据切换/数据包缓冲区使用。当应用软件写0时,DTOG_RX的值保持不变,而写入‘1使位值切换。这个位是读/写的,但只能通过写1来切换。

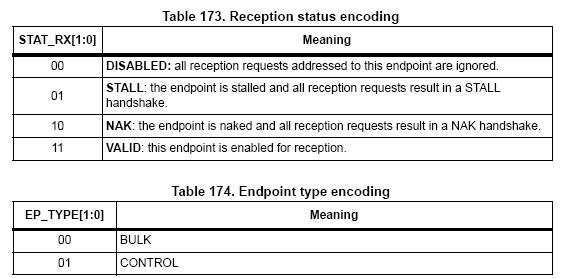

Bits 13:12 STAT_RX [1:0]: Status bits, for reception transfers

这些位包含关于端点状态的信息,这些信息在表173中列出:第638页中的接收状态编码。这些位可以被软件切换以初始化它们的值。当应用软件写入‘0’时,值保持不变,而写入‘1’则使位值切换。当正确的传输发生(CTR_RX=1)时,硬件将STAT_RX位设置为NAK,对应于发送到此端点的OUT或设置(仅限控制)事务,因此软件有时间在确认一个新的事务双缓冲大容量端点之前详细说明接收的数据,实现一个特殊的事务流控制,该控制基于缓冲区可用性条件控制状态(参见23.4.3节:双缓冲端点)。如果端点定义为等时,则其状态只能是“有效”或“禁用”,因此硬件无法在成功的事务处理后更改端点的状态。如果软件将等时端点的STAT_RX位设置为“Start”或“NAK”,则不定义USB外围行为。这些位元是读/写的,但是它们只能通过写1来切换。

Bit 11 SETUP: Setup transaction completed

这个位是只读的,当最后一个完成的事务是一个设置时,它是由硬件设置的。此位仅对控件端点更改其值。对于成功的接收事务(CTR_RX事件),必须对其进行检查,以确定发生的事务类型。为了保护中断服务例程不受由于下一个传入令牌造成的设置位的更改,此位被冻结,而CTR_RX位于1;当CTR_RX位于0时,它的状态发生变化。这个位是只读的。

Bits 10:9 EP_TYPE[1:0]: Endpoint type

这些位配置此端点的行为,如表174所述:页面638中的端点类型编码。端点0必须始终是一个控制端点,并且每个USB函数必须至少有一个地址为0的控制端点,但如果需要,可能还有其他的控制端点。只有控件端点处理安装事务,而其他类型的端点则忽略这些事务。安装事务不能用NAK或STACK来回答。如果将控制端点定义为NAK,则当接收到安装事务时,USB外围设备将不会在接收方向上响应,模拟接收错误。如果控制端点被定义为接收方向上的阻塞,那么设置数据包无论如何都会被接受,传输数据和发出CTR中断。Out事务的接收是以正常的方式处理的,即使端点是一个控制端点也是如此。大容量端点和中断端点具有非常相似的行为,它们仅在使用EP_CORT配置位的特殊特性上有所不同。The usage of Isochronous endpoints is explained in Section 23.4.4: Isochronous transfers

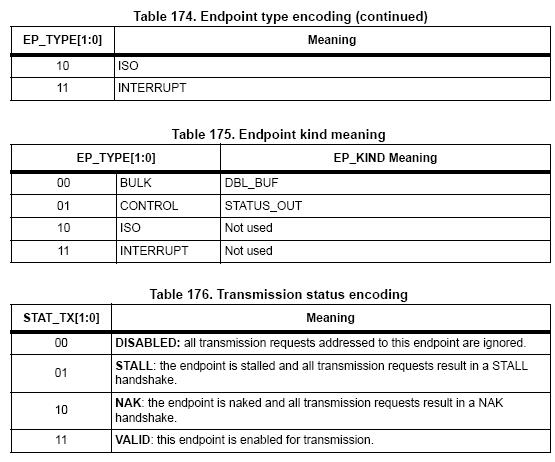

Bit 8 EP_KIND: Endpoint kind

The meaning of this bit depends on the endpoint type configured by the EP_TYPE bits.

Table 175 summarizes the different meanings.

DBL_BUF: This bit is set by the software to enable the double-buffering feature for this bulk

endpoint. The usage of double-buffered bulk endpoints is explained in Section 23.4.3:

Double-buffered endpoints.

STATUS_OUT: This bit is set by the software to indicate that a status out transaction is

expected: in this case all OUT transactions containing more than zero data bytes are

answered ‘STALL’ instead of ‘ACK’. This bit may be used to improve the robustness of the

application to protocol errors during control transfers and its usage is intended for control

endpoints only. When STATUS_OUT is reset, OUT transactions can have any number of

bytes, as required.

Bit 7 CTR_TX: Correct Transfer for transmission

This bit is set by the hardware when an IN transaction is successfully completed on this

endpoint; the software can only clear this bit. If the CTRM bit in the USB_CNTR register is

set accordingly, a generic interrupt condition is generated together with the endpoint related

interrupt condition, which is always activated.

A transaction ended with a NAK or STALL handshake does not set this bit, since no data is

actually transferred, as in the case of protocol errors or data toggle mismatches.

This bit is read/write but only ‘0 can be written.

Bit 6 DTOG_TX: Data Toggle, for transmission transfers

If the endpoint is non-isochronous, this bit contains the required value of the data toggle bit

(0=DATA0, 1=DATA1) for the next data packet to be transmitted. Hardware toggles this bit

when the ACK handshake is received from the USB host, following a data packet

transmission. If the endpoint is defined as a control one, hardware sets this bit to 1 at the

reception of a SETUP PID addressed to this endpoint.

If the endpoint is using the double buffer feature, this bit is used to support packet buffer

swapping too (Refer to Section 23.4.3: Double-buffered endpoints)

If the endpoint is Isochronous, this bit is used to support packet buffer swapping since no

data toggling is used for this sort of endpoints and only DATA0 packet are transmitted (Refer

to Section 23.4.4: Isochronous transfers). Hardware toggles this bit just after the end of data

packet transmission, since no handshake is used for Isochronous transfers.

This bit can also be toggled by the software to initialize its value (mandatory when the

endpoint is not a control one) or to force a specific data toggle/packet buffer usage. When

the application software writes ‘0, the value of DTOG_TX remains unchanged, while writing

‘1 makes the bit value toggle. This bit is read/write but it can only be toggled by writing 1.

Bits 5:4 STAT_TX [1:0]: Status bits, for transmission transfers

These bits contain the information about the endpoint status, listed in Table 176. These bits

can be toggled by the software to initialize their value. When the application software writes

‘0, the value remains unchanged, while writing ‘1 makes the bit value toggle. Hardware sets

the STAT_TX bits to NAK, when a correct transfer has occurred (CTR_TX=1) corresponding

to a IN or SETUP (control only) transaction addressed to this endpoint. It then waits for the

software to prepare the next set of data to be transmitted.

Double-buffered bulk endpoints implement a special transaction flow control, which controls

the status based on buffer availability condition (Refer to Section 23.4.3: Double-buffered

endpoints).

If the endpoint is defined as Isochronous, its status can only be “VALID” or “DISABLED”.

Therefore, the hardware cannot change the status of the endpoint after a successful

transaction. If the software sets the STAT_TX bits to ‘STALL’ or ‘NAK’ for an Isochronous

endpoint, the USB peripheral behavior is not defined. These bits are read/write but they can

be only toggled by writing ‘1.

Bits 3:0 EA[3:0]: Endpoint address

Software must write in this field the 4-bit address used to identify the transactions directed to

this endpoint. A value must be written before enabling the corresponding endpoint.

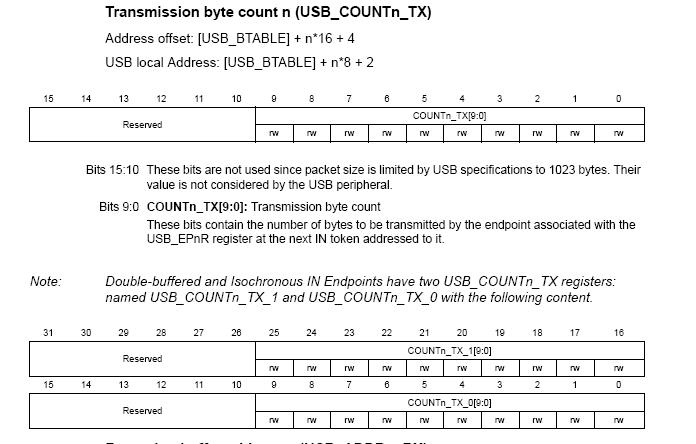

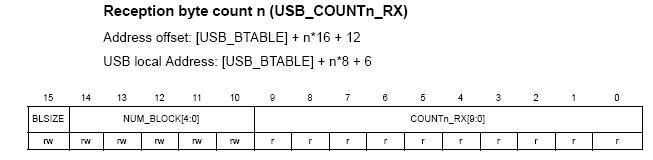

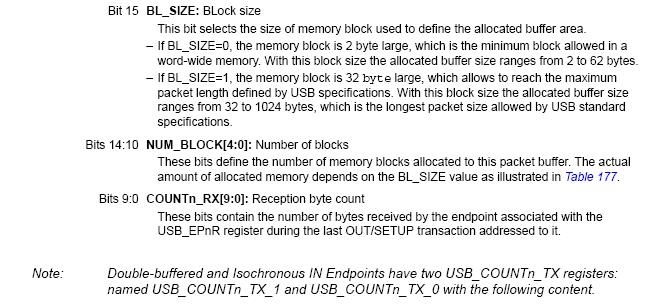

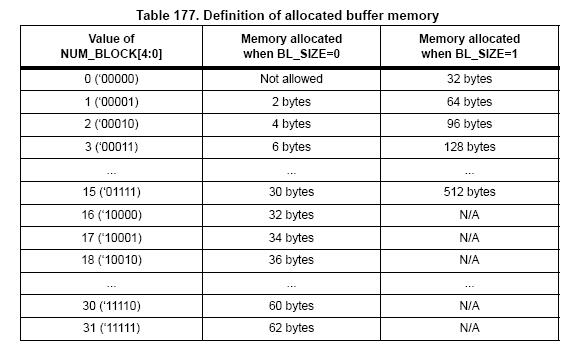

此表位置用于存储两个不同的值,这两个值都是在数据包接收期间所需的。最重要的位包含分配缓冲区大小的定义,以允许缓冲区溢出检测,而该位置的最小重要部分由USB外围设备在接收结束时写回,以给出接收到的字节的实际数量。由于对可用位数的限制,缓冲区大小使用分配的内存块数表示,其中可以选择块大小来选择细粒度/小缓冲区和粗粒度/大缓冲区之间的折衷。分配缓冲区的大小是端点描述符的一部分,它通常是根据其maxPacketSize参数值在枚举过程中定义的(参见“通用串行总线规范”)。

23.5.4 USB register map

以上是关于USB的主要内容,如果未能解决你的问题,请参考以下文章