系统时钟和定时器

Posted 游戏进行中

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了系统时钟和定时器相关的知识,希望对你有一定的参考价值。

15.1 介绍

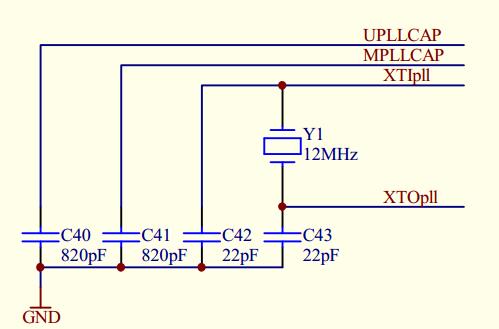

CPU 的时钟控制逻辑既可以外接晶振,然后通过内部电路产生时钟源;也可以直接使用外部提供的时钟源,它们通过引脚的设置来选择。S3C2440A有两个锁相环,(MPLL)一个用于FCLK、PCLK和HCLK,(UPLL)另一个用于USB模块(48MHZ)。时钟控制逻辑给整个芯片提供三种时钟:

- FCLK:用于CPU 核

- HCLK:用于 AHB 总线上设备,比如CPU核、存储器控制器、中断控制器、LCD控制器、DMA 和 USB 主机模块等

- PCLK:用于 APB 总线上的设备,比如 WATCHDOG、IIS、IIC、PWM 定时器、MMC 接口、ADC、UART、GPIO、RTC 和 SPI

AHB(Advanced High performance Bus)总线主要用于高性能模块(比如CPU、DMA 和 DSP 等)之间的连接;APB(Advanced Peripheral Bus)总线主要用于低带宽的周边外设之间的连接,比如 UART、IIC 等

MPLL在1.3V电压的情况下,产生的最大时钟为 400 MHZ,UPLL 固定产生 48 MHZ 的时钟供 USB 使用

JZ2440 的时钟电路图如下:

15.1.1 MPLL 设置

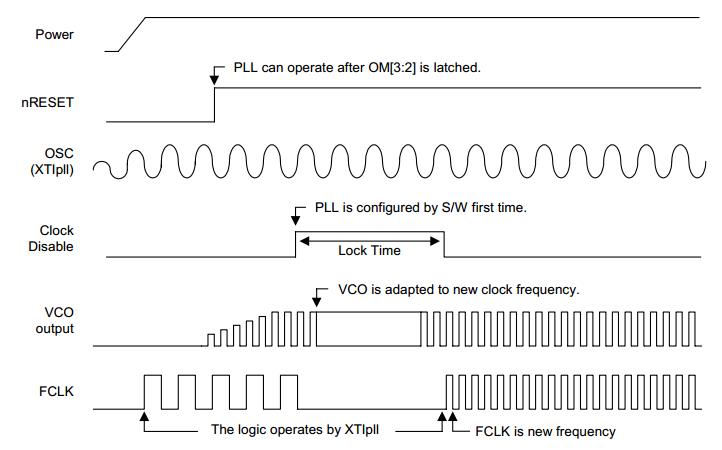

上电时,PLL 没有被启动,FCLK 为外部时钟源,JZ2440的外部时钟源为12MHZ,称为 Fin。可以通过软件来启用 PLL,提高系统时钟。

- 上电几毫秒后,晶振输出稳定,FCLK = Fin(晶振频率),nRESET 信号回复高电平后,CPU开始执行指令

- 可以在程序开头启动 MPLL,设置 MPLL 的几个寄存器后,需要等待一段时间(Lock Time),MPLL 的输出才稳定。在此时间内,FCLK 停振,CPU停止工作。Lock Time 的长短由寄存器 LOCKTIME 设定

- Lock Time 后,MPLL 输出正常,CPU 工作在新的 FCLK 下。(FCLK、HCLK和PCLK 的比例可以通过寄存器来设置)

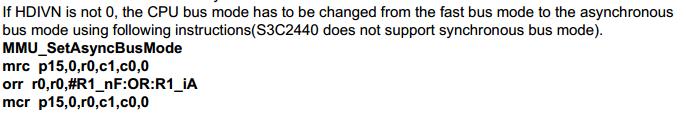

要注意的是,如果 CLKDIVN 寄存器中的 HDIVN 非0,则需要将 CPU 的总线模式从 “fast bus mode” 变为"asynchronous bus

mode"

15.2 PWM 定时器

S3C2440 共有 5个 16 位的定时器。其中0、1、2、3由 PWM(Pulse Width Modulation)功能,即它们都由一个输出引脚,可以通过定时器来控制引脚周期性的高、低电平变化;定时器 4 只有一个内部定时器,没有输出引脚。定时器 0 有一个死区发生器,可以用于大电流设备上。

定时器部件的时钟源称为 PCLK,首先通过两个 8 位的预分频器降低频率:定时器0、1共用第一个预分频器,定时器2、3、4共用第二个预分频器。预分频器的输出将进入第二级分频器,它们输出5种频率的时钟:2分频、4分频、8分频、16分频或者外部时钟(TCLK0/TCLK1)。每个定时器的工作时钟可以从这 5 种频率种选择。

这个8位预分频器是可编程的,根据负载值分割存储在 TCFG0 和 TCFG1 寄存器 PCLK。

具体可以看 S3C2440 芯片手册的第10章

定时器的控制流程如下:

- 程序初始,设定 TCMPBn、TCNTBn 两个寄存器,这两个寄存器是设定定时器n 的比较值、初始计数值

- 随后设置 TCON 寄存器启动定时器 n,这时 TCMPBn、TCNTBn 的值将被装入其内部寄存器 TCMPn、TCNTn 中。在定时器 n 的工作频率下,TCNTn 开始减 1 计数,其值可以通过读取 TCNTOn 寄存器得知

- 当 TCNTn 的值等于 TCMPn 的值时,定时器 n 的输出管脚 TOUTn 反转;TCNTn 继续减 1 计数

- 当 TCNTn 的值到达 0 时,其输出管脚 TOUTn 再次反转,并触发定时器 n 的中断(中断必须使能才会中断)

- 当 TCNTn 的值到达 0 时,如果在 TCON 寄存器中将定时器 n 设为 “自动加载”,则 TCMPB0 和 TCNTB0 寄存器的值被自动转入 TCMP0 和 TCNT0 寄存器中,下一个计数流程开始

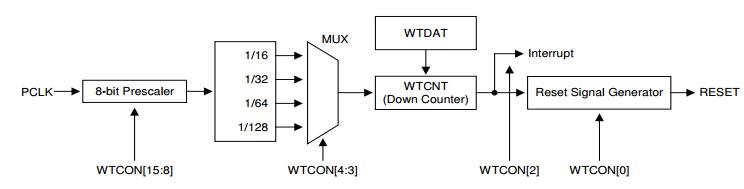

15.1.3 看门狗

看门狗定时器可以像一般 16 位定时器一样用于产生周期性的中断,也可以用于发出复位信号以重启失常的系统。与 PWM 结构类似。

使用 看门狗定时器的 “WATCHDOG 功能”时,在正常的程序中,必须不断重新设置 WTCNT 寄存器使得它不为0,这样可以保证系统不被重启,这称为“喂狗”;当程序崩溃时不能正常“喂狗”,计数值达到 0 后系统将被重启,这样程序将重新运行。

看门狗定时器的寄存器看芯片手册

15.2 代码

timer.lds

1 SECTIONS { 2 . = 0x30000000; //程序运行地址为 0x30000000 3 .text : { *(.text) } //定义代码段 4 .rodata ALIGN(4) : {*(.rodata)} //定义只读数据段 5 .data ALIGN(4) : { *(.data) } //定义数据段 6 .bss ALIGN(4) : { *(.bss) *(COMMON) } //清除代码 7 }

s3c24xx.h

1 /* WOTCH DOG register */ 2 #define WTCON (*(volatile unsigned long *)0x53000000) 3 4 /* SDRAM regisers */ 5 #define MEM_CTL_BASE 0x48000000 6 #define SDRAM_BASE 0x30000000 7 8 /* NAND Flash registers */ 9 #define NFCONF (*(volatile unsigned int *)0x4e000000) 10 #define NFCMD (*(volatile unsigned char *)0x4e000004) 11 #define NFADDR (*(volatile unsigned char *)0x4e000008) 12 #define NFDATA (*(volatile unsigned char *)0x4e00000c) 13 #define NFSTAT (*(volatile unsigned char *)0x4e000010) 14 15 /*GPIO registers*/ 16 #define GPBCON (*(volatile unsigned long *)0x56000010) 17 #define GPBDAT (*(volatile unsigned long *)0x56000014) 18 19 #define GPFCON (*(volatile unsigned long *)0x56000050) 20 #define GPFDAT (*(volatile unsigned long *)0x56000054) 21 #define GPFUP (*(volatile unsigned long *)0x56000058) 22 23 #define GPGCON (*(volatile unsigned long *)0x56000060) 24 #define GPGDAT (*(volatile unsigned long *)0x56000064) 25 #define GPGUP (*(volatile unsigned long *)0x56000068) 26 27 #define GPHCON (*(volatile unsigned long *)0x56000070) 28 #define GPHDAT (*(volatile unsigned long *)0x56000074) 29 #define GPHUP (*(volatile unsigned long *)0x56000078) 30 31 32 33 /*UART registers*/ 34 #define ULCON0 (*(volatile unsigned long *)0x50000000) 35 #define UCON0 (*(volatile unsigned long *)0x50000004) 36 #define UFCON0 (*(volatile unsigned long *)0x50000008) 37 #define UMCON0 (*(volatile unsigned long *)0x5000000c) 38 #define UTRSTAT0 (*(volatile unsigned long *)0x50000010) 39 #define UTXH0 (*(volatile unsigned char *)0x50000020) 40 #define URXH0 (*(volatile unsigned char *)0x50000024) 41 #define UBRDIV0 (*(volatile unsigned long *)0x50000028) 42 43 44 /*interrupt registes*/ 45 #define SRCPND (*(volatile unsigned long *)0x4A000000) 46 #define INTMOD (*(volatile unsigned long *)0x4A000004) 47 #define INTMSK (*(volatile unsigned long *)0x4A000008) 48 #define PRIORITY (*(volatile unsigned long *)0x4A00000c) 49 #define INTPND (*(volatile unsigned long *)0x4A000010) 50 #define INTOFFSET (*(volatile unsigned long *)0x4A000014) 51 #define SUBSRCPND (*(volatile unsigned long *)0x4A000018) 52 #define INTSUBMSK (*(volatile unsigned long *)0x4A00001c) 53 54 /*external interrupt registers*/ 55 #define EINTMASK (*(volatile unsigned long *)0x560000a4) 56 #define EINTPEND (*(volatile unsigned long *)0x560000a8) 57 58 /*clock registers*/ 59 #define LOCKTIME (*(volatile unsigned long *)0x4c000000) 60 #define MPLLCON (*(volatile unsigned long *)0x4c000004) 61 #define UPLLCON (*(volatile unsigned long *)0x4c000008) 62 #define CLKCON (*(volatile unsigned long *)0x4c00000c) 63 #define CLKSLOW (*(volatile unsigned long *)0x4c000010) 64 #define CLKDIVN (*(volatile unsigned long *)0x4c000014) 65 66 67 /*PWM & Timer registers*/ 68 #define TCFG0 (*(volatile unsigned long *)0x51000000) 69 #define TCFG1 (*(volatile unsigned long *)0x51000004) 70 #define TCON (*(volatile unsigned long *)0x51000008) 71 #define TCNTB0 (*(volatile unsigned long *)0x5100000c) 72 #define TCMPB0 (*(volatile unsigned long *)0x51000010) 73 #define TCNTO0 (*(volatile unsigned long *)0x51000014) 74 75 #define GSTATUS1 (*(volatile unsigned long *)0x560000B0)

head.S

1 @****************************************************************************** 2 @ File:head.S 3 @ 功能:初始化,设置中断模式、系统模式的栈,设置好中断处理函数 4 @****************************************************************************** 5 6 .extern main 7 .text 8 .global _start 9 _start: 10 @****************************************************************************** 11 @ 中断向量,本程序中,除Reset和HandleIRQ外,其它异常都没有使用 12 @****************************************************************************** 13 b Reset 14 15 @ 0x04: 未定义指令中止模式的向量地址 16 HandleUndef: 17 b HandleUndef 18 19 @ 0x08: 管理模式的向量地址,通过SWI指令进入此模式 20 HandleSWI: 21 b HandleSWI 22 23 @ 0x0c: 指令预取终止导致的异常的向量地址 24 HandlePrefetchAbort: 25 b HandlePrefetchAbort 26 27 @ 0x10: 数据访问终止导致的异常的向量地址 28 HandleDataAbort: 29 b HandleDataAbort 30 31 @ 0x14: 保留 32 HandleNotUsed: 33 b HandleNotUsed 34 35 @ 0x18: 中断模式的向量地址 36 b HandleIRQ 37 38 @ 0x1c: 快中断模式的向量地址 39 HandleFIQ: 40 b HandleFIQ 41 42 Reset: 43 ldr sp, =4096 @ 设置栈指针,以下都是C函数,调用前需要设好栈 44 bl disable_watch_dog @ 关闭WATCHDOG,否则CPU会不断重启 45 bl clock_init @ 设置MPLL,改变FCLK、HCLK、PCLK 46 bl memsetup @ 设置存储控制器以使用SDRAM 47 bl copy_steppingstone_to_sdram @ 复制代码到SDRAM中 48 ldr pc, =on_sdram @ 跳到SDRAM中继续执行 49 on_sdram: 50 msr cpsr_c, #0xd2 @ 进入中断模式 51 ldr sp, =4096 @ 设置中断模式栈指针 52 53 msr cpsr_c, #0xdf @ 进入系统模式 54 ldr sp, =0x34000000 @ 设置系统模式栈指针, 55 56 bl init_led @ 初始化LED的GPIO管脚 57 bl timer0_init @ 初始化定时器0 58 bl init_irq @ 调用中断初始化函数,在init.c中 59 msr cpsr_c, #0x5f @ 设置I-bit=0,开IRQ中断 60 61 ldr lr, =halt_loop @ 设置返回地址 62 ldr pc, =main @ 调用main函数 63 halt_loop: 64 b halt_loop 65 66 HandleIRQ: 67 sub lr, lr, #4 @ 计算返回地址 68 stmdb sp!, { r0-r12,lr } @ 保存使用到的寄存器 69 @ 注意,此时的sp是中断模式的sp 70 @ 初始值是上面设置的4096 71 72 ldr lr, =int_return @ 设置调用ISR即EINT_Handle函数后的返回地址 73 ldr pc, =Timer0_Handle @ 调用中断服务函数,在interrupt.c中 74 int_return: 75 ldmia sp!, { r0-r12,pc }^ @ 中断返回, ^表示将spsr的值复制到cpsr

init.c

1 /* 2 * init.c: 进行一些初始化 3 */ 4 5 #include "s3c24xx.h" 6 7 void disable_watch_dog(void); 8 void clock_init(void); 9 void memsetup(void); 10 void copy_steppingstone_to_sdram(void); 11 void init_led(void); 12 void timer0_init(void); 13 void init_irq(void); 14 15 /* 16 * 关闭WATCHDOG,否则CPU会不断重启 17 */ 18 void disable_watch_dog(void) 19 { 20 WTCON = 0; // 关闭WATCHDOG很简单,往这个寄存器写0即可 21 } 22 23 #define S3C2410_MPLL_200MHZ ((0x5c<<12)|(0x04<<4)|(0x00)) 24 #define S3C2440_MPLL_200MHZ ((0x5c<<12)|(0x01<<4)|(0x02)) 25 /* 26 * 对于MPLLCON寄存器,[19:12]为MDIV,[9:4]为PDIV,[1:0]为SDIV 27 * 有如下计算公式: 28 * S3C2410: MPLL(FCLK) = (m * Fin)/(p * 2^s) 29 * S3C2410: MPLL(FCLK) = (2 * m * Fin)/(p * 2^s) 30 * 其中: m = MDIV + 8, p = PDIV + 2, s = SDIV 31 * 对于本开发板,Fin = 12MHz 32 * 设置CLKDIVN,令分频比为:FCLK:HCLK:PCLK=1:2:4, 33 * FCLK=200MHz,HCLK=100MHz,PCLK=50MHz 34 */ 35 void clock_init(void) 36 { 37 // LOCKTIME = 0x00ffffff; // 使用默认值即可 38 CLKDIVN = 0x03; // FCLK:HCLK:PCLK=1:2:4, HDIVN=1,PDIVN=1 39 40 /* 如果HDIVN非0,CPU的总线模式应该从“fast bus mode”变为“asynchronous bus mode” */ 41 __asm__( 42 "mrc p15, 0, r1, c1, c0, 0\\n" /* 读出控制寄存器 */ 43 "orr r1, r1, #0xc0000000\\n" /* 设置为“asynchronous bus mode” */ 44 "mcr p15, 0, r1, c1, c0, 0\\n" /* 写入控制寄存器 */ 45 ); 46 47 /* 判断是S3C2410还是S3C2440 */ 48 if ((GSTATUS1 == 0x32410000) || (GSTATUS1 == 0x32410002)) 49 { 50 MPLLCON = S3C2410_MPLL_200MHZ; /* 现在,FCLK=200MHz,HCLK=100MHz,PCLK=50MHz */ 51 } 52 else 53 { 54 MPLLCON = S3C2440_MPLL_200MHZ; /* 现在,FCLK=200MHz,HCLK=100MHz,PCLK=50MHz */ 55 } 56 } 57 58 /* 59 * 设置存储控制器以使用SDRAM 60 */ 61 void memsetup(void) 62 { 63 volatile unsigned long *p = (volatile unsigned long *)MEM_CTL_BASE; 64 65 /* 这个函数之所以这样赋值,而不是像前面的实验(比如mmu实验)那样将配置值 66 * 写在数组中,是因为要生成”位置无关的代码”,使得这个函数可以在被复制到 67 * SDRAM之前就可以在steppingstone中运行 68 */ 69 /* 存储控制器13个寄存器的值 */ 70 p[0] = 0x22011110; //BWSCON 71 p[1] = 0x00000700; //BANKCON0 72 p[2] = 0x00000700; //BANKCON1 73 p[3] = 0x00000700; //BANKCON2 74 p[4] = 0x00000700; //BANKCON3 75 p[5] = 0x00000700; //BANKCON4 76 p[6] = 0x00000700; //BANKCON5 77 p[7] = 0x00018005; //BANKCON6 78 p[8] = 0x00018005; //BANKCON7 79 80 /* REFRESH, 81 * HCLK=12MHz: 0x008C07A3, 82 * HCLK=100MHz: 0x008C04F4 83 */ 84 p[9] = 0x008C04F4; 85 p[10] = 0x000000B1; //BANKSIZE 86 p[11] = 0x00000030; //MRSRB6 87 p[12] = 0x00000030; //MRSRB7 88 } 89 90 void copy_steppingstone_to_sdram(void) 91 { 92 unsigned int *pdwSrc = (unsigned int *)0; 93 unsigned int *pdwDest = (unsigned int *)0x30000000; 94 95 while (pdwSrc < (unsigned int *)4096) 96 { 97 *pdwDest = *pdwSrc; 98 pdwDest++; 99 pdwSrc++; 100 } 101 } 102 103 /* 104 * LED1-4对应GPB5、GPB6、GPB7、GPB8 105 */ 106 #define GPB5_out (1<<(5*2)) // LED1 107 #define GPB6_out (1<<(6*2)) // LED2 108 #define GPB7_out (1<<(7*2)) // LED3 109 #define GPB8_out (1<<(8*2)) // LED4 110 111 #define GPFCON (*(volatile unsigned long *)0x56000050) 112 113 #define GPF4_out (1<<(4*2)) 114 #define GPF5_out (1<<(5*2)) 115 #define GPF6_out (1<<(6*2)) 116 117 118 /* 119 * K1-K4对应GPG11、GPG3、GPF2、GPF3 120 */ 121 #define GPG11_eint (2<<(11*2)) // K1,EINT19 122 #define GPG3_eint (2<<(3*2)) // K2,EINT11 123 #define GPF3_eint (2<<(3*2)) // K3,EINT3 124 #define GPF2_eint (2<<(2*2)) // K4,EINT2 125 126 void init_led(void) 127 { 128 GPFCON = GPF4_out|GPF5_out|GPF6_out; // 将LED1,2,4对应的GPF4/5/6三个引脚设为输出 129 } 130 131 /* 132 * Timer input clock Frequency = PCLK / {prescaler value+1} / {divider value} 133 * {prescaler value} = 0~255 134 * {divider value} = 2, 4, 8, 16 135 * 本实验的Timer0的时钟频率=100MHz/(99+1)/(16)=62500Hz 136 * 设置Timer0 0.5秒钟触发一次中断: 137 */ 138 void timer0_init(void) 139 { 140 TCFG0 = 99; // 预分频器0 = 99 141 TCFG1 = 0x03; // 选择16分频 142 TCNTB0 = 31250; // 0.5秒钟触发一次中断 143 TCON |= (1<<1); // 手动更新 144 TCON = 0x09; // 自动加载,清“手动更新”位,启动定时器0 145 } 146 147 /* 148 * 定时器0中断使能 149 */ 150 void init_irq(void) 151 { 152 // 定时器0中断使能 153 INTMSK &= (~(1<<10)); 154 }

interrupt.h

1 void EINT_Handle();

interrupt.c

1 #include "s3c24xx.h" 2 3 void Timer0_Handle(void) 4 { 5 /* 6 * 每次中断令4个LED改变状态 7 */ 8 if(INTOFFSET == 10) 9 { 10 GPFDAT = ~(GPFDAT & (0x7 << 4)); 11 } 12 //清中断 13 SRCPND = 1 << INTOFFSET; 14 INTPND = INTPND; 15 }

main.c

1 int main(void) 2 { 3 while(1); 4 return 0; 5 }

Makefile

objs := head.o init.o interrupt.o main.o timer.bin: $(objs) arm-linux-ld -Ttimer.lds -o timer_linux $^ arm-linux-objcopy -O binary -S timer_linux $@ arm-linux-objdump -D -m arm timer_linux > timer.dis %.o:%.c arm-linux-gcc -Wall -O2 -c -o $@ $< %.o:%.S arm-linux-gcc -Wall -O2 -c -o $@ $< clean: rm -f timer.bin timer_linux timer.dis *.o

以上是关于系统时钟和定时器的主要内容,如果未能解决你的问题,请参考以下文章