ARM总线架构

Posted 『流浪的Coder』

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARM总线架构相关的知识,希望对你有一定的参考价值。

S3C2440集成了丰富了外设控制器(LCD控制器、USB Device控制器、USB Host控制器、NAND FLASH控制器、I2C控制器、SPI控制器等)。要控制这些外设就要设置相应控制器的寄存器以产生相应的驱动时序。学习S3C2440,主要是如何配置寄存器。下面是S3C2440特殊功能寄存器地址:

#define rBANKCON0 (*(volatileunsigned *)0x48000004) //Boot ROM control #define rBANKCON1 (*(volatileunsigned *)0x48000008) //BANK1 control #define rBANKCON2 (*(volatileunsigned *)0x4800000c) //BANK2 cControl #define rBANKCON0 (*(volatileunsigned *)0x48000004) //Boot ROM control #define rBANKCON1 (*(volatileunsigned *)0x48000008) //BANK1 control #define rBANKCON2 (*(volatileunsigned *)0x4800000c) //BANK2 cControl

图1 内存映射

下面就来详细分析。

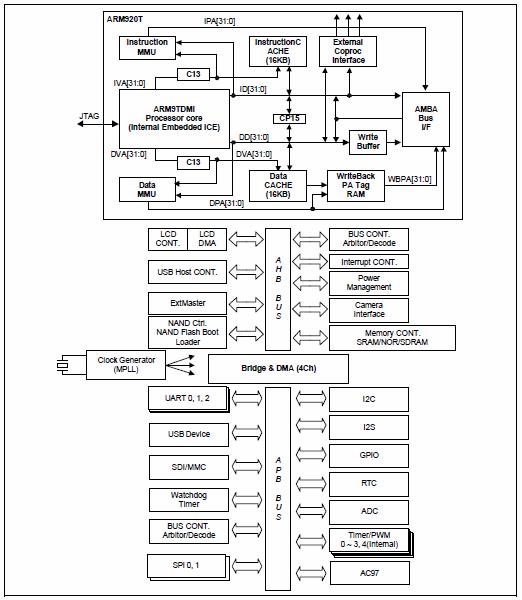

图2 S3C2440结构框图

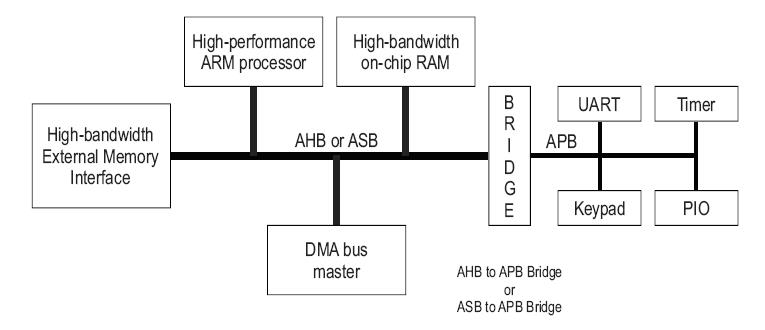

先介绍一下AMBA(Advanced Micro-Controller Bus Architecture)是由ARM Limited公司推出的On-Chip Bus片上总线规范,是目前芯片总线的主流标准。一开始AMBA 1.0只有ASB和APB,为了节省面积,这时候的总线协定都是采用3态的总线,到后来的AMBA 2.0版本,新增了AHB总线,共定义了3组总线:高性能总线(AdvancedHigh Performance Bus,AHB)、系统总线(AdvancedSystem Bus,ASB)和外设总线(Advanced PeripheralBus,APB)。

图3 典型的基于AMBA总线的系统

关于AMBA总线的更多的内容可上网查看,中文的资料都有很多。由图2可知AHB总线上挂载了LCD控制器、中断控制器、USB Host控制器、电源管理、NAND控制器、Camera控制器、存储器控制器以及AHB to APB桥和DMA控制器。APB总线上挂载了UART控制器、I2C控制器、USB Device控制器、I3S控制器SDI/MMC控制器、GPIO、Watchdog/定时器、RTC、ADC、SPI、AC97。下面这段话是摘自S3C2440芯片手册:

"The S3C2440A holds 13 bus masters. They include DRAMrefresh controller, LCD_DMA, CAMIF DMA, DMA0,DMA1, DMA2, DMA3, USB_HOST_DMA,EXT_BUS_MASTER, Test interface controller (TIC) and ARM920T."

S3C2440A有13个主设备。当AHB总线上的主设备读写从设备时,发出的地址经过AHB总线的译码器(通过内存映射表) 产生该地址所对应从设备的选择信号,选中从设备;这样就可以对从设备进行读写啦。

图4 AHB译码器

图5 译码器的具体实现代码

译码器的内存映射表具有相对的独立性。如果AHB总线上的从设备发生了变化,必须对内存映射表进行修改以确保每个地址都对应正确的从设备。下面是内存映射表的一个例子。

图6 内存映射表

使用了两种内存映射表:正常工作下的内存映射表和重新启动时的内存映射表。在正常工作时,微处理器的从设备包括内部RAM、外部RAM、外部ROM和AHB/APB桥;当系统重新启动时,系统的内存映射不包括内部RAM,而是将0x0000—0000至0x0000—03FF的内存地址段映射为nash。这个部分包含系统的启动和初始化代码。当系统启动完成初始化后,AMBA总线将产生一个Remap信号,送入译码器,将译码器的当前内存映射表改为正常工作状态下的内存映射表。

下面是S3C2440的地址映射

AHB Memory Map

Memory control 0x48000000 0x48000030

USB HOST 0x49000000 0x49000058

INTERRUPT 0x4a000000 0x4a00001c

DMA 0x4b000000 0x4b0000e0

CLOCK & POWER MANAGEMENT 0x4c000000 0x4c000018

*LCD CONTROLLER 0x4d000000 0x4d000060 0x4d000400(Palettestart address)

Nand Flash 0x4E000000 0x4E00003C

Camera Interface 0x4F000000 0x4F0000A0

APB Memory Map

UART0 0x50000000 0x50000028

UART1 0x50004000 0x50004028

UART2 0x50008000 0x50008028

PWM TIMER 0x51000000 0x51000040

USB DEVICE 0x52000140 0x5200026c

WATCH DOG TIMER 0x53000000 0x53000008

IIC 0x54000000 0x54000010

IIS 0x55000000 0x55000010

AC97 0x5b000000 0x5b00001C

I/O PORT

A 0x560000000x56000004

B 0x560000040x56000018

C 0x560000200x56000028

D 0x560000300x56000038

E 0x560000400x56000048

F 0x560000500x56000058

G 0x560000600x56000068

H 0x560000700x56000078

J 0x560000d0 0x560000d8

other 0x56000080 0x560000cc

RTC 0x57000040 0x57000088

ADC 0x58000000 0x58000014

SPI 0x59000000 0x59000034

SD Interface 0x5a0000000x5a000040

总结:AHB总线上的译码器根据地址产生相应的片选信号,选中对应的设备。AHB总线上有一个AHB to APB 桥,桥是AHB总线的从设备,是APB总线上唯一的主设备。桥是一个协议转换器(AHB协议到APB协议的转换),它还要完成APB总线的地址译码工作。

<wiz_tmp_tag id="wiz-table-range-border" contenteditable="false" style="display: none;">

以上是关于ARM总线架构的主要内容,如果未能解决你的问题,请参考以下文章