Zynq学习笔记——Hellow World

Posted NingHeChuan

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Zynq学习笔记——Hellow World相关的知识,希望对你有一定的参考价值。

Zynq是一款SOC芯片,之前只是用了PL(Programmable Logic)部分,而Zynq最突出的功能,就是内部的双核Cortex-A9,所以从现在开始我将学习ZYNQ的SOC学习(PS部分)。

本文记录的是熟悉Zynq的PS(Processor Subsystem)部分使用方法,了解开发板资源,做一个最小系统Hellow world,使用资源有ARM Cortex-A9、DDR3内存、一个UART串口。具体流程是将写好的程序加载到DDR内存中,然后CPU一条一条执行,那么执行的情况可以通过串口打印观察。

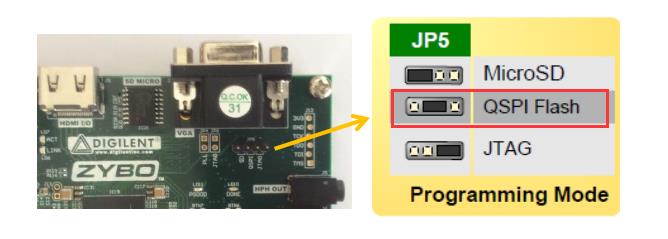

我使用的是迪芝伦官方出品的ZYBO开发板,首先在开发板上选择QSPI Flash跳线帽

供电方式不用改,选择USB供电

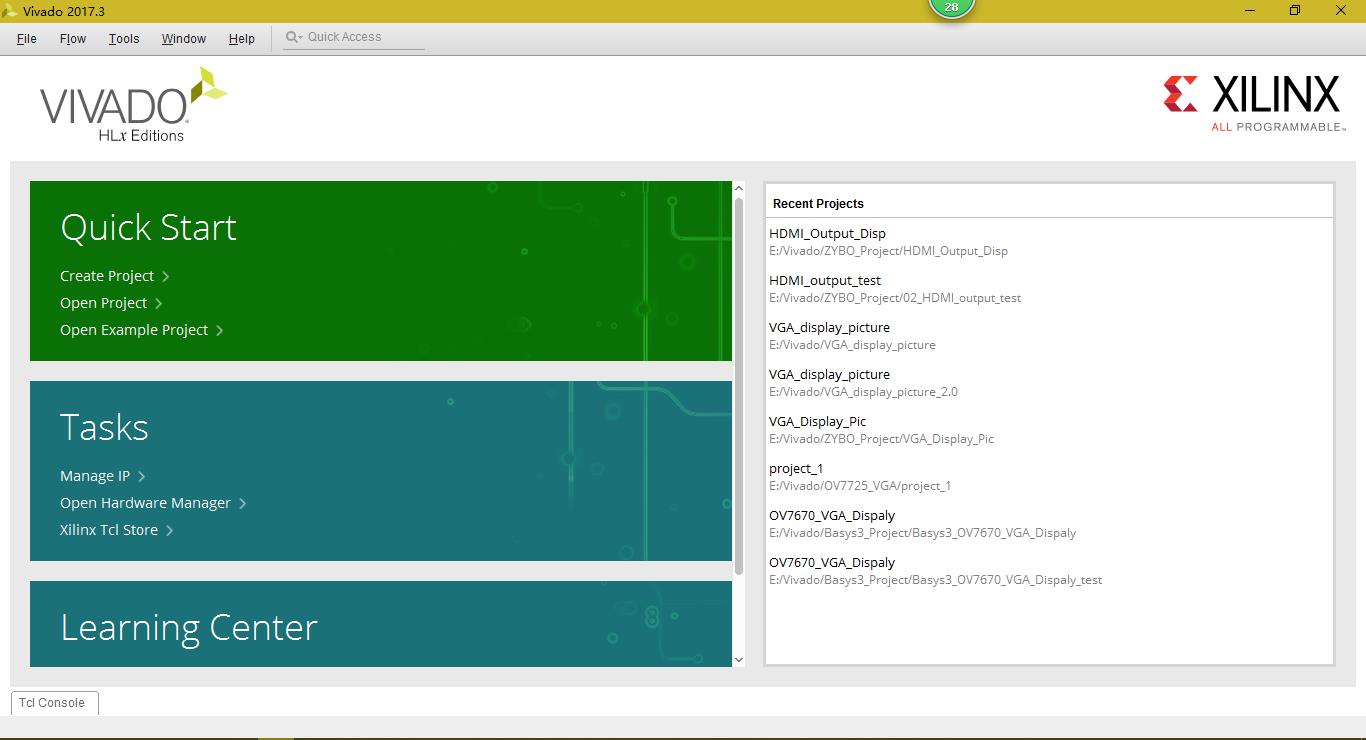

打开Vivado软件,选择Create Project

Next~

添加工程名,next~

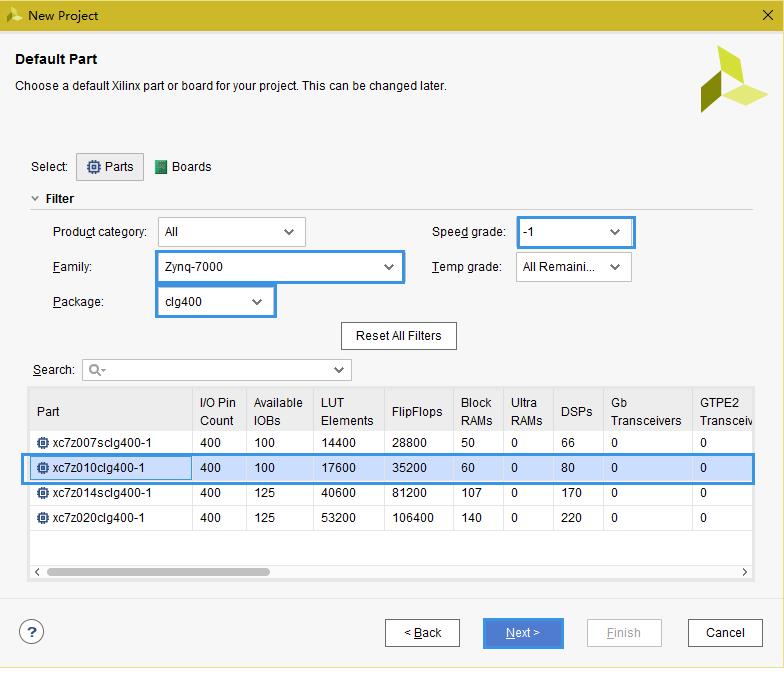

选择开发板型号,我手上的开发板型号如图所示。

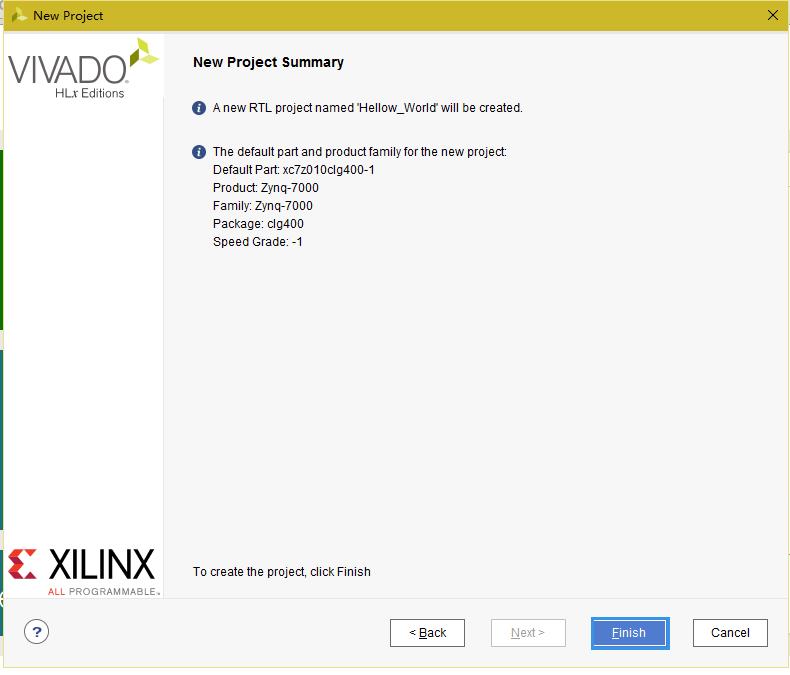

finish~

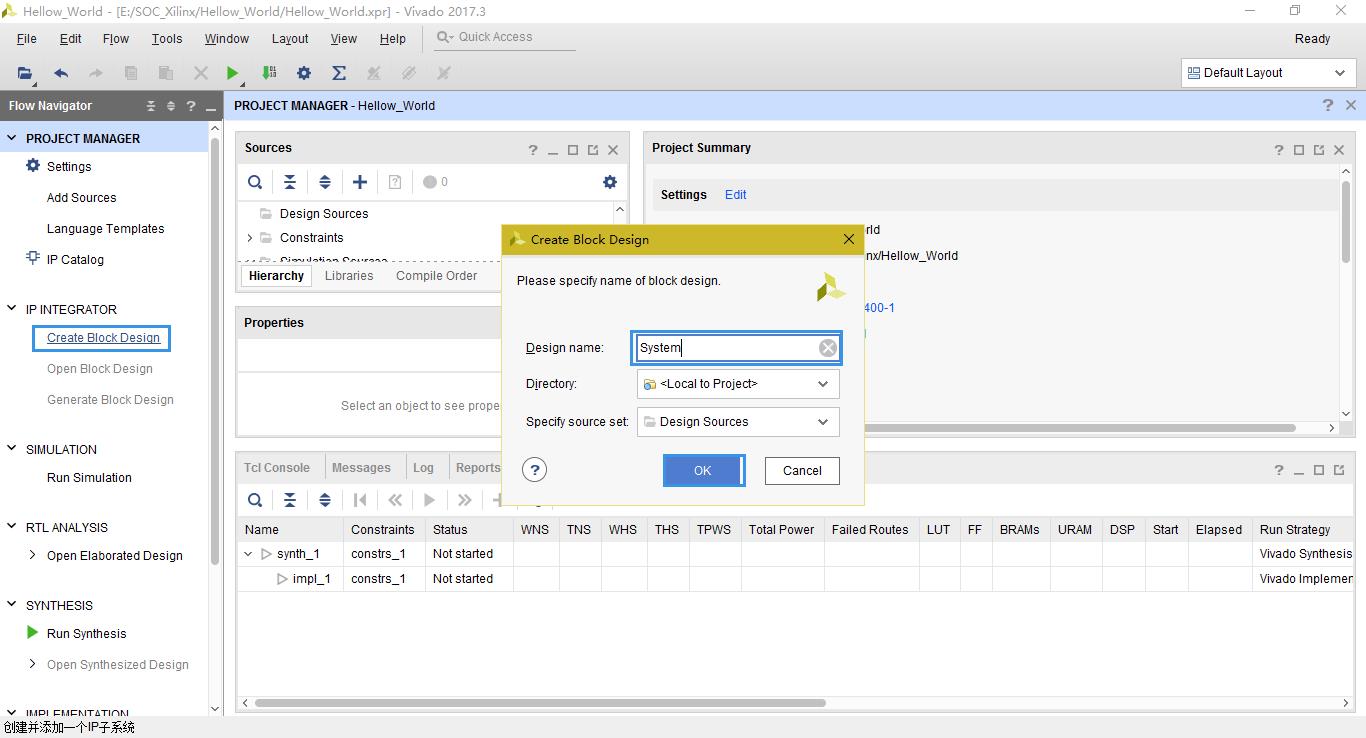

点击create block design,块的名称为system,

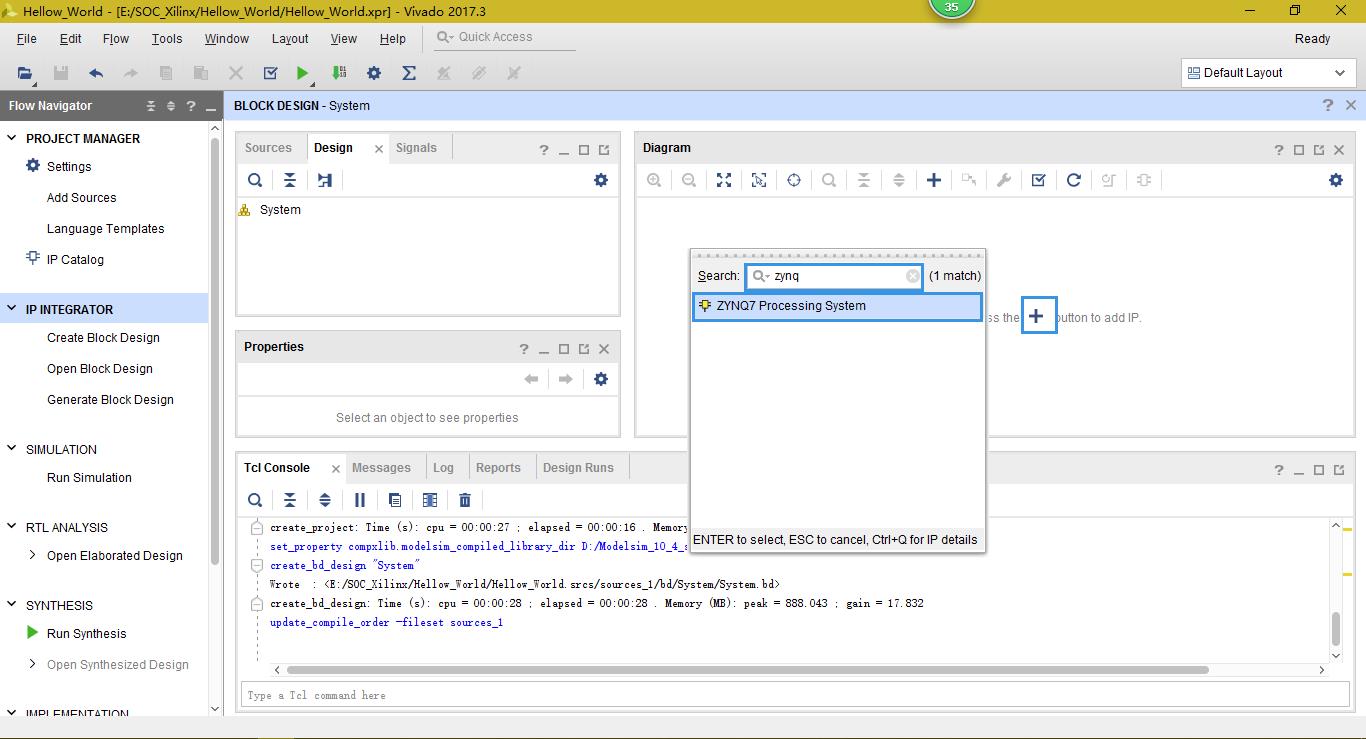

点击图上的加号,查找zynq IP,选择zynq7 processing system。

点击run block automation

这个界面什么也不做,点击OK。

然后就会生成如图所示引脚。

双击进入system,点击clock configuration,ZYBO提供了50Mhz的时钟给PS部分,所以input frequency添加50Mhz,FCLK就是产生的时钟,这里设置为100或者ZYBO PL部分的时钟125Mhz都可以。

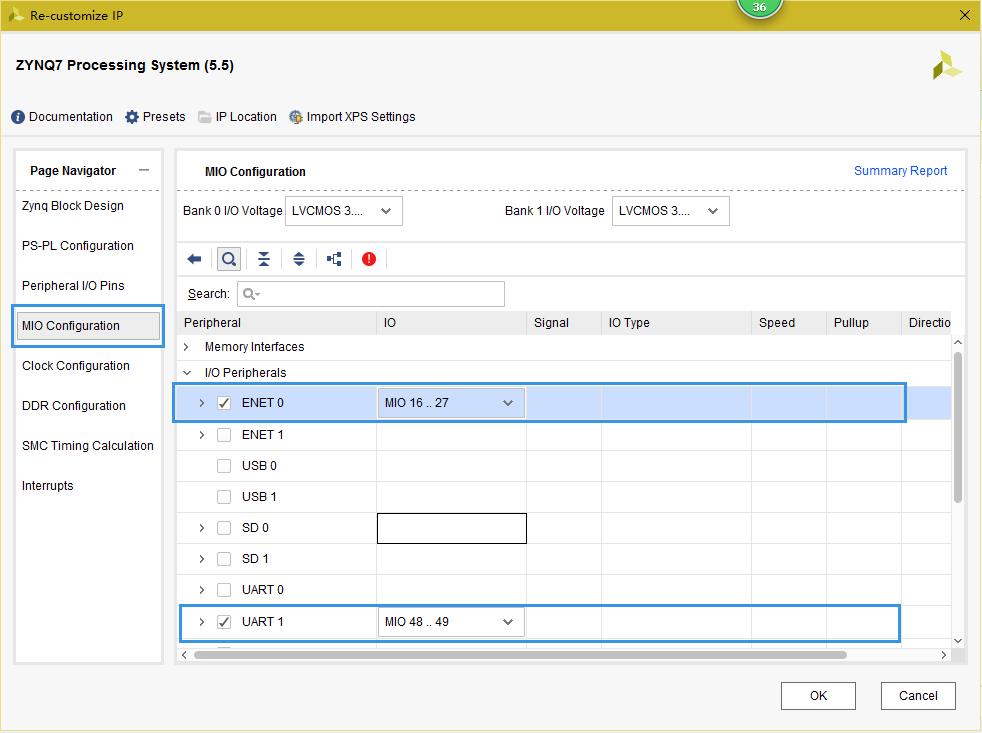

点击MIO configuration——I/O peripheral勾选,如图所示。

这个需要注意的是。右上脚的Bank1 I/O voltage设置为lvcmos 1.8v,因为zynq的bank1的电压是1.8v,其余都是3.3v,这个我们从原理图上可以看到。

这里选择DDR型号,从官方手册上得到zybo包含了两片MT41J128M16JT-125或者,MT41K128M16JT-125 DDR3存储器。原理图上是前者,但经博主实际测试是后者。选择完成后点击OK。

右键点击system.bd,点击generate output products。

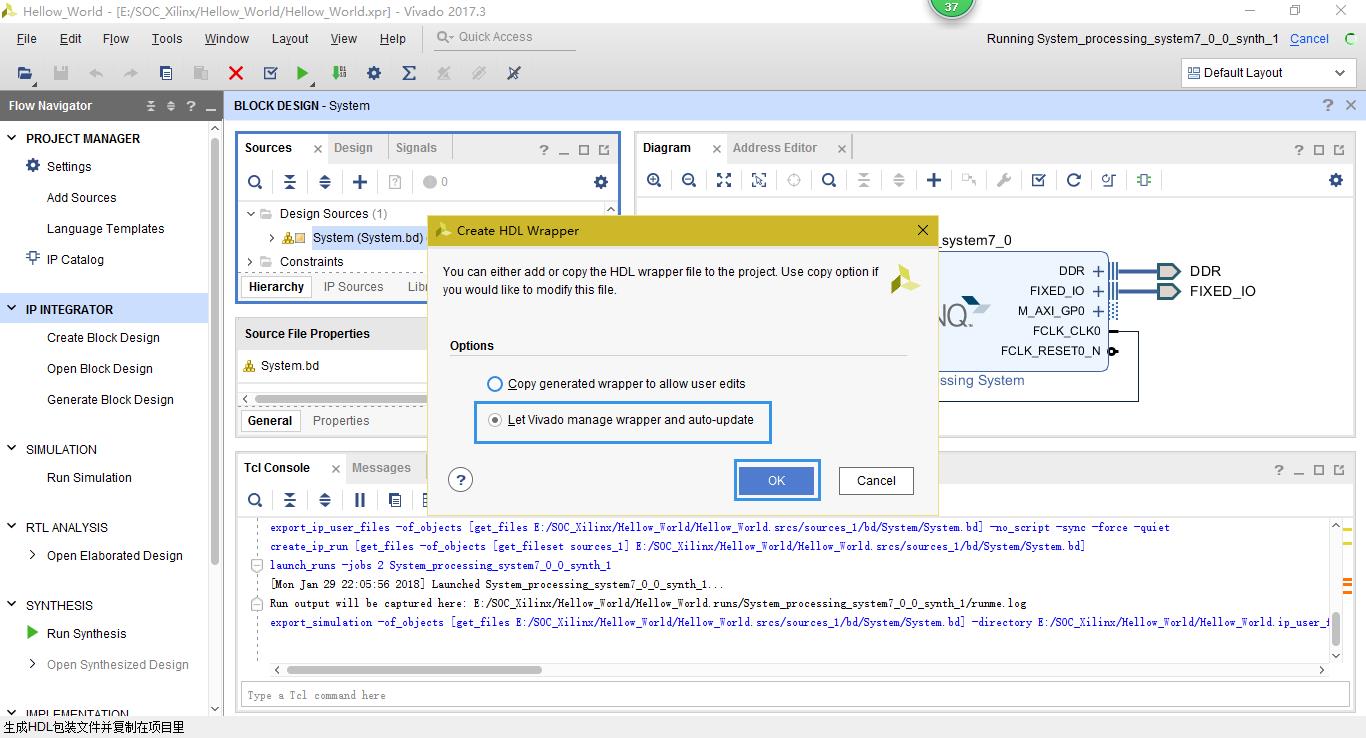

同样右键system.bd,点击create HDL wrapper。

选择如图所示选项,点击OK。这里实际上是生成顶层源码,其中调用了zynq ARM内核IP。

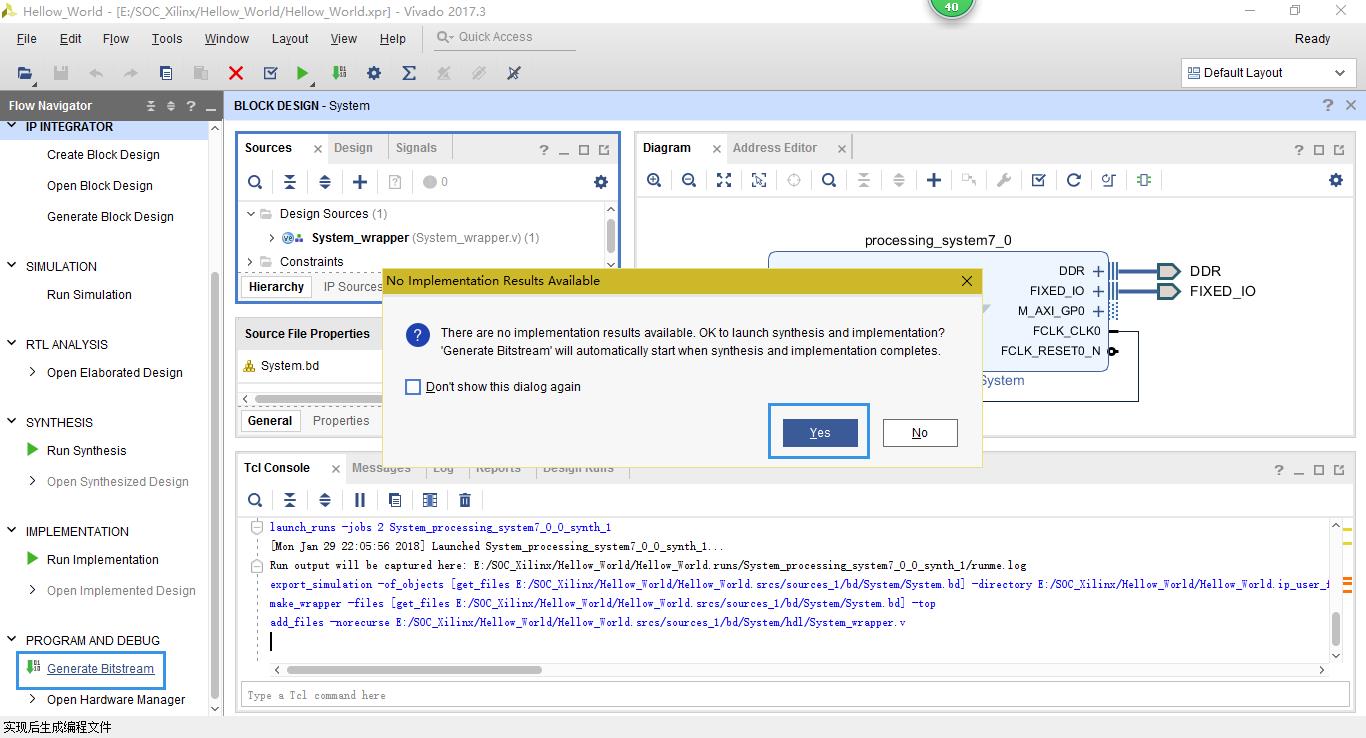

然后点击generate bitstream

点击file——export——export hardware。将SOC硬件导入到SDK。

点击file——launch SDK。接下来就到了软件开发上了。

左边这部分是Vivado定制好的soc硬件,中间这是硬件地址分配空间。

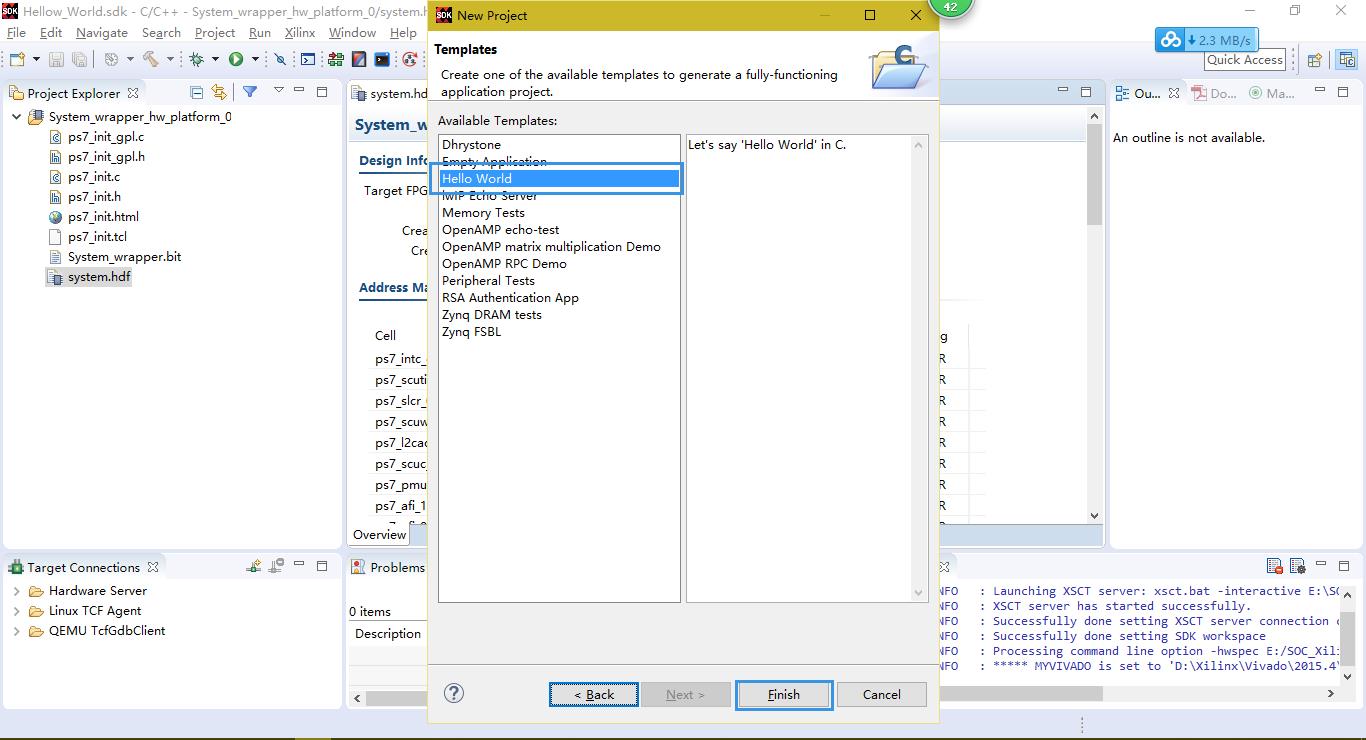

点击file——new——application location,将工程名设置为Hellow World,next。

SDK自带了一些测试程序,我们选择Hellow World

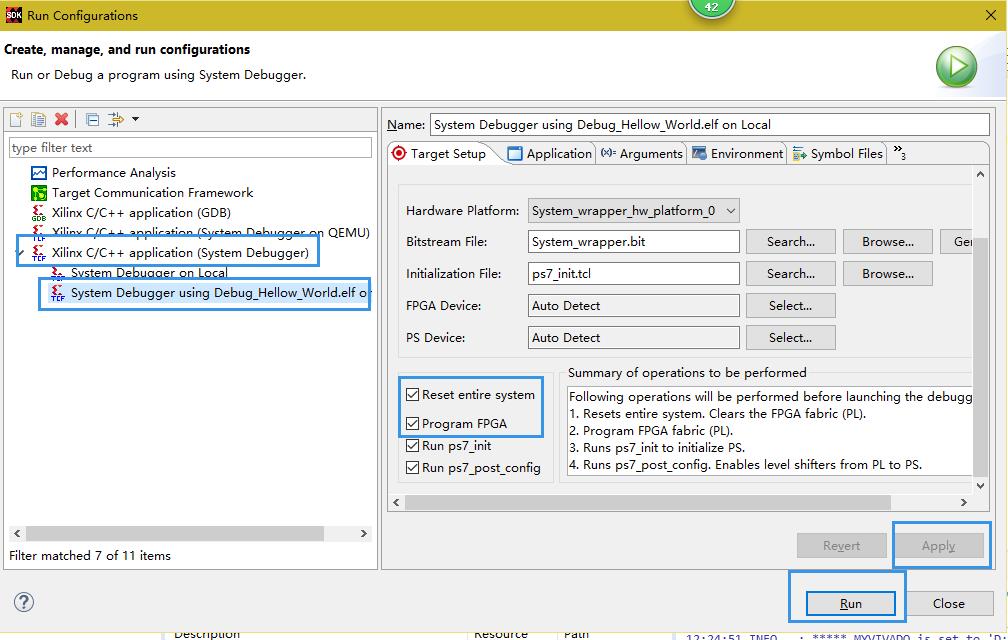

右键Hellow World——Debug AS——Debug Configuration

双击如图所示

注意这里,要run的system debugger要和所创建的工程一直,如图都是Hellow World,然后点击run。这个时候开发板就要连接了。

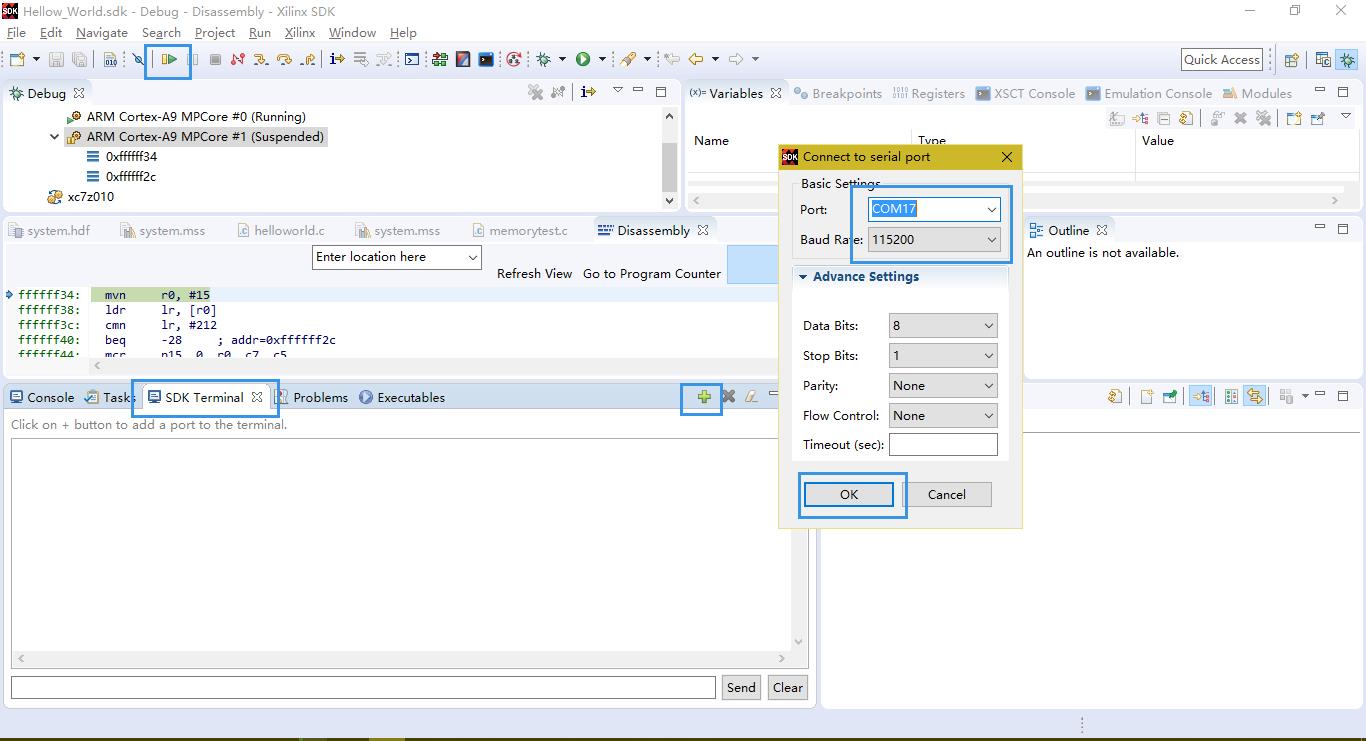

在这一步,用SDK自带的串口调试,SDK Terminal,点击加号添加串口,设置COM口,选择OK。

点击Resume,在SDK Terminal窗口显示Hellow World,测试成功。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

以上是关于Zynq学习笔记——Hellow World的主要内容,如果未能解决你的问题,请参考以下文章

MiZ702学习笔记13——ZYNQ通过AXI-Lite与PL交互