1、前言

目前从事于linux下程序开发,涉及到多个文件,多个目录,这时候编译文件的任务量比较大,需要写Makefile。关于Makefile的详细内容可以参考网上流传非常广泛的《跟我一起写Makefile》http://blog.csdn.net/haoel/article/details/2886/,作者是个大牛,非常佩服。

2、简单测试

测试程序在同一个文件中,共有func.h、func.c、main.c三个文件,Makefile写法如下所示:

1 CC = gcc

2 CFLAGS = -g -Wall

3

4 main:main.o func.o

5 $(CC) main.o func.o -o main

6 main.o:main.c

7 $(CC) $(CFLAGS) -c main.c -o main.o

8 func.o:func.c

9 $(CC) $(CFLAGS) -c func.c -o func.o

10 clean:

11 rm -rf *.o

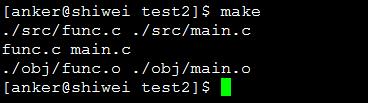

执行过程如下图所示:

3、通用模板

实际当中程序文件比较大,这时候对文件进行分类,分为头文件、源文件、目标文件、可执行文件。也就是说通常将文件按照文件类型放在不同的目录当中,这个时候的Makefile需要统一管理这些文件,将生产的目标文件放在目标目录下,可执行文件放到可执行目录下。测试程序如下图所示:

完整的Makefile如下所示:

1 DIR_INC = ./include

2 DIR_SRC = ./src

3 DIR_OBJ = ./obj

4 DIR_BIN = ./bin

5

6 SRC = $(wildcard ${DIR_SRC}/*.c)

7 OBJ = $(patsubst %.c,${DIR_OBJ}/%.o,$(notdir ${SRC}))

8

9 TARGET = main

10

11 BIN_TARGET = ${DIR_BIN}/${TARGET}

12

13 CC = gcc

14 CFLAGS = -g -Wall -I${DIR_INC}

15

16 ${BIN_TARGET}:${OBJ}

17 $(CC) $(OBJ) -o $@

18

19 ${DIR_OBJ}/%.o:${DIR_SRC}/%.c

20 $(CC) $(CFLAGS) -c $< -o $@

21 .PHONY:clean

22 clean:

23 find ${DIR_OBJ} -name *.o -exec rm -rf {}

解释如下:

(1)Makefile中的 符号 $@, $^, $< 的意思:

$@ 表示目标文件

$^ 表示所有的依赖文件

$< 表示第一个依赖文件

$? 表示比目标还要新的依赖文件列表

(2)wildcard、notdir、patsubst的意思:

wildcard : 扩展通配符

notdir : 去除路径

patsubst :替换通配符

例如下图例子所示:

输出结果如下所示:

SRC = $(wildcard *.c)

等于指定编译当前目录下所有.c文件,如果还有子目录,比如子目录为inc,则再增加一个wildcard函数,象这样:

SRC = $(wildcard *.c) $(wildcard inc/*.c)

gcc -o hello hello.c -I /home/hello/include -L /home/hello/lib -lworld

上面这句表示在编译hello.c时-I /home/hello/include表示将/home/hello/include目录作为第一个寻找头文件的目录,

寻找的顺序是:/home/hello/include-->/usr/include-->/usr/local/include

-L /home/hello/lib表示将/home/hello/lib目录作为第一个寻找库文件的目录,

寻找的顺序是:/home/hello/lib-->/lib-->/usr/lib-->/usr/local/lib

-lworld表示在上面的lib的路径中寻找libworld.so动态库文件(如果gcc编译选项中加入了“-static”表示寻找libworld.a静态库文件)

参考:

http://blog.csdn.net/liangkaiming/article/details/6267357

Makefile中的wildcard用法

在Makefile规则中,通配符会被自动展开。但在变量的定义和函数引用时,通配符将失效。这种情况下如果需要通配符有效,就需要使用函数“wildcard”,它的用法是:$(wildcard PATTERN...) 。在Makefile中,它被展开为已经存在的、使用空格分开的、匹配此模式的所有文件列表。如果不存在任何符合此模式的文件,函数会忽略模式字符并返回空。需要注意的是:这种情况下规则中通配符的展开和上一小节匹配通配符的区别。

一般我们可以使用“$(wildcard *.c)”来获取工作目录下的所有的.c文件列表。复杂一些用法;可以使用“$(patsubst %.c,%.o,$(wildcard *.c))”,首先使用“wildcard”函数获取工作目录下的.c文件列表;之后将列表中所有文件名的后缀.c替换为.o。这样我们就可以得到在当前目录可生成的.o文件列表。因此在一个目录下可以使用如下内容的Makefile来将工作目录下的所有的.c文件进行编译并最后连接成为一个可执行文件:

#sample Makefile

objects := $(patsubst %.c,%.o,$(wildcard *.c))

foo : $(objects)

cc -o foo $(objects)

这里我们使用了make的隐含规则来编译.c的源文件。对变量的赋值也用到了一个特殊的符号(:=)。

1、wildcard : 扩展通配符

2、notdir : 去除路径

3、patsubst :替换通配符

例子:

建立一个测试目录,在测试目录下建立一个名为sub的子目录

$ mkdir test

$ cd test

$ mkdir sub

在test下,建立a.c和b.c2个文件,在sub目录下,建立sa.c和sb.c2 个文件

建立一个简单的Makefile

src=$(wildcard *.c ./sub/*.c)

dir=$(notdir $(src))

obj=$(patsubst %.c,%.o,$(dir) )

all:

@echo $(src)

@echo $(dir)

@echo $(obj)

@echo "end"

执行结果分析:

第一行输出:

a.c b.c ./sub/sa.c ./sub/sb.c

wildcard把 指定目录 ./ 和 ./sub/ 下的所有后缀是c的文件全部展开。

第二行输出:

a.c b.c sa.c sb.c

notdir把展开的文件去除掉路径信息

第三行输出:

a.o b.o sa.o sb.o

在$(patsubst %.c,%.o,$(dir) )中,patsubst把$(dir)中的变量符合后缀是.c的全部替换成.o,

任何输出。

或者可以使用

obj=$(dir:%.c=%.o)

效果也是一样的。

这里用到makefile里的替换引用规则,即用您指定的变量替换另一个变量。

它的标准格式是

$(var:a=b) 或 ${var:a=b}

它的含义是把变量var中的每一个值结尾用b替换掉a

今天在研究makefile时在网上看到一篇文章,介绍了使用函数wildcard得到指定目录下所有的C语言源程序文件名的方法,这下好了,不用手工一个一个指定需要编译的.c文件了,方法如下:

SRC = $(wildcard *.c)

等于指定编译当前目录下所有.c文件,如果还有子目录,比如子目录为inc,则再增加一个wildcard函数,象这样:

SRC = $(wildcard *.c) $(wildcard inc/*.c)

也可以指定汇编源程序:

ASRC = $(wildcard *.S)