armv8 memory translation

Posted _9_8

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了armv8 memory translation相关的知识,希望对你有一定的参考价值。

AArch32,arm的32bit架构;

AArch64,arm的64bit架构;

ARMv8.2-LPA,是armv8.2中的新feature,扩大了IPA和PA的支持范围,从48bit扩展到52bit。

armv8-a core内部使用virtual memory,内部通过mmu转换为physical address。

mmu的好处:

1)允许system同时运行多个task,各个task之间完全是地址透明的。

2)同一个task,code在编写的时候,也完全不需要了解processor内部的地址分配。

3)mmu还可以实现memory access permission的控制,memory attribute的控制,cache policy的控制。

这样app的编写,编译,链接都是在virtual memory space中进行的。

arm提出trustzone之后,定义了两种physical address space,在理论上,secure和non-secure的physical address

应该是完全分开的两个地址空间,甚至存储器,但是在实现中,多通过bus attribute来进行控制。表示的是

同一块地址,在进行secure和non-secure切换的时候,需要自己保存上下文。

arm规定,non-secure不能访问secure空间,但是secure是可以访问secure和non-secure的,这样的化,在应用中

如果一个secure的master,读了两次同一个地址,一次是secure bus读,一次是non-secure bus读,这样在cache

中会出错,所以一般要求,secure在读取non-secure的时候,要求使用non-secure bus attr。

mmu内部的translation table根据exception level分为四级:

1) EL0------app

2) EL1------kernel

3) EL2------hypervisor,armv7加入的一个arm core mode,主要为了virtualization。

4) EL3------secure monitor,在trustzone切换过程中的mode。

一般情况下EL0是执行在unprivilege mode下的,其他三种都是执行在privilege mode下的。需要配置自己的TCR寄存器

EL0和EL1都可以执行在non-secure或secure mode下,但是EL2只能执行在non-secure mode下,EL3只能执行在secure mode下。

EL0和EL1的translation table base address是指定在寄存器中,Translation Table Base Registers(TTBR0_EL1)和(TTBR1_EL1)

EL0和EL1的区分是通过VA的高位地址来区分的,OS的地址都在高位,高位都为1;

APP的地址都在低位,高位都为0;

一般是16bit的高位,这样和32bit级联起来,刚好48bits

EL2和EL3都只有TTBR0,寄存器分别为TTBR0_EL2和(TTBR0_EL3)

除了base address,还有一个Translation control register(TCR_EL1),其中控制

1)IPA size,最终的PA的范围大小,3bits,000---32bitsPA,101---48bitsPA

2)TG0/TG1,translation table的size大小,2bits,00---4KB,01---16KB,11---64KB (Translation Granule)

3)T0SZ/T1SZ,高bits的位数,来区分EL0/EL1的高位,5bits

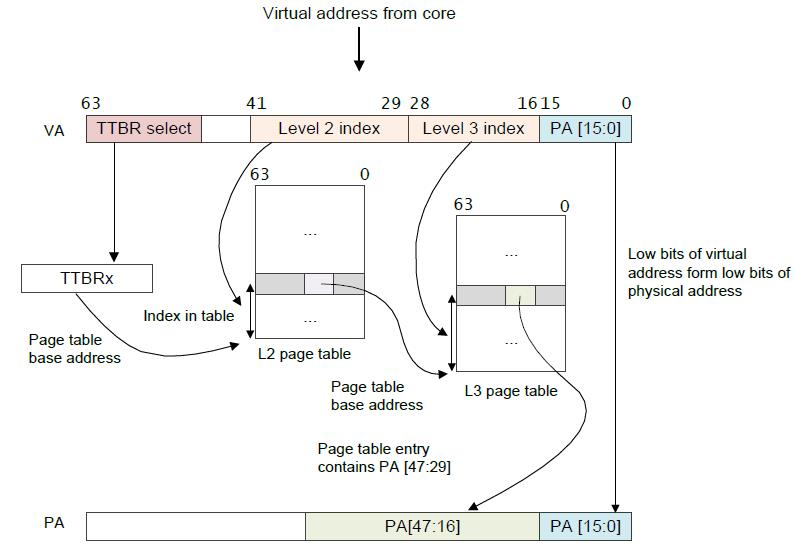

VA到PA的translation:

对于一个nbits的VA空间的应用,高位64-n必须是全零或者全1,否则mmu会报event error。

VA的低位地址,或直接作为PA中的offset,具体bit是按design而定的。

一个转换的流程图,多级转换:

TTBR0_EL1,TTBR1_EL1以及TCR_EL1都是不区分secure和non-secure的寄存器,所以在secure切换的时候,

必须自己做context的保存。

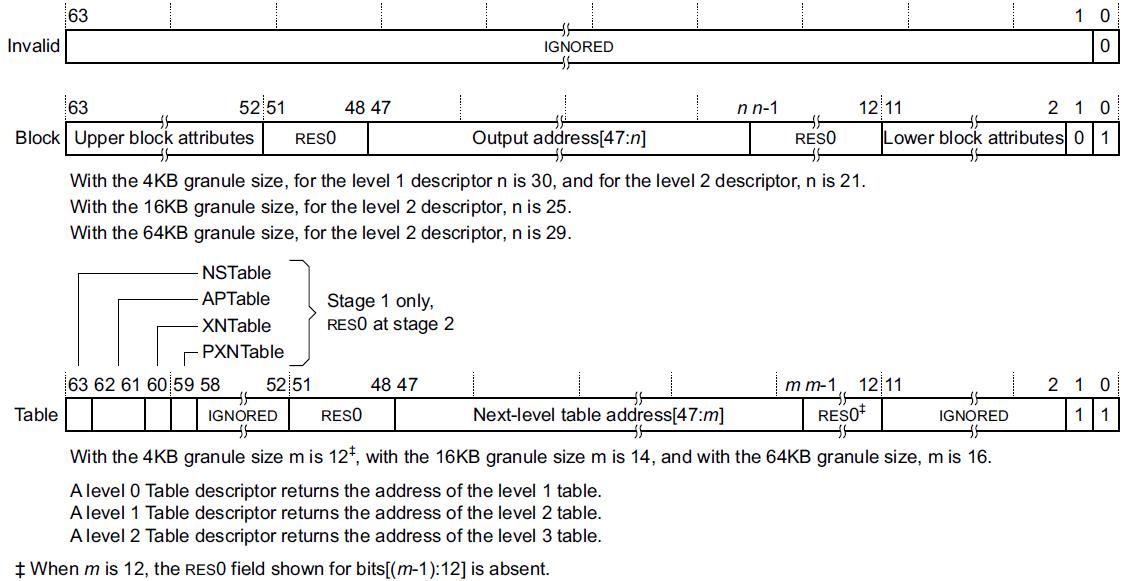

VMSAv8-64的translation table format descripter:

主要有以下几个方面,

1) invalid或者valid; bit[0]

2) table entry或者block entry; bit[1]

descripter与granule的颗粒有关系,

4k granule 16granule 64granule

level0 block entry不支持 block entry不支持 block entry不支持

level1 block entry不支持 block entry不支持(主要看ARMv8.2-LPA是否支持)

level2

对于level3的table,都是支持block entry的,不支持table entry

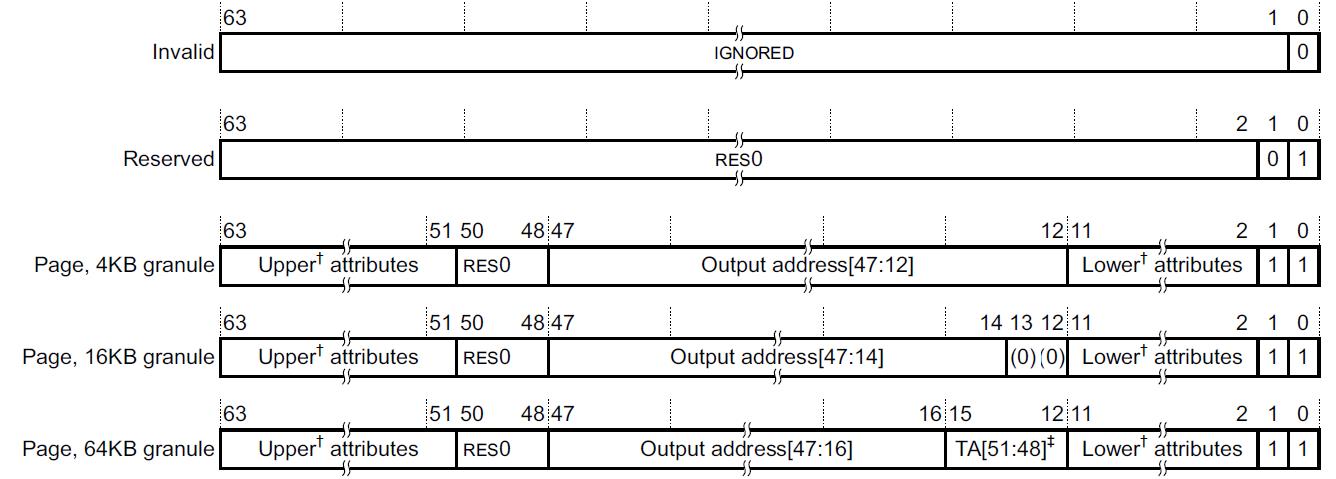

对于不支持ARMv8.2-LPA的level0-level3的descripter的各种格式,

level3的descripter格式:

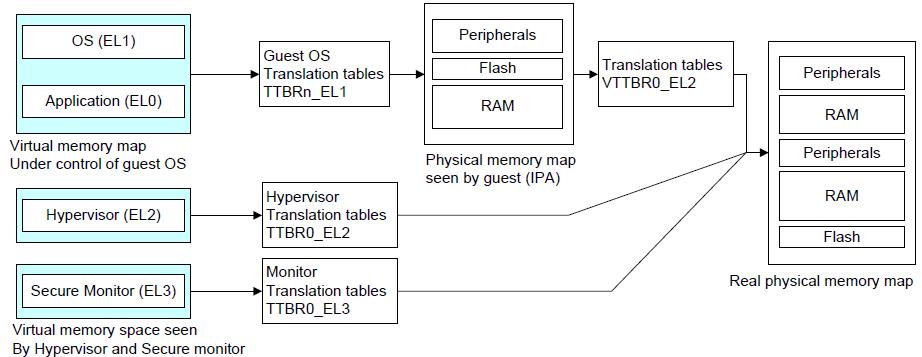

amrv8.2中的多级地址映射:

两级的translations,主要引入了hypervisor的控制,stage1由guest os控制,stage2由hypervisor控制。

1) 主要在level0和level1进行了扩展,可能会有stage2。对于secure的操作,系统中是不允许在做stage2的。

对于non-secure操作,需要配置Hypervisor Configuration Register(HCR_EL2)来进行stage2。

2) EL2和EL3都是只有stage1的,Translation base table,分别有自己的TTBR0_EL2/EL3,secure world是不允许有virtualization的。

3) stage2的 Translation base table寄存器是单独的VTTBR0_EL2,并且有自己单独的control寄存器VTCR_EL2

另一类的access的控制,是对执行attr的控制,反应到bus上就是某些instruction的prefetch不能再一些地址上进行。

block/page可以被标识为Execute Never(XN),Unprivilege Execute Never(UXN),Privilege Execute Never(PXN),

通过配置每个level的SCTLR_ELn寄存器来实现。

AF(access flag),是软件的应用,表明目前该page是否被访问过,优化在OS memory control中的实现。

Bit[58:55],不论是block descripter还是table descripter,中都会预留,为OS使用。可以存放page是否dirty等信息。

mmu中还包括secure ctrl register(SCR)寄存器,可以定义secure是否可以访问non-secure的空间,

arm中还定义了指令LDTR和STTR,可以允许在EL1中执行数据的加载和写入,权限等是按照EL0的配置来执行。

在其他的except level中,LDTR和STTR指令与普通的LDR和STR相同。

TLB(Translation Lookaside Buffer),MMU中访问page translation的cache,每个TLB的entry,都包括memory type,

cache policy,access permission,ASID,VMID等信息。

如果memory中的translation entry已经更新,但是TLB中的未更新,这时需要OS进行invalidation stale TLB entry。

指令TLBI <type> <level>,可以指定stage-level,specify-attr等。

ALL,VMALL,VMALLSI2,ASID,VA,VAA

TLB中的entry是区分secure和non-secure的,所以在secure切换的时候,是不需要context-switch的。

以上是关于armv8 memory translation的主要内容,如果未能解决你的问题,请参考以下文章