CPU

Posted betajj

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了CPU相关的知识,希望对你有一定的参考价值。

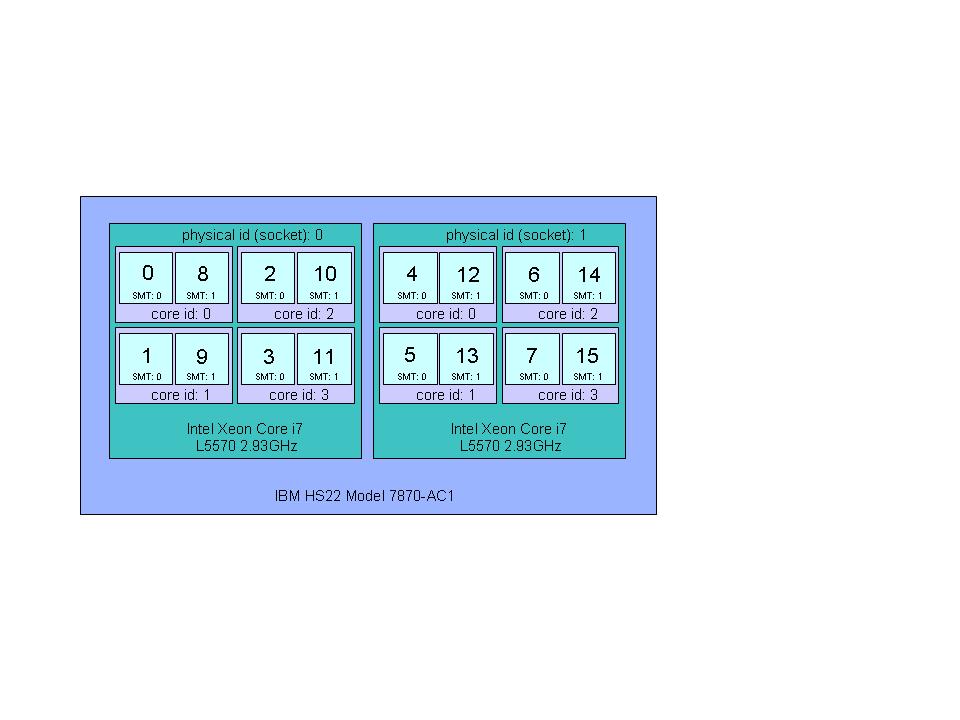

Before setting CPU affinities for device interrupts and application processes and threads it is important to get an accurate picture of CPU physical layout. On System x® this can be done be looking at the physical ID and core ID values of each processor entry in /proc/cpuinfo. CPU entries with the same physical ID are on the same CPU socket. CPU entries with the same physical ID and the same core ID are known as simultaneous multi threads (SMTs) also known as hardware threads on the same core.

Below is a diagrammatic representation of the CPU physical layout described from the information in /proc/cpuinfo for an IBM® HS22 blade. CPU 0 and 8 share a common 32kB instruction and data L1 cache and a 256kB L2 cache. CPU 0 and 1 share a common 8MB (16 way associative) L3 cache. CPU 0 and 4 share no common cache. In the system shown here the optimal (that is, for best latency and throughput) assignment of Low Latency Messaging and application threads to CPUs is (0,1,2,3) or (4,5,6,7) because they each have a dedicated L2 cache and a shared (on die) L3 cache.

This is just one example of microprocessor architecture, before tuning for your system you should understand the cache hierarchy as implemented by the microprocessor manufacturer for your particular system.

以上是关于CPU的主要内容,如果未能解决你的问题,请参考以下文章