09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档

Posted 小梅哥

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档相关的知识,希望对你有一定的参考价值。

芯航线——普利斯队长精心奉献

实验目的: 1.复习按键的设计

2.用模块化设计的方式实现每次按下按键0,4个LED显示状态以二进制加法格式加1,每次按下按键1,4个LED显示状态以二进制加法格式减1

实验平台:芯航线FPGA核心板

实验原理:

在上一讲中设计并验证了独立按键的消抖,这里基于上一讲的按键消抖模块来实现一个加减法计数器,并以此学习模块化的设计方式。

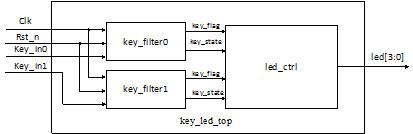

在设计过程中,相对大一点的工程经常通常不会写在一个设计文件中,通常会针对不同的功能设计出不同的子文件,最后在顶层文件中进行例化。基于本讲其模块的划分如图9-1所示。

图9-1 顶层模块端口图

实验步骤:

这里先编写led_ctrl,从图9-1可得出其端口列表如下。

|

input Clk; input Rst_n; input key_flag0,key_flag1; input key_state0,key_state1;

output [3:0]led; |

这里需要进行根据两个按键的状态来进行计数器的加减。

|

reg [3:0]led_r; always@(posedge Clk or negedge Rst_n) if(!Rst_n) led_r <= 4\'b0000; else if(key_flag0 && !key_state0) led_r <= led_r + 1\'b1; else if(key_flag1 && !key_state1) led_r <= led_r - 1\'b1; else led_r <= led_r; |

计数器的初值为4\'b0000,这里当按键0按下即计数器加一计数器变为4\'b0001,由开发板上的led灯电路图可知,led灯为低电平点亮,此时就会出现led0-led3分别为亮亮亮暗,为了更直观的显示效果对输出数据进行取反,这样led的数据就会变为暗暗暗亮,与正常的思路相符合。

|

assign led = ~led_r; |

图9-2 led灯电路图

这样各个独立的模块即编写完成,下面开始顶层文件的设计。

|

module key_led_top(Clk,Rst_n,key_in0,key_in1,led);

input Clk; input Rst_n; input key_in0; input key_in1;

output [3:0]led;

wire key_flag0,key_flag1; wire key_state0,key_state1;

key_filter key_filter0( .Clk(Clk), .Rst_n(Rst_n), .key_in(key_in0), .key_flag(key_flag0), .key_state(key_state0) );

key_filter key_filter1( .Clk(Clk), .Rst_n(Rst_n), .key_in(key_in1), .key_flag(key_flag1), .key_state(key_state1) );

led_ctrl led_ctrl0( .Clk(Clk), .Rst_n(Rst_n), .key_flag0(key_flag0), .key_flag1(key_flag1), .key_state0(key_state0), .key_state1(key_state1), .led(led) );

endmodule |

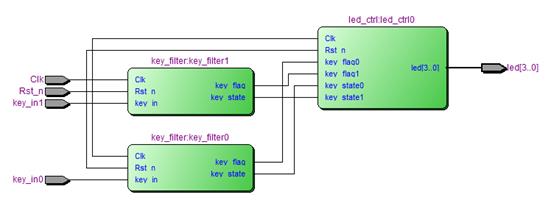

进行分析和综合直至没有错误以及警告。这时可以打开Quartus II软件中的RTL Viewer,查看模块间的连接。如图9-4所示,与设计的顶层模块端口图一样,因此可以看出顶层文件例化正确。

图9-4 顶层模块RTL视图

为了测试仿真编写测试激励文件,这里由于调用了两个按键进行仿真,因此需要将前一讲设计的按键仿真模型进行改写,加入使能信号press,即press上升沿时就执行一次输出key,其中任务task press_key部分是不变的。如果不改写调用的两个仿真模型会同时执行,就导致出错。

|

`timescale 1ns/1ns

module key_model(press,key);

input press; output reg key;

reg [15:0]myrand;

initial begin key = 1\'b1; end

always@(posedge press) press_key;

task press_key; begin ………… end endtask

endmodule |

新建key_led_top_tb.v文件输入以下内容并保存到testbench文件夹下,再次进行分析和综合直至没有错误以及警告。以下内容除了生成了时钟以及复位信号,还模拟了按键0按下释放两次以及按键1按下释放两次的过程。这样整体的代码就如下所示。

|

`timescale 1ns/1ns

`define clk_period 20

module key_led_top_tb;

reg Clk; reg Rst_n;

wire key_in0; wire key_in1; reg press0,press1;

wire [3:0]led;

key_led_top key_led_top0( .Clk(Clk), .Rst_n(Rst_n), .key_in0(key_in0), .key_in1(key_in1), .led(led) );

key_model key_model0( .press(press0), .key(key_in0) );

key_model key_model1( .press(press1), .key(key_in1) );

initial Clk= 1; always#(`clk_period/2) Clk = ~Clk;

initial begin Rst_n = 1\'b0; press0 = 0; press1 = 0; #(`clk_period*10) Rst_n = 1\'b1; #(`clk_period*10 + 1);

press0 = 1; #(`clk_period*3) press0 = 0; #80_000_000;

press0 = 1; #(`clk_period*3) press0 = 0; #80_000_000;

press1 = 1; #(`clk_period*3) press1 = 0; #80_000_000;

press1 = 1; #(`clk_period*3) press1 = 0; #80_000_000; $stop; end

endmodule |

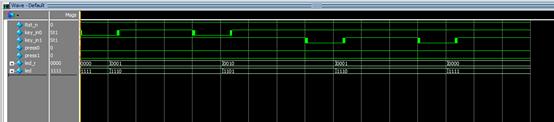

设置好仿真脚本后进行功能仿真,可以看到如图9-5所示的波形文件。每当按键0按下时计数器led_r则会加一,按键1按下后计数器led_r则会减一。

图9-5 功能仿真波形图

分配引脚后全编译无误后下载工程到开发板中。也看到与之对应的现象,即为设计无误。

至此,实现了一个简单的模块化设计,并进行了仿真与板级验证。

以上是关于09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档的主要内容,如果未能解决你的问题,请参考以下文章

02-FPGA设计流程介绍——小梅哥FPGA设计思想与验证方法视频教程配套文档

06-BCD计数器设计与应用——小梅哥FPGA设计思想与验证方法视频教程配套文档

05-IP核应用之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档