电源完整性设计

Posted alifpga

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了电源完整性设计相关的知识,希望对你有一定的参考价值。

由于芯片工艺不断改进,从0.35um、0.18um、0.13um到目前的40nm甚至28nm,芯片的内核电压也在不断降低,从3.3V、1.8V、1.5V到40nm器件的0.9V,芯片对电源的波动越来越敏感。

与SI相比,电源完整性PI是一个比较新的概念,实际上PI也属于SI研究的范畴,它和SI之间的关系非常密切。

保持电源的完整性,就是保持电源的稳定供电。在实际系统中,要做到这一点并不容易,因为系统中总是存在着不同频率的噪声。

首先需要把电源分配系统与外界很好的隔离起来,电源系统与外界主要的连接途径是电压调整模块,通常总是需要在电压调整模块的附近使用T型或者PI型滤波网络。以放置低频噪声串入。同时大电容也提供了一个电荷的蓄水池,及时提供电压调整模块所不能供给的电流。

另外,系统内部的一些元件会产生高频的电源噪声,例如在数字逻辑门在翻转的时候,瞬间会从电源平面汲取一定的电流。电流值虽然不是很大,但是速度很快,如果是电源分配系统的阻抗,电源平面不能及时提供这些电流,那么就会在这里产生翻转噪声。如果PCB去耦处理不当,这个电源噪声就会波及整个电源地平面。

与此相类似,当信号线穿过一个过孔,切换信号的参考平面时,例如由地平面切换到电源平面,相应的会在过孔附近的电源平面和地平面之间形成一个回路电流,这个回路电流同样会成为系统噪声,波及整个电源分布系统。

同步开关噪声

同步开关噪声(SSN)是指由于多个输出同时发生翻转而引起的感应噪声。

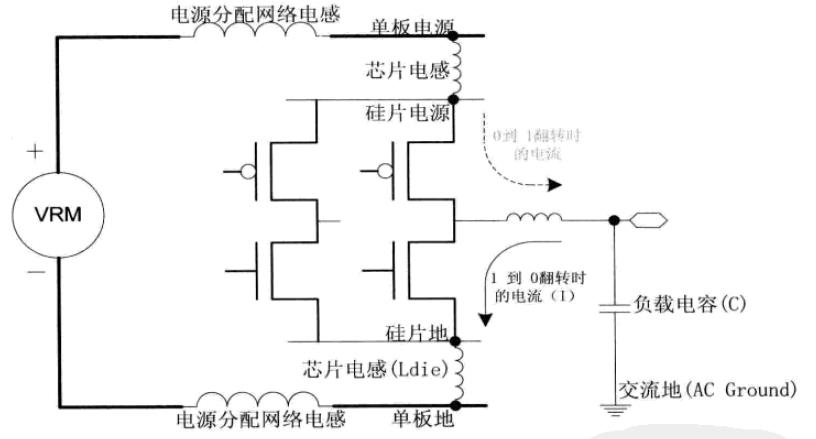

要搞清楚SSN的原理,必须从不同的层面来分析。下图所示,电源分配系统的感抗表示,同时也把硅片到PCB电源之间的连线感抗也表示出来。

SSN模型

从芯片级来考虑,如果多个IO同时由“1”到“0”翻转,会在地脚上产生较大的变化电流,上图实线箭头部分,由于芯片电感的存在,而电感的特性是产生一个反向电动势来抵抗电流的变化,因此在硅片内部的地平面和单板地之间将形成一定的电压波动,这种现象又称为地弹(ground-bounce)。

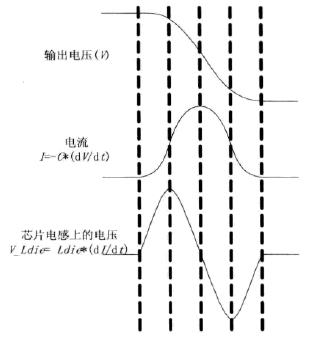

要知道PCB的地和硅片的地之间的电压差关系,首先要分析输出信号的电压变化。当输出信号由“1”翻转到“0”时,在输出驱动器的下拉MOS管和芯片电感上将产生一个相应的电流变化(I),这个电流满足I=-C*(dV/dt),这里的负号表示电流的方向(灌电流)。如下图I的变化情况,首先由0变为最大值,然后再回到0。

SSN产生原理

这样的电流变化会在“芯片电感”两端产生一个电压的波动(V_Ldie) ,根据电感的特性,这个电压值可以表示为V_Ldie=Ldie*(dI/dt),如上图。

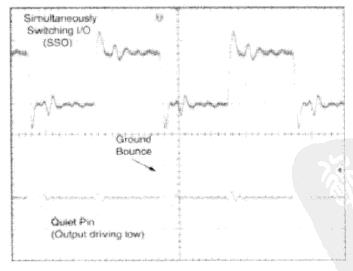

因此,在硅片地和PCB地之间就有一个V_Ldie的电压差,假设PCB地保持不变,硅片地上就有一个相应的噪声信号,这个噪声信号会对输出0的静态信号造成影响,也有可能使得输入信号误采样,如下图,SSN对输出低信号的影响。

SSN对输出低信号的影响

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

以上是关于电源完整性设计的主要内容,如果未能解决你的问题,请参考以下文章