用户定义原语UDP

1.UDP的定义

UDP说明定义如下:

primitive UDP_name (OutputName,List_of_inputs)

Output_declaration

List_of_input_declarations

[Reg_declaration]

[Initial_statement]

table

list_of_tabel_entries

endtable

endprimitive

UDP的定义不依赖于模块定义,因此出现在模块定义以外,也可以在单独的文本文件中定义UDP。

UDP只能有一个输出和一个或多个输入。第一个端口必须是输出端口。输出可以取值0、1、x。输入中出现值z以x处理。

UDP可以描述两类行为:组合电路、时序电路(边沿触发和电平触发)

2.组合电路UDP

在组合电路UDP中,表规定了不同的输入组合和相对应的输出值。没有指定的任意组合输出为x。

例如:

primitive MUX2_1 (Z,Hab,Bay,Sel);

output Z;

input Hab,Bay,Sel;

table

0 ? 1:0;

1 ? 1:1;

? 0 0:0;

? 1 0:1;

0 0 x:0;

1 1 x:1;

endtable

endprimitive

字符?代表不必关心相应变量的具体值,即它可以是0、1或x。输入端口的次序必须与表中各项的次序匹配。

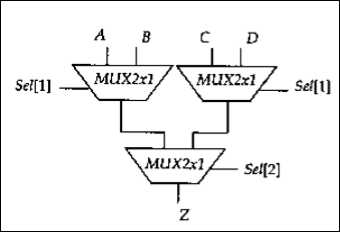

使用2-1多路选择器原语组成的4-1多路选择器:

module MUX4_1(Z,A,B,C,D,Sel);

input A,B,C,D;

input [2:1] Sel;

output Z;

parameter tRISE = 2, tFALL = 3;

MUX2_1 #(tRISE,tFALL)

(TL,A,B,Sel[1]),

(TP,C,D,Sel[1]),

(Z,TL,TP,Sel[2]);

endmodule

在UDP实例中,总共可以指定2个时延,这是由于UDP的输出可以取值0、1或x。

3.时序电路UDP

在时序电路UDP中,使用1位寄存器描述内部状态。该寄存器的值是时序电路UDP的输出值。

共有两种不同类型的时序电路UDP:一种模拟电平触发行为,另一种模拟边沿触发行为。

时序电路UDP使用寄存器当前值和输入值界定寄存器的下一状态。

初始化状态寄存器::时序电路UDP的状态初始化可以使用带有一个过程赋值语句的初始化语句实现。

initial reg_name = 0,1,or x;初始化语句在UDP定义中出现。

电平触发的时序电路UDP

例如D锁存器建模的电平触发的时序电路UDP示例。只有时钟为低电平0,数据就从输入传递到输出,否则输出值被锁存。

primitive Latch(Q,Clk,D);

output Q;

reg Q;

input Clk,D;

table

// Clk D Q(State) Q(next)

0 1 :? : 1;

0 0 :? : 0;

0 ? :? : -;

endtable

endprimitive

"-"字符表示值“无变化”

边沿触发的时序电路UDP

例如用边沿触发时序电路UDP为D边沿触发触发器建模。初始化语句用于初始化触发器的状态。

primitive D_Edge_FF(Q, Clk, Data);

output Q;

reg Q;

input Data,Clk;

initial Q = 0;

table

// Clk Data Q(State) Q(next)

(01) 0 : ? : 0;

(01) 1 : ? : 1;

(0x) 1 : 1 : 1;

(0x) 0 : 0 : 0;

(?0) ? : ? : -; //时钟负边沿

? (??) : ? : -; //稳定时钟上数据不变

endtable

endprimitive

例如对D_Edge_FF的使用

module Reg4(Clk,Din,Dout);

input Clk;

input [0:3] Din;

output [0:3] Dout;

D_Edge_FF

DLAB0(Dout[0],Clk,Din[0]),

DLAB1(Dout[1],Clk,Din[1]),

DLAB2(Dout[2],Clk,Din[2]),

DLAB3(Dout[3],Clk,Din[3]),

endmodule

边沿触发和电平触发的混合行为

在同一个表中能够混合电平触发和边沿触发项。在这种情况下,边沿变化在电平触发之前处理,即电平触发项覆盖边沿触发项。

带异步清空的D触发器的UDP描述:

primitive D_Async_FF(Q,Clk,Clr,Data);

output Q;

reg Q;

input Clr,Data,Clk;

table

// Clk Clr Data Q(state) Q(next)

(01) 0 0 : ? : 0;

(01) 0 1 : ? : 1;

(0x) 0 1 : 1 : 1;

(0x) 0 0 : 0 : 0;

(?0) 0 ? : ? : -;

(??) 1 ? : ? : 0;

? 1 ? : ? : 0;

endtable

endprimitive

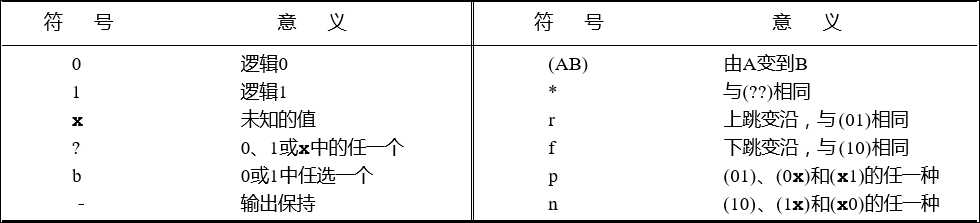

所有能够用于UDP原语中表项的可能值