1.RCC of STM32F103

Posted QIYUEXIN

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了1.RCC of STM32F103相关的知识,希望对你有一定的参考价值。

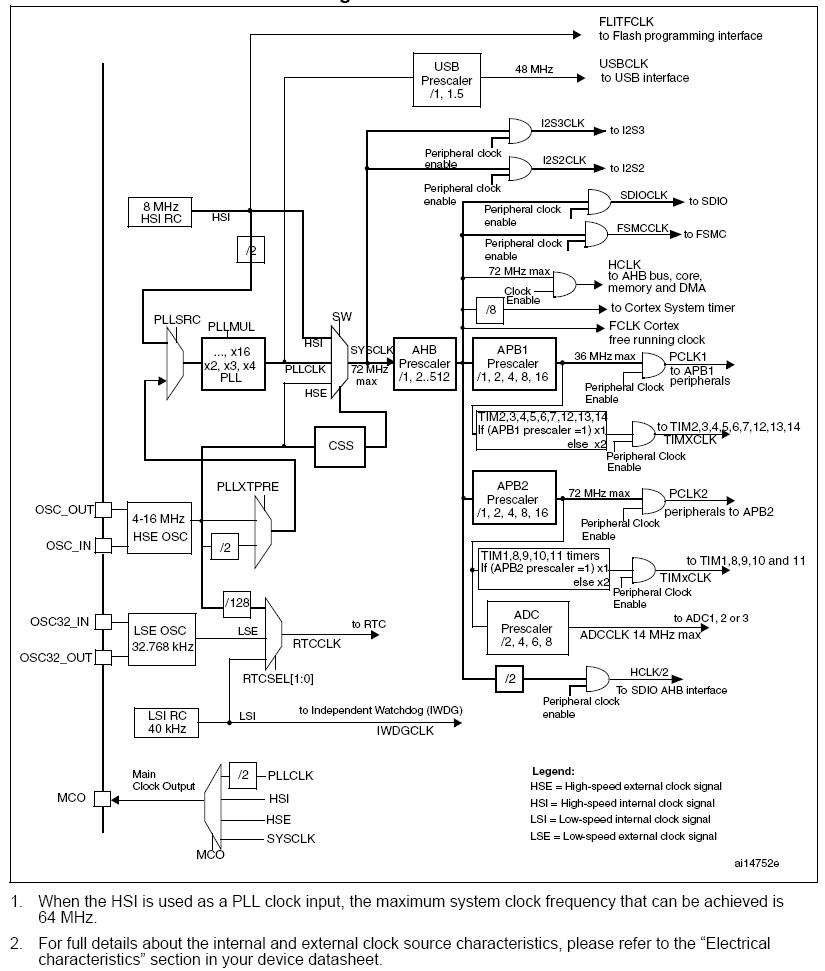

开发板用的是8Mhz晶振,即HSE=8,000,000

f103最大支持72Mhz,即SYSCLK=PLLCLK=72Mhz,HSE=8M,所以PLLM=9即可。

/* HCLK = SYSCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; /* PCLK2 = HCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1; /* PCLK1 = HCLK */ RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2; /* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL)); RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

以上是关于1.RCC of STM32F103的主要内容,如果未能解决你的问题,请参考以下文章