arm中断体系结构

Posted Darren_pty

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了arm中断体系结构相关的知识,希望对你有一定的参考价值。

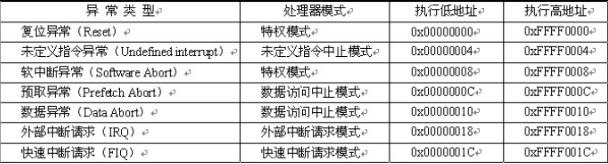

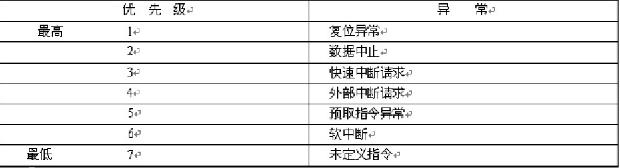

ARM处理器中有7种类型的异常,按优先级从高到低的排列如下:

复位异常(Reset)、

数据异常(Data Abort)、

快速中断异常(FIQ)、

外部中断异常(IRQ)、

预取异常(Prefetch Abort)、

软件中断(SWI)、

未定义指令异常(Undefined instruction)。

ARM异常优先级:

(1)当发生各种异常时,CPU会进入对应的工作模式,并跳转到它的异常向量处进行执行程序,那么这一步骤我们可以在汇编文件中进行配置:

异常向量:在0x00,0x04...处的指令称为异常向量

.text

.global _start

_start:

@0x00复位异常

b reset

@0x04未定义指令终止异常

undefined_interrupt:

b undefined_interrupt

@0x08软中断异常

software_abort:

b software_abort

@0x0c预取异常

prefetch_abort:

b prefetch_abort

@0x10数据异常

data_abort:

b data_abort

@0x14保留

notused:

b notused

@0x18外部中断

handle_iqr:

b handle_iqr

@0x1c快速中断

handle_fqr:

b handle_fqr

(2)当上电或复位时,CPU进入svr模式,进入复位异常并跳转到地址0x00处进行执行程序:

当复位异常时,系统执行下列伪操作:

R14_svc = UNPREDICTABLE value //任意值

SPSR_svc = UNPREDICTABLE value //任意值

CPSR[4∶0] = 0b10011 /*进入管理模式*/

CPSR[5] = 0 /*处理器进入ARM状态*/

CPSR[6] = 1 /*禁止快速中断*/

CPSR[7] = 1 /*禁止外设中断*/

If high vectors configured then

PC = 0xffff0000

Else

PC = 0x00000000

复位异常中断处理程序的主要功能:

*设置异常中断向量表。

*初始化数据栈和寄存器。

*初始化存储系统,如系统中的MMU等。

*初始化关键的I/O设备。

*使能中断。

*处理器切换到合适的模式。

*初始化C变量,跳转到应用程序执行。

reset: ldr sp,=4096 //设置栈 bl disable_watch_dog //关闭看门狗 msr cpsr_c, #0xd2 // ldr sp, =3072 //(在复位异常中提前设置中断模式的栈指针,防止中断触发时栈指针未设置而系统崩溃)

msr cpsr_c, #0xd3 //0xd3--11010011b

ldr sp, =4096 //进入管理模式,设置栈指针

bl init_led //初始化led的gpio管脚

bl init_irq //初始化中断

msr cpsr_c, #0x53 //使能IRQ中断0x53--01010011

ldr lr, =halt_loop //设置返回地址

ldr pc, =main //调用main函数

halt_loop:

b halt_loop

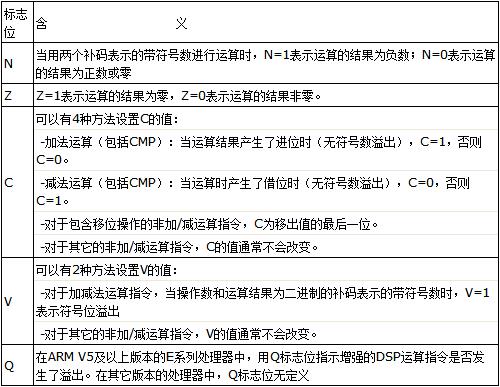

关于当前程序状态寄存器CPSR及msr,mrs汇编指令的知识:

1)CPSR寄存器

ARM每种工作模式除R0~R15共16个寄存器外,还有第17个寄存器CPSR,CPSR中一些位被用于标识各种状态,一些位被用于标识当前出于什么工作模式

如上图所示,它的CPU状态位=> T位=0 --ARM状态

=1 --Thumb状态

它的中断禁止或使能位=> I和F位=0 --使能

=1 --禁止

它的M[4:0]位=> xxxxx,通过编写它可以使得CPU进入相应的工作模式

它的条件码标志位:N、Z、C、V--它们的内容可被算术或逻辑运算的结果所改变,并且可以决定某条指令是否被执行。

2) msr及mrs汇编指令

格式:MRS{<条件码>}Rd,CPSR}SPSR

其中:

Rd 目标寄存器,Rd不允许R15。

R=0 将CPSR中的内容传送目的寄存器。

R=1 将SPSR中的内容传送至目的寄存器。

功能:将状态寄存器的内容传送至通用寄存器。

2 格式:MSR{<条件码>CPSR_<field>|SPSR_<field>,Rm

其中:

<field>字段可以是以下之一或多种:(位从右到左)

C:控制域屏蔽字段(PSR中的第0位到第7位);

X:扩展域屏蔽字段(PSR中的第8位到第15位);

S:状态域屏蔽字段(PSR中的第16位到第32位);

F:标志域屏蔽字段(PSR中的第24位到第31位)。

Rm 源寄存器。

功能:将通用寄存器的内容传送至状态寄存器。

(3)当触发中断时,CPU进入中断模式,并跳转到中断异常向量处进行执行:

1.计算返回地址

2.现场保存工作

3.执行中断服务函数

4.清理现场,中断返回

handle_iqr: sub lr,lr, #4 //lr=lr-4 计算返回地址 stmdb sp!, {r0-r12,lr} ldr lr, =int_return ldr pc, =EINT_Handleiqr int_return: ldmia sp!, {r0-r12,pc}^

以上是关于arm中断体系结构的主要内容,如果未能解决你的问题,请参考以下文章