Xilinx Artix7 FPGA供电电压

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Xilinx Artix7 FPGA供电电压相关的知识,希望对你有一定的参考价值。

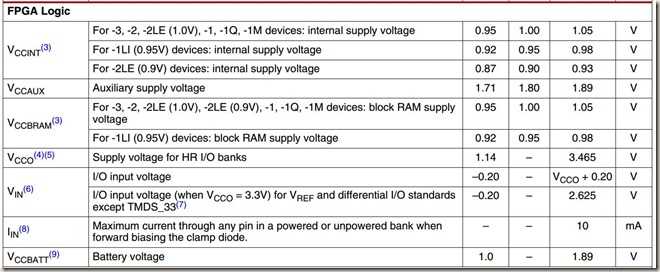

Artix7 FPGA的供电电压大致可以分为三个大的种类: FPGA逻辑电压、GTP高速串行收发器电压和XADC电压。FPGA逻辑电压包括内核电压、辅助电压、Block RAM电压和IO电压四种;GTP电压有GTP收发器电压和GTP收发器终端电压两种;XADC电压有XADC供电电压和XADC外部输入参考电压两种。这八种电压并不一定全部都要单独供电,比如内核电压和Block RAM电压就可以一起供电。

一. FPGA Logic Voltage

FPGA逻辑电压信息如下图所示:

1.1 IO供电电源

从上图中我们可以看出,内核电压VCCINT、辅助电压VCCAUX和Block RAM电压VCCBRAM三种电压的范围都在Typ±1%以内,但是IO电源VCCO却是一个从1.14V~3.465V的范围,这个明显不是IO电源的误差范围,而是因为Artix7 FPGA的IO管脚支持不同的电平标准。

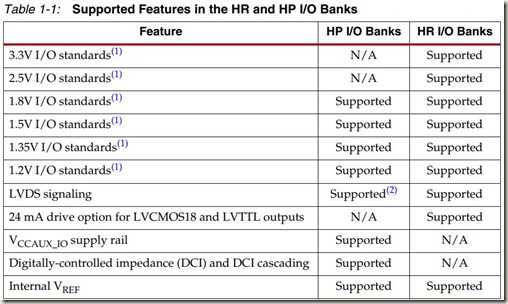

Xilinx的7系列FPGA有两种IO Bank:HP(High Performace)和HR(High Range)。Virtex7部分型号的器件仅部分型号带有HR类型的IO Bank,全部型号都带有HP类型的IO Bank;Kintex7器件同时支持HR和HP两种IO Bank;Artix7和Spartan7仅有HR类型的IO Bank。

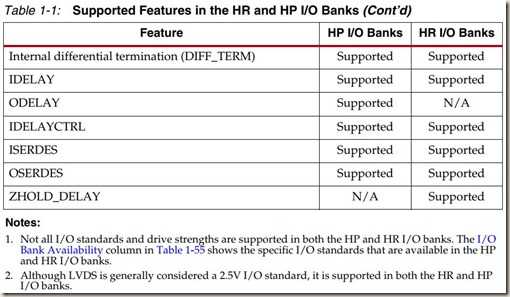

HR和HP两种类型的IO Bank支持的电平标准如下两图所示:

在使用Xilinx的综合工具(ISE或Vivado)对Artix7器件进行开发时,如果不在约束文件里声明管脚类型,默认使用3.3V电平标准。

另外,Artix7 FPGA的每个IO Bank 都可以单独供电,也就是说,不同的IO Bank可以使用不同的电平标准。外部信号输入FPGA的电平、IO Bank供电电压和约束文件里声明必须一致,不然轻则导致整个FPGA系统不能正常工作,重则导致FPGA器件甚至更大范围的器件损毁。

1.2 内核电压、Block RAM电压和辅助电压

FPGA的内核一般就是指FPGA内部的工作逻辑,内核电压即为内部逻辑的工作电压,一般情况下整个FPGA器件功耗的大头就是内核功耗。一般器件的内核电压为1.0V,低功耗器件的内核电压要更低一些。

Block RAM电压即为FPGA内部的Block RAM资源的工作电压。关于Block RAM资源,以前看过一些Spartan6 FPGA的资料,7系列的资料只是大致浏览了一下,发现变化好像不是很大。

辅助电压这东西我一直都不是很明白使用来干什么的,如果有路过的大神明白,还请不吝赐教。

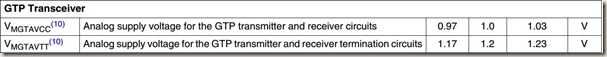

二. GTP电压和XADC电压

2.1 GTP电压

这俩电压是Artix7 FPGA GTP资源工作的必要电压,有专门的供电脚。

GTP对电源噪声的要求稍微有点高:电源纹波峰峰值不能超过10mV,不然就会影响性能。

关于GTP资源更多的信息,目前还在看相关资料,看完之后会整理出一个笔记来。

2.2 XADC电压

这俩电压跟上面说的几个电压是不共地的,具体情况还得等我看完相关文档之后再做总结,这里就先把电压放这。

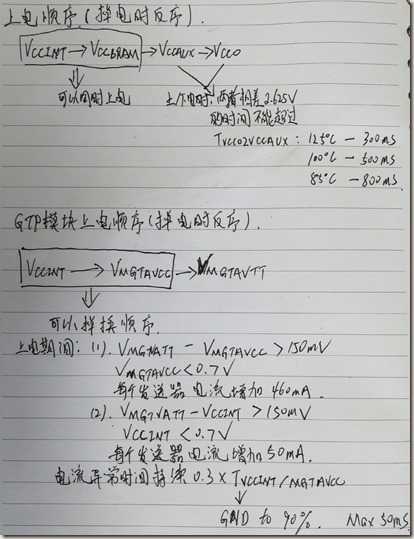

三.上电序列

上面提到的各类电源如果随随便便怼上去是会出问题的,上电基本法如下:

灵魂画师说的就是我啊~~~~~

内核电压必须首先到达指定压值,这个跟上电配置过程有关系,内核在上电配置器件会将所有IO都设置为三态模,具体情况之后会单独写一个关于FPGA配置过程的笔记。

对GTP功能的电压要求主要是为了获得最小消耗电压。

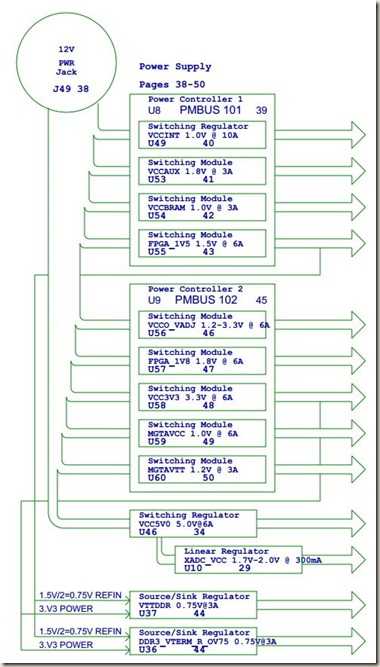

Xilinix官方开发板达成上电序列要求的方法是:各个电压都有外部输入的12V电压经各种电源芯片一起转换,然后用电源管理芯片UCD90120A来产生电源芯片的使能信号,控制上电过程。

以上是关于Xilinx Artix7 FPGA供电电压的主要内容,如果未能解决你的问题,请参考以下文章