TrustZone软硬件架构

Posted Q7318

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了TrustZone软硬件架构相关的知识,希望对你有一定的参考价值。

第一章TrustZone的硬件结构

1. 系统结构

TrustZone硬件架构旨在提供安全框架,从而使设备能够抵御将遇到的众多特地威胁。

TrustZone技术可提供允许SoC设计人员从大量可在安全环境中实现特定功能的组件中进行选择的基础结构,而不提供固定且一成不变的安全解决方案。

架构的主要安全目标是支持构建可编程环境,以防止资产的机密性和完整性受到特定的攻击。具备这些特性的平台可用于构建一组范围广泛的安全解决方案,而使用传统方法构建这些解决方案将费时费力。

可通过以下方式确保系统安全:隔离所有SoC硬件和软件资源,使他们分别处于两个区域(用于安全子系统的安全区域以及用于存储其他所有的内容的普通区域)中。支持TrustZone的AMBA3 AXITM总线构造中的硬件逻辑可确保普通区域组件无法访问安全区域资源,从而在这两个区域之间构建强大边界。将敏感资源放入安全区域的设计,以及在安全的处理器内核中可靠运行软件可确保资产能够抵御众多潜在攻击,包括那些通常难以防护的攻击(例如,使用键盘或触摸屏输入密码)。通过在硬件中隔离安全敏感的外设,设计人员可限制需要通过安全评估的子系统的数目,从而在提交安全认证设备时节省成本。

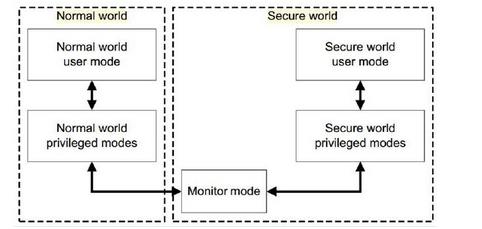

TrustZone硬件架构的第二个方面是在一些ARM处理器内核中实现扩展。通过这些额外增加的扩展,单个处理器内核能够以时间片的方式安全有效地同时从普通区域和安全区域实行代码。这样,使无需使用专用安全处理器内核,从而节省了芯片面积和能源,并且允许高性能安全软件与普通区域操作环境一起运行。 更改当前运行的虚拟处理器后,这两个虚拟处理器通过新处理器模式(监控模式)来实现上下文切换。

物理处理器用于从普通区域进入监控区域的机制受到密切控制,并且这些机制始终被视为监控模式软件的异常。要监视的项可由执行专用指令(安全监控调用(SMC)指令)的软件触发,或由硬件异常机制的子集触发。可对IRQ、FIQ、外部数据中止和外部预取中止异常进行配置,以使处理器切换到监控模式。

在监控模式中执行的软件是实现定义的,但它通常保存当前区域的状态,并还原切换到的区域位置的状态。然后,它将执行从异常返回的操作,以在已还原区域中重新启动处理过程。TrustZone硬件架构的最后一个方面是安全感知调试基础结构,它可控制对安全区域调试的访问,而不会削弱普通区域的调试可视化。

1.1 AMBA3 AXI 系统总线

为了支持TrustZone技术,AXI总线上每个读写信道都增加了一个额外的控制信号: AWPROT[1]:总线写事务控制信号—低电平为安全写事物,高电平为非安全写事物。 ARPROT[1]:总线读事物控制信号—低电平为安全读事物,高电平为非安全读事物。

当主设备向总线提出读写事物请求时必须将控制信号发送到总线上。总线或者从设备的解码逻辑必须能够解释这些信号,确保安全从设备不被非安全的主设备访问。如果非安全主设备访问安全从设备,则访问失败。访问失败时可能会产生一个错误信号,也可能什么也不做,这依赖于具体硬件实现。错误信号可能由从设备或者总线产生,取决于外设的硬件设计和总线配置。

1.2 AMBA3 APB 外围总线

TrustZone架构一个最有用的特性就是其有保护外设安全的能力,比如:中断控制器、计时器及用户I/O设备。这使得安全环境能够解决比仅仅提供一个安全的数据处理环境更广泛的安全问题。安全中断控制器和计数器允许非中断安全任务来监控系统,安全时钟源保证了坚固的DRM,安全键盘使得用户密码输入能够得到安全保障。

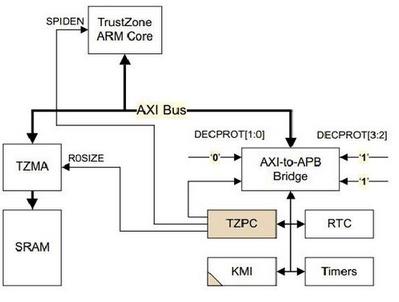

AMBA3 规范包含了一个低门数,低带宽的外设总线,被称作高级外设总线(APB),APB通过AXI-to-APB桥连接到系统总线上。APB总线没有带对应的NS位,这使得已经存在的AMBA2 APB外设与实现了TrustZone技术的系统兼容。AXI-to-APB负责管理APB外设的安全。

1.3 内存隔离

Cache tags所携带的额外的NS位,可以看作是第33根地址线。处理器访存时,除了将内存地址发送到AXI总线上之外,还需要将AWPROT或ARPROT控制信号发送到总线上,以表明本次访存是安全事务还是非安全事务。如果当前系统处于安全状态,控制信号电平的高低取决于页表项的NSTID值。如果当前系统处于非安全状态,控制信号始终为高电平,即非安全事务。

TrustZone通过两个设备来保障物理内存的安全,一个是TrustZone地址空间控制器(TZASC),另一个是TrustZone存储适配器(TZMA):

1> TZASC是AXI的一个主设备,用来将它的从设备的地址空间划分为一系列内存空间。通过运行在安全环境的安全软件,可以将这些区间配置为安全的或者非安全的。TZASC可以拒绝非安全的事物访问安全内存区间。可以划分的内存区间数以及TZASC AXI接口的总线宽度取决于具体的SoC设计。使用TZASC的主要目的是用来将一个AXI从设备进行分区为几个安全设备,比如说片外DRAM。因为多连接一块DRAM芯片需要额外的引脚和印刷电路板面积,并且内存本身也是要一定费用,所有通过对内存进行分区,使它能够包含安全和非安全分区,比两个执行环境各采用一块单独的内存更经济。ARM动态内存控制器(DMC),它本身并不支持创建安全和非安全分区。为了创建安全分区,可以将DMC接到TZASC上。TZASC只用来支持存储映射设备,不能用于块设备,比如NAND FLASH。

2> TZMA使得可以对片上静态内存RAM或者片上ROM划分安全分区。将单独的一个大内存划分为安全区和非安全区比为每一个执行环境提供一个单独的内存要经济。TZMA支持为最大2M的静态内存划分分区低地址部分为安全的分区,高低地部分为不安全的分区。安全分区和非安全分区的分界点是4KB的整数倍,分区的具体大小通过TZMA的输入信号ROSIZE控制,这个信号来自于TrustZone保护控制器(TZPC)的输出信号TZPCROSIZE。通过对TZPC编程可以动态地配置安全区大小。TZMA不能用来对动态内存进行分区,也不能用在要求几个分区的情况,这些情况可以使用TZASC。

2 处理器结构

每个带TrustZone安全扩展的处理器核都有两个虚拟处理器核,每个处理器核分属不同的执行环境(安全和非安全),并引入了一个特殊的机制——监控模式,负责不同执行环境间的切换。非安全虚拟处理器能仅仅访问非安全系统资源,但安全虚拟处理器能访问所有的资源,如图2-1所示

2.1 监控器和监控模式

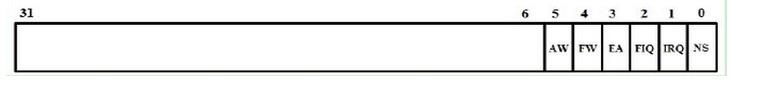

在带TrustZone安全扩展的ARM处理器的CP15协处理器中有一个安全配置寄存器(SCR),该寄存器中有一个NS位,这个NS位指明当前系统的状态,寄存器的格式如图2-2所示。如果NS为0,则当前系统处于安全态;如果NS为1,则当前系统处于非安全态。但当系统处于监控模式时,不管NS位是否为0,都可以访问安全环境的资源。这个NS位不仅影响CPU内核和内存子系统,还可以影响片内外设的工作。NS位是TrustZone对系统所做的关键扩展。系统的安全状态与系统的用户模式和特权模式无关,也就是说用户态程序也可以运行在安全态,而运行特权态程序时系统也可能处于非安全态。NS位只能被运行在安全态且处于特权模式的软件改变,系统在非安全状态时不能访问SCR寄存器。安全环境的软件在安全态下运行,普通环境软件在非安全态下运行。因此,在切换执行环境时,同时需要改变系统的安全状态。

从非安全状态可以通过三种异常进入监控模式:

1. 执行SMC指令,SMC指令是一条特殊指令,它类似于软件中断指令(SWI),通过它来调用监控器例程; 2. 外部中止,包括预取指外部中止和数据外部中止,外部中止是在访问存储系统时发生但不会被MMU检测到的异常,通常发生在普通环境访问安全环境的资源时; 3. 中断,包括FIQ中断和IRQ中断。

其中,第一种进入监控模式的方式是无条件的,后两种情况依赖于SCR寄存器的配置。与监控模式相关的SCR寄存器各个字段的定义如下:

1> EA,默认为0,表示发生外部中止时处理器进入中止模式,如果为1,表示发生外部中止时处理器进入

监控模式;

2> IRQ,默认为0,表示发生IRQ中断时处理进入中止模式,如果为1,表示发生IRQ中断时处理器进入监

控模式;

3> FIQ,默认为0,表示发生FIQ中断时处理进入中止模式,如果为1,表示发生FIQ中断时处理器进入监 控模式。

通过以上三种异常进入监控模式都会触发监控器的异常处理程序,监控器的具体功能,是由软件开发者定义的,但执行环境的切换都是通过监控器进行的。

如果安全环境的软件在非监控模式下直接将SCR的NS位设置为1,则系统直接进入非安全状态,这使得非安全状态有了看到正在流水线的指令,以及正在寄存器中的数据的可能。如果这些指令和数据都是敏感信息的话,这将给系统带来安全威胁。因此,通常只有监控可以直接修改SCR的NS位。

2.2 对Cache和MMU的扩展

在带TrustZone安全扩展的处理器内核中,为每个tag域增加了一个NS位,用来标识这一行的安全状态。如果NS为0,则这一行处于安全态;如果NS为1,则这一行为非安全态。不管Cache行的安全状态如何,只要没被锁住,都可以被换出到主存中,为新的缓冲数据留出存储空间。处于安全状态的Cache行把处于非安全态的Cache行换出,处于非安全态的Cache行把处于安全态的Cache行换出都是可能的。

在带TrustZone安全扩展的处理器中,有两个页表基地址寄存器,不同安全状态使用不同的页表基地址寄存器,相当于有两个虚拟的MMU,每个虚拟的MMU分属不同的虚拟处理器核,这使得每个执行环境有一个本地的页表集,各个执行环境从虚地址到物理地址的转换是独立的,在切换执行环境时,不需要切换页表。

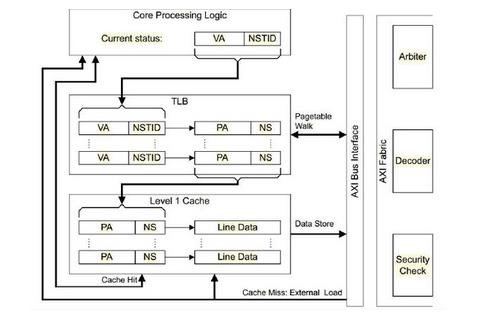

在带TrustZone安全扩展的处理器的页表项中包含一个NS标位,即非安全标识符(NSTID),如果当前系统处于非安全状态,则忽略NSTID。一般安全环境的内存页表项的NSTID设置为0,属于普通环境的内存页表项的NSTID设置为1。与此相对应,TLB也作了相应的扩展,每行的tag域也增加了一个NSTID。访问内存时需要将虚拟地址和页表中的NSTID与TLB的tag域中的虚拟地址和NSTID值进行比较。在TLB中增加的NSTID用来标志这一行是对来自哪个执行环境的虚拟地址的转换,这使得两个执行环境的地址转换数据可以同时在TLB中存在,执行环境切换时不需要刷新TLB,加快了执行环境的切换速度。

图2-3展示了带TrustZone安全扩展的ARM处理器访问存储器的过程。

1> 处理器执行访存指令,硬件将虚拟地址以及NSTID给TLB,使它产生一次地址转换;

2> TLB将虚拟地址和NSTID与TLB各行tag域中的虚拟地址和NSTID值进行比较,如果匹配则加载与虚拟地址和NSTID对应的物理地址和NS值;如果没有找到匹配项,则由MMU查找页表,并将查找结果缓存到TLB中。如果当前系统处于非安全状态,在将MMU页表查找结果缓存到TLB中时,必须强制NS为1,如果当前系统处于安全状态,NS的值取决于NSTID的值。

3> Cache行的tag与来自TLB的物理地址与NS进行匹配,如果匹配成功,将从Cache行中返回数据,否则从外部存储系统中加载Cache行。

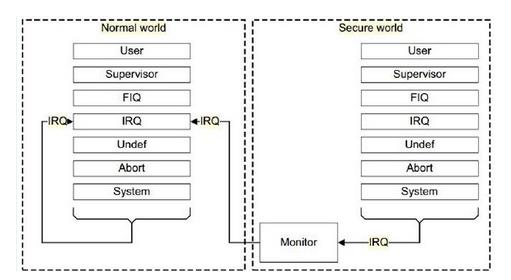

2.3安全中断

监控器有在没有任何执行环境的代码帮助下就能够直接捕获FIQ和IRQ的能力,这可以为安全中断源创建一个灵活的中断模型。当执行流到达监控器的时候,监控器能够将中断请求路由到相应的中断处理程序,如果和安全中断控制器结合起来就可以让安全中断源发出的中断不能被普通环境软件操作。

ARM推荐使用IRQ作为普通的环境中断源,FIQ作为安全环境中断源。大多数的操作系统都采用IRQ作为中断源,所以采用FIQ作为安全中断源意味着对普通环境操作系统的改动最少。如果中断发生在相应的执行环境,则不需要进行执行环境的切换,否则陷入到监控器中,由监控器切换执行环境。一般情况下,执行监控器代码的时候应该关中断。

为了防止普通环境的恶意软件屏蔽掉安全环境的中断,在CP15协处理器中包含了一个配置寄存器,能够用来阻止普通环境软件修改CPSR的F位(FIQmask)和A位(externalabortmask)。这个控制寄存器只能够被安全环境的软件访问。当然,普通环境有屏蔽IRQ中断的权利。

2.3.1TrustZone异常向量表

在带TrustZone安全扩展的处理器带有三个异常向量表,一个是普通环境的异常向量表,一个是安全环境的异常向量表,还有一个是监控器的异常向量表。

在系统开机时,安全环境的异常向量表的基地址取决于处理器输入信号VINITHI,如果该信号是低电平,则异常向量表的基地址为低地址,记0x00000000,如果该信号是高电平,则异常向量表的基地址为高,即0xffff0000。其它向量表的基地址在开机的时候是未定义的,在使用前必须由软件设置。

与以前的普通ARM处理器不同,每个异常向量表的位置在运行时可以动态地移动,只需要将新的异常向量表基地址写入到CP15协处理器的向量基地址寄存器(VBAR)就能完成。

普通环境和安全环境异常向量表基地址除了与向量基地址寄存器有关外,还与处理器控制器的V位有关。如果V位被设置了,则异常向量表基地址采用高地址,而与VBAR无关。安全状态下和非安全状态下的V位是独立的,这使得安全环境和普通环境可以独立的设置向量表基地址是否采用高地址。V位只是用于安全环境和普通环境,监控器的异常向量表的基地址有监控器的异常向量表基地址寄存器指定。

2.3.2TrustZone中断控制器

TrustZone的中断控制器(TZIC)用来配置和截获安全中断源的中断信号,为安全中断系统提供软件接口。可以将TZIC与传统的向量中断控制器(VIC)通过菊花链的方式连接组成两级中断控制系统,完成普通中断与安全中断的隔离。TZIC是第一级中断控制器,所有中断源的中断请求都是连接在TZIC上的,它最先截获设备的中断请求。通过对TZIC的TZICIntSelect寄存器进行编程,可以对中断源产生的中断类型进行设置。如果TZICIntSelect中的某一位为1,则相应中断源的中断请求被配置为FIQ中断,如果为0,则该中断源的中断请求将交由第二级中断控制器VIC处理。凡是由TZICIntSelect配置为FIQ中断的中断源提出的中断请求都将绕过VIC而直接交由TZIC处理,经过TZIC的中断屏蔽和中断判优后向处理器提出中断请求。没有被TZICIntSelect设置为FIQ中断的中断源具体会被设置为FIQ还是IRQ这将由VIC的VICIntSelect寄存器来决定了,当然一般情况下应该配置为IRQ,如果被配置为FIQ,中断请求又将被反馈给TZIC。TZICIntSelect寄存器的复位值为0,也就是说默认所有的中断都交给VIC处理,这样对不支持TrustZone的系统来说,可以把TZIC看作是完全透明的。

2.3.3外设保护

APB总线没有与AXI那样的与TrustZone安全状态相关的控制信号,因此不需要改变原有的外设设计,可以直接将原有外设连接到APB总线上。APB总线上的外设的安全由AXI-to-APB桥来负责,AXI-to-APB桥既提供了AXI总线接口由提供APB总线接口。

AXI-to-APB桥包含了地址解码逻辑,用来在AXI总线发出一个事务的时候选中相应的外设。AXI-to-APB桥包含了一个TZPCDECPORT输入信号,对应于每个总线上的外设。这个信号用来决定外设是配置为安全的还是非安全的,AXI-to-APB桥会拒绝非安全事务访问安全外设。TZPCDECPORT输入信号可以在SoC设计时静态地设置,也可以通过对TrustZone保护控制器(TZPC)进行编程,在程序运行时动态地设置。

图2-5展示了一个AXI-to-APB桥控制了4个外设,TZPC的安全状态是在SoC设计时确定的,它被设置为安全设备,只能被安全的软件环境使用。定时器和实时时钟在SoC设计时被设置为非安全的,键盘和鼠标接口的安装状态是可以动态改变的。安全环境的软件可以在运行时对TZPC进行编程,来改变输入到AXI-to-APB桥的信号,从而将键盘鼠标接口在安全和非安全之间切换。这样设计使得外设大部分时间都处于非安全状态,可以被普通环境使用。然后又可以将他们短暂地切换到安全状态,成为安全环境的设备。比如键盘,通常情况下都被用于普通环境,但是需要在安全环境下输入密码的时候又可以将其设置为安全设备。

2.3.4安全处理器配置

ARM协处理器附属于ARM处理器,一个协处理器通过扩展指令集或者提供配置寄存器来扩展内核的功能。其中最重要的协处理器是CP15协处理器,用来控制Cache、TCM和存储器管理。协处理器的某些寄存器是有备份的,也就是普通环境和安全环境各有一个这样的寄存器。对这种能够寄存器的修改,只会对它所在执行环境起作用。有的协处理器是没有备份的,对它的修改影响到全局,比如说控制对Cache进行锁定操作的寄存器。对这种寄存器的访问必须严格控制,一般只对安全环境提供读写权限,而普通环境只能读取。

ARM提供了一个非安全访问控制寄存器(NSACR)来配置非安全执行环境下对那些具有全局影响的协处理器的访问权限。NSACR的各字段定义如下:

1> CP0-CP13(13:0):控制相应的协处理器的访问权限,如果为0,则只能被安全环境访问,如果为1,则安全环境和普通环境都可以访问。

2> CL(16):ARM内核可以为Cache锁定分配固定的Cache单元,CL用来确定普通环境下是否有权限在L2Cache中分配Cache锁定单元,默认为0,即普通环境不能在L2中执行Cache锁定操作。

3> TL(17):TLB的地址转换时数据可以被锁定,如果某一行被锁定,则当执行TLB清除指令时,它仍然保留在TLB中。TL字段用来确定在普通环境下是否有权限执行TLB锁定操作。默认情况下为0,即不执行TLB锁定操作。

4> PLE(18):用来决定普通环境下是否有权限访问PLE寄存器,默认为0,即不能访问PLE寄存器。

2.4系统IP支持

安全性是整个系统的属性,而不仅仅是某个组件的属性,采用TrustZone技术可更加轻松对系统进行分区,以确保安全,同时保持对安全子系统的硬件支持保护。使用TrustZone技术设计安全子系统不仅需要支持TrustZone技术的处理器内核,还需要总线构造、安全内存和安全外设。ARM可提供众多构造和外设组件,以提供安全子系统的基础。

第2章TrustZone软件结构

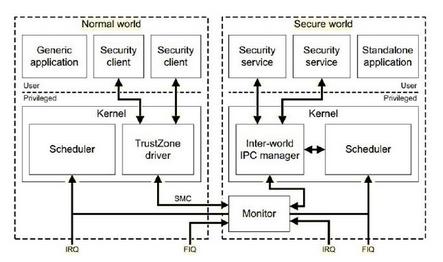

在SoC硬件中实现安全区域要求在其中运行某些安全软件,并利用存储在其中的敏感资产。 可能有许多支持TrustZone的处理器内核上的安全区域软件堆栈可实现的软件架构。最高级的软件架构是专用安全区域操作系统;最简单的是放置在安全区域的同步代码库。这两个极端架构之间有许多中间选项。

1 安全内核

专用安全内核可能是一种复杂但强大的设计。它可以模拟多个独立安全区域应用程序的并发执行、新安全应用程序的运行时下载以及完全与普通区域环境独立的安全域任务。

这些设计与将在SoC中看到的软件堆栈非常类似,它们在非对称多处理(AMP)配置中使用两个单独的物理处理器。在每个虚拟处理器上运行的软件是独立的操作系统,并且每个区域使用硬件中断来抢占当前运行的区域和获得处理器时间。

使用将安全区域任务与请求这些任务的普通区域威胁相关联的通信协议的紧密集成设计可提供对称多处理(SMP)设计的许多优点。例如,在这些设计中,安全区域应用程序可继承它支持的普通区域任务的优先级。这将导致对媒体应用程序做出某些形式的软实时响应。安全扩展是ARM架构的开放式组件,因此任何开发人员都可创建自定义安全区域软件环境,以满足其要求。

由于实现安全操作系统实际上非常复杂,并且可能需要验证其功能,因此许多合作伙伴倾向于与此领域中的专业公司(如Gieseke&Devrient或TrustedLogic)进行合作。

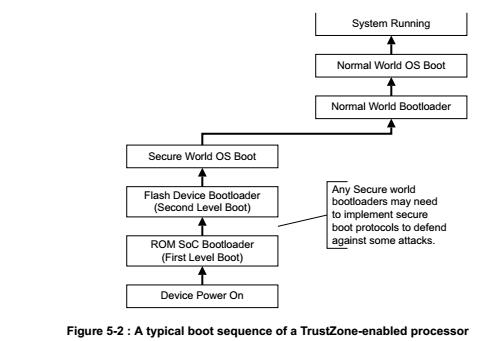

2 安全系统启动

设备上电时,带TrustZone的处理器会在安全环境中启动。这样使得在普通环境有机会修改系统之前进行一次敏感的安全核查。典型的启动流程如图2所示。

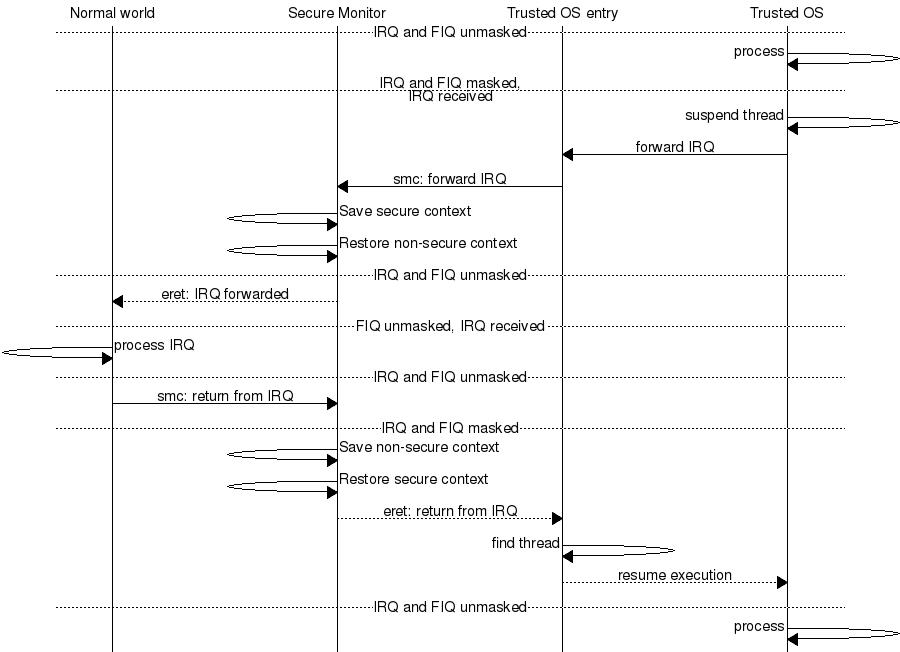

3 中断响应切换模式处理过程

处在安全世界下,收到IRQ中断:

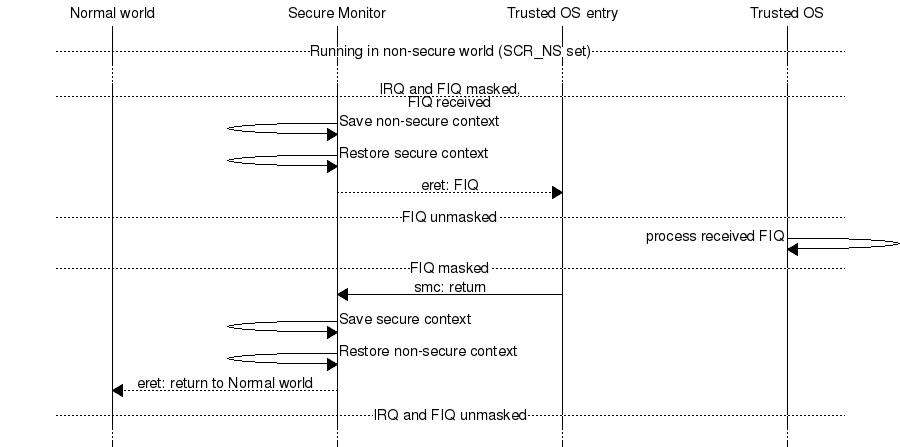

处在非安全世界下,收到FIQ中断:

以上是关于TrustZone软硬件架构的主要内容,如果未能解决你的问题,请参考以下文章