FPGA学习笔记之 ADC_549模块

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA学习笔记之 ADC_549模块相关的知识,希望对你有一定的参考价值。

1.ADC_549模块的时序知识.

2.ADC_549模块的核心代码.

3.ADC_549模块的使用.

===================================================================================

1.ADC_549模块的时序知识.

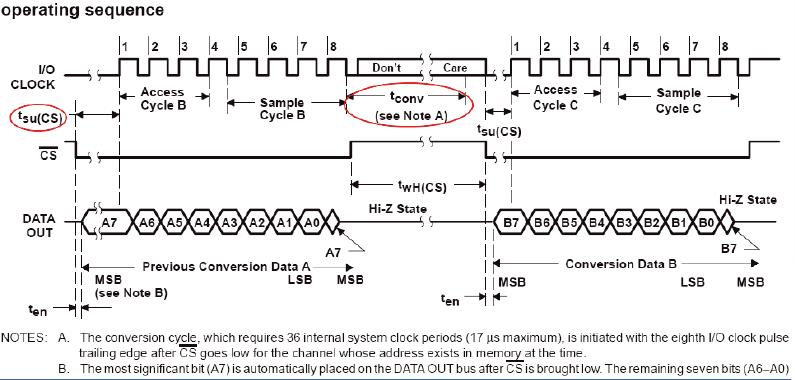

(1)时序图

从上面的红色画圈的地方是我们总结出的几个需要重点注意的地方:

1. CS 有效时(低),需要等待1.4us才可以读取第一位数据

2. 连续读完8位数据后需要等待17us的时间才可以进行下一次数据的读取,这段时间就是AD芯片内部进行模数转换的时间.

3.数据的读取要在每个ADC_CLK的上升沿.

--------------------------------------------------------------------------------------------------------------------------

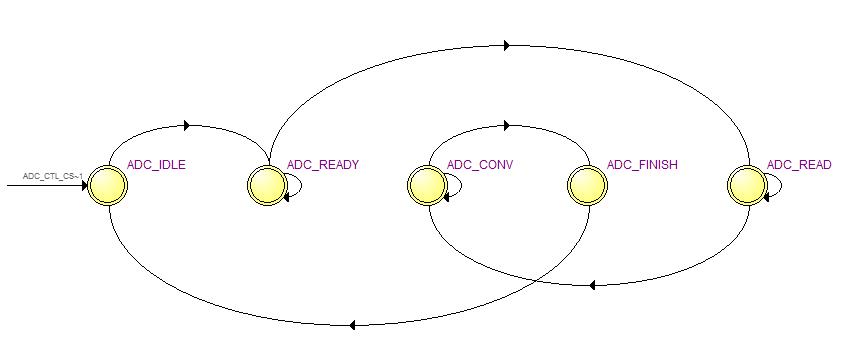

(2)状态转换图

(1)ADC_IDLE 状态是一个初始状态.

(2)ADC_READY 是我们为了满足CS有效时的第一个1.4us的延期状态.

(3)ADC_READ 是读ADC转换后数据的状态,8个时钟的上升沿逐位移入ADC数据线上的8位串行数据.

(4)ADC_CONV 是ADC正在转换数据需要消耗的时间,是17us,请看datasheet中的时序图.

(5)ADC_FINISH 是ADC驱动结束的状态标志.

=============================================================================================

2.ADC_549模块的核心代码.

ADC_549的核心代码涉及三大部分:状态机、输出引脚的控制、内部逻辑部分

(1)状态机

//ADC_549状态机 `define ADC_CLK_TIME 10‘h15 `define ADC_READY_TIME 10‘h31 `define ADC_CONV_TIME 10‘h360 always @ (posedge SYSCLK or negedge RST_B) begin if(!RST_B) ADC_CTL_CS <= `UD ADC_IDLE; else ADC_CTL_CS <= `UD ADC_CTL_NS; end always @ (*) begin case(ADC_CTL_CS) ADC_IDLE : ADC_CTL_NS = ADC_READY; ADC_READY : if(TIME_CNT == `ADC_READY_TIME) //改变宏定义中的部分可以改变延时的长度 ADC_CTL_NS = ADC_READ; else ADC_CTL_NS = ADC_CTL_CS; ADC_READ : if((BIT_CNT == 4‘h8) && (!ADC_CLK) &&(TIME_CNT == `ADC_CLK_TIME)) ADC_CTL_NS = ADC_CONV; else ADC_CTL_NS = ADC_CTL_CS; ADC_CONV : if(TIME_CNT == `ADC_CONV_TIME) ADC_CTL_NS = ADC_FINISH; else ADC_CTL_NS = ADC_CTL_CS; ADC_FINISH : ADC_CTL_NS = ADC_IDLE; default : ADC_CTL_NS = ADC_IDLE; endcase end

(2)输出引脚的控制

//ADC_CS always @ (posedge SYSCLK or negedge RST_B) begin if(!RST_B) ADC_CS <= `UD 1‘h1; else ADC_CS <= `UD ADC_CS_N; end always @ (*) begin if(ADC_CTL_CS == ADC_READY) ADC_CS_N = 1‘h0; else if(ADC_CTL_CS == ADC_CONV) ADC_CS_N = 1‘h1; else ADC_CS_N = ADC_CS; end //ADC_CLK always @ (posedge SYSCLK or negedge RST_B) begin if(!RST_B) ADC_CLK <= `UD 1‘h0; else ADC_CLK <= `UD ADC_CLK_N; end always @ (*) begin if((BIT_CNT == 4‘h8) && (!ADC_CLK)) ADC_CLK_N = 1‘h0; else if((ADC_CTL_CS == ADC_READ) && (!ADC_CLK) && (TIME_CNT == `ADC_CLK_TIME)) //这里ADC_CTL_CS == ADC_READ与TIME_CNT == `ADC_CLK_TIME相差一个系统时钟周期,不可能同时出现 ADC_CLK_N = 1‘h1; else if((ADC_CTL_CS == ADC_READ) && (ADC_CLK) && (TIME_CNT == `ADC_CLK_TIME)) ADC_CLK_N = 1‘h0; else ADC_CLK_N = ADC_CLK; end //SEND_FINISH; assign ADC_NEW = (ADC_CTL_CS == ADC_FINISH); assign ADC_DATA = SHIFT_REG;

(3)内部逻辑控制

//Some control singal. //First,time count. always @ (posedge SYSCLK or negedge RST_B) begin if(!RST_B) TIME_CNT <= `UD 10‘h0; else TIME_CNT <= `UD TIME_CNT_N; end always @ (*) begin if(ADC_CS != ADC_CS_N) //****这部分比较难**** TIME_CNT_N = 10‘h0; else if(ADC_CLK != ADC_CLK_N) TIME_CNT_N = 10‘h0; else if(ADC_CTL_CS != ADC_CTL_NS) TIME_CNT_N = 10‘h0; else TIME_CNT_N = TIME_CNT + 10‘h1; end //Second, bit count, 12bit of all. always @ (posedge SYSCLK or negedge RST_B) begin if(!RST_B) BIT_CNT <= `UD 4‘h0; else BIT_CNT <= `UD BIT_CNT_N; end always @ (*) begin if(ADC_CTL_CS == ADC_FINISH) BIT_CNT_N = 4‘h0; else if((!ADC_CLK) && (ADC_CLK_N)) //这个就是很典型的ADC_CLK上升沿出现的条件 BIT_CNT_N = BIT_CNT + 4‘h1; else BIT_CNT_N = BIT_CNT; end //移位寄存器,存储每个ADC_CLK上升沿到来时ADC传来的数据 always @ (posedge SYSCLK or negedge RST_B) begin if(!RST_B) SHIFT_REG <= `UD 8‘h0; else SHIFT_REG <= `UD SHIFT_REG_N; end always @ (*) begin if((!ADC_CLK) && (ADC_CLK_N)) SHIFT_REG_N = {SHIFT_REG[6:0] , ADC_DAT}; //移位寄存的核心代码 else SHIFT_REG_N = SHIFT_REG; end

ADC_549驱动模块代码特点:

1.类SPI通信模块,基本的SPI通信都与此类似.

2.也只用一个变量TIME_CNT来安排每个状态的长度,但是与串口通信的区别是,串口通信的状态转换条件BAUD_RATE都是步调一致,跨度一致,而SPI的状态长度可以自己使用宏定义,不过涉及到位数的都会使用一个BIT_CNT的变量

3.涉及到的变量:(内部)状态机ADC_CTL_CS、状态长度TIME_CNT、数据位数BIT_CNT、移位寄存器SHIFT_REG

(输出)ADC数据驱动时钟ADC_CLK、ADC数据获取使能端ADC_CS

=================================================================================

3.ADC_549模块的使用.

添加ADC_549模块的V文件,并在要使用此模块的工程中添加代码

//Instance TLC549 controller. ADC_549_CTL I_ADC_549_CTL ( .SYSCLK (SYSCLK), .RST_B (RST_B), .ADC_CLK (ADC_CLK), .ADC_DAT (ADC_DAT), .ADC_CS (ADC_CS), .ADC_DATA (ADC_DATA), //这里是ADC采集来的数据,不过要加一个带使能端的二选一选择器才能得到正确AD数据,使能端接ADC_NEW .ADC_NEW (ADC_NEW) );

至此完成ADC_549驱动模块的编写.

以上是关于FPGA学习笔记之 ADC_549模块的主要内容,如果未能解决你的问题,请参考以下文章