数字电路中时序

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字电路中时序相关的知识,希望对你有一定的参考价值。

读时序图方法

1、从上到下,从左到右,高电平在上,低电平在下,高阻态在中间。双线表示可能高也可能低,视数据而定。交叉线表示状态的高低变化点,可以是高变低,也可以是低变高,也可以不变。

2、竖线是生命线,代表时序图的对象在一段时期内的存在,时序图中每个对象和底部中心都有一条垂直段的虚线,这就是对象的生命线,对象的消息存在于两条生命线之间。

3、时序要满足建立时间和保持时间的约束才能保证锁存到正确的地址。数据或地址线的时序图画0/1两条线,表示是一个固定的电平,可能是“0”,也可能是“1”,视具体的地址或数据而定;交叉的线表示电平变化,状态不确定,数值无意义。

如:

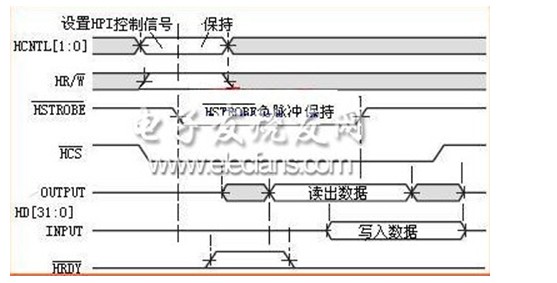

HCNTL,HR/W阴影部分表示不相关的数据周期,非阴影区为有效稳定数据区,交叉线为数据变化时间点.

纵向的最长虚线为数据及控制信号的采集参考点,即HSTROBE的下降沿采样

对OUTPUT的读出数据而言,其阴影及非阴影区均为读出数据时间周期,不同的是阴影区表示非稳定期,而非阴影区表示数据稳定有效期,可以在此刻采样读有效数据.OUTPUT中间横线表示数据高阻态.

以上是关于数字电路中时序的主要内容,如果未能解决你的问题,请参考以下文章