可测性设计-扫描通路

Posted hippomyl

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了可测性设计-扫描通路相关的知识,希望对你有一定的参考价值。

1、问题:扫描测试的原理

扫描测试的两个目的:

1、实现对组合逻辑电路输入的控制。

2、对组合逻辑电路的输出进行观察。

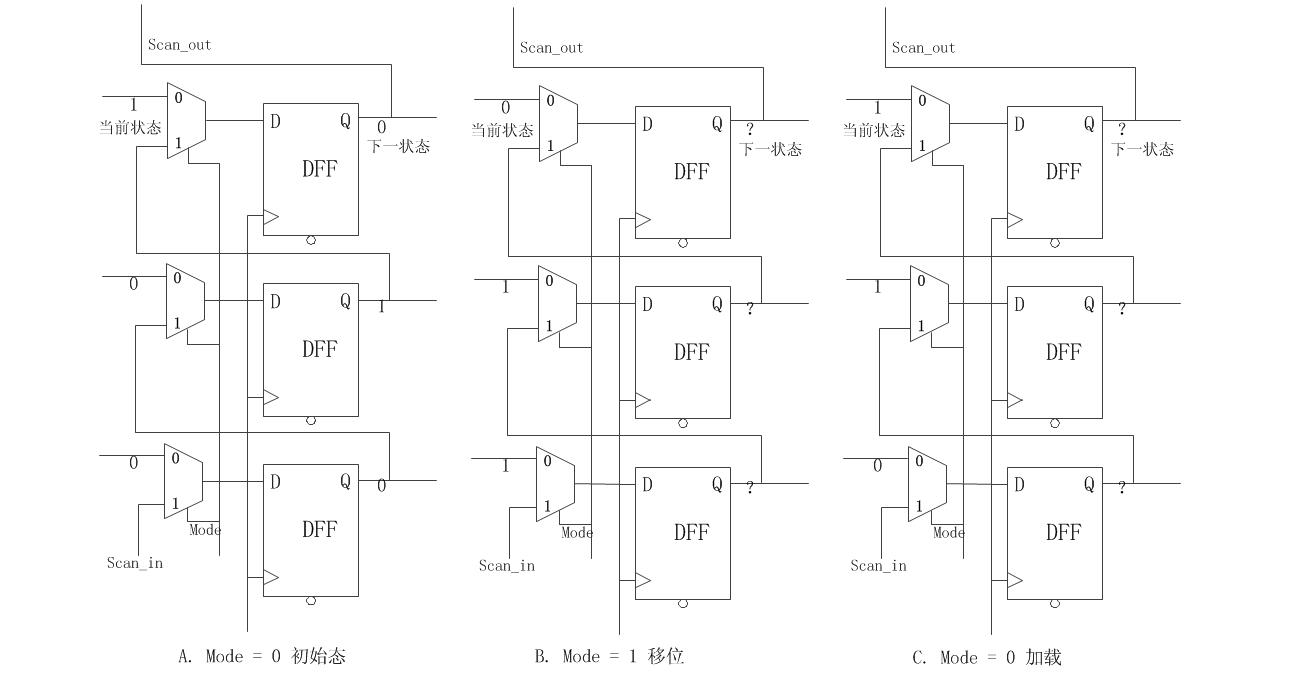

如图所示:当前状态即寄存器的输出,一般直接接到组合逻辑的输入端口,通过对寄存器扫描特定的数值,即可完成对组合电路输入的控制。

同时,当前的组合逻辑的输出也接到寄存器的输入端口,在测试数据施加之前,有必要将当前的输出扫描出来。

整个扫描测试分为三部分:

A. Mode = 0,执行一次扫描操作,将100(组合电路的结果)扫描到寄存器中。

B. Mode = 1,执行三次扫描操作,将测试模板110扫描到寄存器中,同时将上一次的结果(100)扫描出来。

C.Mode = 0,电路进入工作模式,此时即完成对组合逻辑输入的控制。

以上是关于可测性设计-扫描通路的主要内容,如果未能解决你的问题,请参考以下文章