APB总线协议

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了APB总线协议相关的知识,希望对你有一定的参考价值。

参考技术A https://www.cnblogs.com/lyuyangly/p/4853921.htmlhttps://blog.csdn.net/u011280717/article/details/81052436

APB主要用来连接高性能低带宽的外围设备,在APB总线系统中, 只有一个master,其他的都是slave 。

特点:

① 可工作在高频下 ;

② 协议简单 :无复杂的时序;

③ 同步总线 :总线上所有的transaction(读写操作)都依赖于时钟的上升沿;

④ 一主多从 :一般情况下,APB挂在AHB总线系统下,通过AHB-APB Bridge将事务在AHB总线系统之间进行转化,此时Bridgre即为APB的master,其他的外围设备均为slave。

⑤ 接口简单 :相对应AXI、AHB来说,接口比较简单;

⑥ 低功耗

⑦ 可连接多种外围设备 :I2C、SPI、Timer、Keypad、UART

它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。

APB上的传输可用如图所示的状态图来说明。

1、IDLE: 系统初始化状态,此时没有传输操作,也没有选中任何从模块。

2、SETUP: 启动状态,当有传输要进行时,PSELx=1,,PENABLE=0,系统进入SETUP状态,并只会在SETUP状态 停留一个周期 。当PCLK的下一个上升沿到来时,系统进入ENABLE状态。

3、ENABLE: 在总线进入SETUP状态的下一个时钟上升沿处,需将PENABLE信号拉高进入ENABLE状态。在这个上升处,master必须保持PADDR、PSEL、PWRITE不变。传输也只会在ENABLE状态 维持一个周期 ,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

T2: 上升沿后,master将选择信号PSEL拉高,同时将地址信号PADDR,读写控制信号PWRITE,以及写数据PWDATA驱动到总线上。此时总线开始进入SETUP状态。

T3: master将PENABLE信号拉高,切保持PADDR、PWRITE、PSEL线上的信号稳定不变。总线进入ENABLE状态。slave在这个上升沿处将地址信号和读写使能信号采样下来(slave会不断检测这些信号,t3发现PSEL为高,采样PADDR和PWRITE,判断是读还是写,在t4采数据)。

T4: slave从PWDATA线上采样数据,写操作完成。之后将PSEL和PENABLE拉低,其他信号保持不变。

( 也可以在T3采PWDATA )

写逻辑推荐写法:

1 assign wr = psel & pwrite & (penable);

2 always @(posedge pclk or negege present)

3 begin

4 if(!presetn)

5 begin

6 REG_A <= 32’h0;

7 end

8 else if(wr & paddr = REG_A_ID) //T3之后

9 begin

10 REG_A <= pwdata;

11 end

12 end

T2: 同写操作

T3: 同写操作

T3上升沿过后: 对应的slave要将读取的数据驱动到PRDATA线上,并且保持稳定。

T4: master从PRDATA线上采数据,读操作完成。之后将PSEL和PENABLE拉低,其他信号保持不变。

( 不可以在T3采PWDATA )

写操作:T2-T4之间,PADDR, PWRTE, PSEL, PWDATA一定保持不变。

读操作:T2-T4之间,PADDR, PWRTE, PSEL,一定保持不变。

T3-T4之间,PRDATA保持不变。

读逻辑推荐写法:

1 assign rd = psel & (~pwrite) & (~penable) ;

2 always @(*)

3 begin

4 if(rd) //setup

5 begin

6 case(paddr)

7 REG_A_ID : prdatanxt = REG_A;

8 REG_B_ID : prdatanxt = REG_B;

9 ……

10 default : prdatanxt = 32’h0;

11 endcase

12 end

13 else

14 begin

15 prdatanxt = 32’h0;

16 end

17 end

18 always @(posedge pclk or negege present)

19 begin

20 if(!presetn)

21 begin

22 prdata <= 32’h0;

23 end

24 else begin

25 prdata <=prdatanxt;

26 End

27 end

AMBA总线协议AHBAPB

一、什么是AMBA总线

AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。

二、AHB

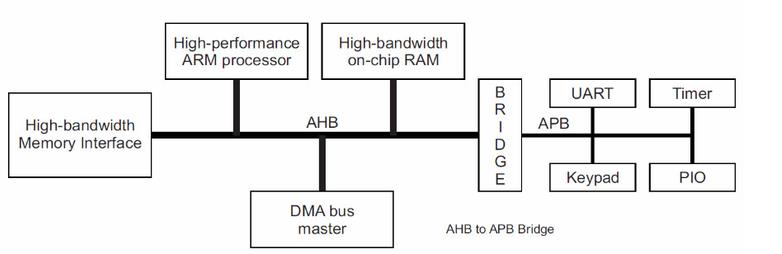

AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完整独立的SOC芯片的骨架。

下图是一个典型的AHB系统总线的结构示意图

三、APB

主要应用在低带宽的外设上,如UART、 I2C,它的架构不像AHB总线是多主设备的架构,APB总线的唯一主设备是APB桥(与AXI或APB相连),因此不需要仲裁一些Request/grant信号。APB的协议也十分简单,甚至不是流水的操作,固定两个时钟周期完成一次读或写的操作。其特性包括:两个时钟周期传输,无需等待周期和回应信号,控制逻辑简单,只有四个控制信号。APB上的传输可用如图所示的状态图来说明。

1、系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

2、当有传输要进行时,PSELx=1,,PENABLE=0,系统进入SETUP状态,并只会在SETUP状态停留一个周期。当PCLK的下一个上升沿到来时,系统进入ENABLE状态。

3、系统进入ENABLE状态时,维持之前在SETUP状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

以上是关于APB总线协议的主要内容,如果未能解决你的问题,请参考以下文章