竞争与冒险——随笔

Posted IC_learner

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了竞争与冒险——随笔相关的知识,希望对你有一定的参考价值。

(1)竞争与冒险的概念(产生原因)

①信号在组合逻辑电路内部通过连线和逻辑单元时,都有一定的延时。延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。此外,信号的高低电平转换也需要一定的过渡时间。由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,这种现象叫做竞争。

由于竞争往往会出现一些不正确的尖峰信号,这些尖峰信号称为“毛刺”。 如果一个组合逻辑电路中有“毛刺”出现,就说明该电路存在“冒险”。

②冒险信号的脉冲宽度很小,常常只有数纳秒或数十纳秒,其频带带宽可达数百兆赫兹或更宽。在板级调试时,如果示波器的上限频率较低,会将幅度较大的毛刺显示为幅度较小的毛刺,甚至不易被察觉。

③冒险按产生形式的不同可以分为静态冒险和动态冒险两大类。

·静态冒险是指输入有变化,而输出不应变化时产生的单个窄脉冲;

·动态冒险则指的是输入变化时,输出也应变化时产生的冒险。

动态冒险是由静态冒险引起的,因此存在动态冒险的电路也存在静态冒险。

④静态冒险根据产生条件的不同,分为功能冒险和逻辑冒险两大类。

·当有两个或两个以上输入信号同时产生变化时,在输出端产生毛刺,这种冒险称为功能冒险。

·如果只有一个变量产生变化时出现的冒险则是逻辑冒险。

冒险往往会影响到逻辑电路的稳定性,因此要注意冒险的消除。

(2)静态冒险产生的判断

①判断一个逻辑电路在某些输入信号发生变化时是否会产生冒险,首先要判断信号是否会同时变化,然后判断在信号同时变化的时候,是否会产生冒险,这可以通过逻辑函数的卡诺图或逻辑函数表达式来进行判断。

②功能冒险的检查

功能冒险是由电路的逻辑功能引起的,只要输入信号不是按照循环码的规律变化,组合逻辑就可能产生功能冒险,且不能通过修改设计加以消除,只能通过对输出采用时钟采样来消除。

③逻辑冒险的检查

检查电路是否产生逻辑冒险的方法有两种:代数法和卡诺图法。

代数法:

如果一个组合逻辑函数表达式 F,在某些条件下能化简成F = A+ A或F = AA的形式,在A 产生变化时,就可能产生静态逻辑冒险。

卡诺图法:

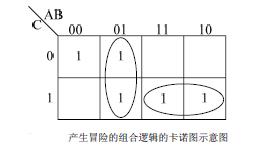

在组合逻辑的卡诺图中,若存在素项圈相切,则可能会产生逻辑冒险,如下图所示的卡诺图中,AC 和AB两个素项环相切,在B = C = 1时,A 由1 变为0 时,将产生逻辑冒险:

(3)毛刺的消除

毛刺并不是对所有的输入都有危害,例如D 触发器的D 输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,我们可以说D 触发器的D 输入端对毛刺不敏感。

根据这个特性,我们应当在系统中尽可能采用同步电路,这是因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害。(由于毛刺很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间)因此我们可以通过改变设计,破坏毛刺产生的条件,来减少毛刺的发生。

例如,在数字电路设计中,常常采用格雷码计数器取代普通的二进制计数器,这是因为格雷码计数器的输出每次只有一位跳变,消除了竞争冒险的发生条件,避免了毛刺的产生。

目前,主要有两种基本的采样方法:脉冲选择法和时序逻辑保持法。

①脉冲选择法

该方法在输出信号的保持时间内,用一定宽度的高电平脉冲与输出信号做逻辑“与”运算,由此获取输出信号的电平值。

这种方法大大减少毛刺,但它并不能完全消除毛刺,我们通常使用“采样”的方法。一般说来,冒险出现在信号发生电平转换的时刻,也就是说在输出信号的建立时间内会发生冒险,而在输出信号的保持时间内是不会有毛刺信号出现的。如果在输出信号的保持时间内对其进行“采样”,就可以消除毛刺信号的影响。但是这种方法必须产生在合适的时候产生高电平,因此有一定的难度。

②时序逻辑保持法

其利用D 触发器的D 输入端对毛刺信号不敏感的特点,在输出信号的保持时间内,用触发器读取组合逻辑的输出信号,这种方法类似于将异步电路转化为同步电路。举例如下:

1 module maoxian( 2 input clk, 3 input A, B, C, D, 4 output reg Out, 5 output Tout 6 ); 7 8 wire aandb, candd, tmp; 9 10 assign aandb = A && B; 11 assign candd = C && D; 12 assign tmp = aandb || candd; 13 14 15 always @(posedge clk) begin 16 Out <= tmp; 17 end 18 19 assign Tout = tmp; 20 21 endmodule

以上是关于竞争与冒险——随笔的主要内容,如果未能解决你的问题,请参考以下文章