verilog task1

Posted hippomyl

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog task1相关的知识,希望对你有一定的参考价值。

问题描述:

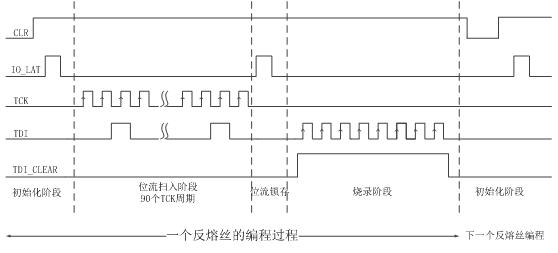

设计中需要重复多次施加一种激励,每一次激励的施加过程,都可以划分为4个部分,如图所示。

每一次施加的激励只有第二部分的数据有变化(数据格式无变化)。所以顶层的Testbench代码如下:

1 reg [4:0] j; 2 task bian_chen; 3 begin 4 for(j=0;j<=27;j=j+1)begin 5 initial_task(); 6 send_weiliu(j); 7 latch_weiliu(); 8 shaolu(); 9 end 10 end 11 endtask

第二部分中有90位数据需要发送,首先申明变量存储数据,如下所述:

1 reg [90:0] TDI_REG [0:27]; 2 initial begin 3 $readmemb("weiliu.dat",TDI_REG); 4 end

第二部分数据发送的具体实现,如下所示:

1 task send_weiliu; 2 input [4:0] num; 3 begin 4 fork 5 TCK_gen(); 6 TDI_weiliu(num); 7 join 8 end 9 endtask 10 11 task TCK_gen; 12 begin 13 TCK = 1‘b0; 14 repeat(182) #5 TCK = ~TCK; 15 #5 TCK = 1‘b0; 16 end 17 endtask 18 19 reg [6:0] i; 20 task TDI_weiliu; 21 input [4:0] n; 22 begin 23 for(i=90;i>=0;i=i-1)begin 24 @(negedge TCK); 25 TDI = TDI_REG[n][i]; 26 end 27 end 28 endtask

说明:

1)位流数据在时钟上升沿被采样进入编程链寄存器中,所以需要在时钟下降沿处产生好要发送的数据。(见代码24行25行。)

2)由于编程链是按照D01到D90的顺序串接的,所以最高的D90的位流数据应该最先发送。

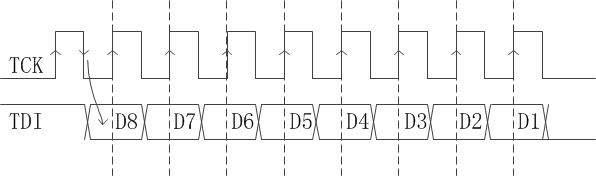

3)由于数据先要在下降沿产生,再在下一个上升沿到来时被采样,所以产生的TCK的数目为182,而非180。同时在TCK的第一次上升延处,由于TDI数据是无效的(还没产生),所以位流文件也要额外的附加一位,位流文件是91位,最高位第91位时无效的。下面通过一个简单时序波形理解这种情形。如下图:

图2-1

图2-1中,要发送8位数据D8-D1,TCK信号需要翻转2x8+2=18次,第一个上升沿发送无效数据,第一个下降沿处,产生数据D8。

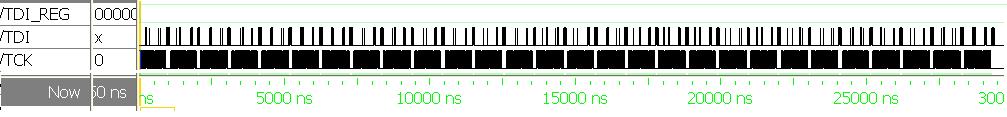

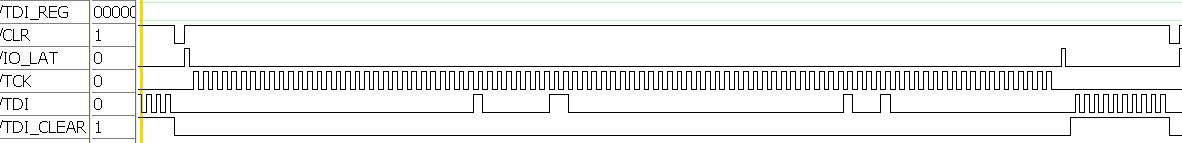

仿真结果:

上图所示,为多28次数据发送过程的仿真波形图。

上图所示,为多每一次数据发送过程的仿真波形图。

总结:

1.用verilog 写Testbench时,本文介绍的,数据的发送过程中TDI、TCk的产生方式值得借鉴。如在模拟键盘的时钟与数据时可以用到。

fork TCK_gen(); TDI_weiliu(num); join

2.熟悉了for 循环处理重复性工作的用法,特别是语法。

以上是关于verilog task1的主要内容,如果未能解决你的问题,请参考以下文章