usb2.0高速视频采集之68013A寄存器配置说明

Posted 层层惊涛

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了usb2.0高速视频采集之68013A寄存器配置说明相关的知识,希望对你有一定的参考价值。

任何的固件编程离不开与与原理图参考,图纸中所采用的是USB的Slave_fifo传输方式,具体配置与图纸对应即可。

•USB_IFCLK:同步Slave_FIFO模式,输入频率范围5M-48M,在FPGA内部将此信号配置为CMOS摄头cmos_pclk,传感器像素时钟的输出端,作为数据采集时钟和 68013与FPGA通信的同步时钟。

assign USB_Data = cmos_data;

•FLAGA/FLAGB/FLAGC/FLAGB:对应FX2LP输出的FIFO状态信息。在写入FIFO或者 读FIFO之前,需先判断FIFO内部满、空等。

•SLCS:FIFO的片选信号,外部逻辑控制,当SLCS无效时,不可进行数据传输。

•SLOE:FIFO的输出使能,外部逻辑控制,当SLOE无效时,数据线不输出有效数据。

•SLRD:FIFO读信号,外部逻辑控制,控制读FIFO。

•USB_WR:FIFO写信号,外部逻辑控制,同步写时,在SLWR有效时的每个IFCLK的上 升沿数据被写入,FIFO指针递增。

assign USB_WR = i2c_config_done & cmos_href & USB_Trigger

USB_WR在CMOS摄像头配置完成,CMOS传感器数据行同步信号和USB_Trigger均有效时,允许写入FIFO操作。

•USB_PA0:外部中断信号。通过CMOS_VSYNC信号来触发中断。该信号是CMOS传感 器像素数据场同步信号输出。代表每帧图像输入的结束,下一帧图像输入的开始。

•USB_FD[0..7]:8位数据传输位。在FPGA内部,将此信号直接连接至传感器像素的输出。

assign USB_Data = cmos_data;//cmos_data为传感器像素时钟输出数据位,8位。

•FIFOADR0/FIFOADR1:选择四个FIFO端点的地址线,外部逻辑控制。68013内部有四个FIFO。

•PKTEND:包结束信号。正常情况下,外部逻辑像FIFO中写入数据时,当写入FIFO端点 的字节数等于固件设定的包大小时,数据将自动打包传输。但外部逻辑传输小数设定的 包大小时,只需在写入一定数目字节后,使PKTEND信号有效,无论外部逻辑写入多 少自己,将自动打包传输。在固件当中,设置PKTEND低有效,此处直接进行拉高处 理,说明每次传输只能固定数据包大小传输。

二、USB68013固件程序解读

首先简要介绍下CYPRESS提供的固件编程框架,用户只需要在我们提供的框架基础上添加修改少量的代码,即可完成固件的编程。框架内部提供了钩子函数,用户在钩子函数中添加自己的代码,完成编程。

固件复位上电时,先初始化一些全局变量,接着调用初始化钩子函数TD_Init(),开中断,等待设备重枚举完成,最后进入while(1)循环语句,执行任务调度。这里不具体说了参考源程序,框架的源文件和头文件如下所示。

|

EZUSB.LIB |

EZUSB库文件 |

|

EZUSB.h |

EZUSB头文件 |

|

fx2regs.h |

FX2寄存器头文件 |

|

fx2.h |

预定义,宏及函数声明 |

|

fw.c |

固件框架源文件 |

|

dscr.a51 |

USB描述符列表,用户可修改 |

|

USBJmpTb.OBJ |

中断跳转函数目标文件 |

|

syncdly.h |

同步延时,定义了程序短延时函数SYNCDELAY |

|

intrins.h |

C51一些数据类型及函数定义 |

|

intr.c |

外部中断处理文件 |

|

app_xxx.c |

用户钩子函数文件,可修改,用户代码 |

除此以外,我们需要了解的函数包括:

•void TD_Init():此函数在USB启动后只调用一次。此函数主要添加USB数据传输的初始化代码,也就是传输之前要配置的。通过68013内部寄存器,配置好时钟、FIFO、中断等。

•void TD_Poll():用户调度程序,USB在空闲时反复执行该函数,通常将反复执行的代码放着里面。

•void ISR_EXTR0(void) interrupt 0:外部中断处理函数,当外部中断产生时,程序跳转至此,执行该中断子程序。

■void TD_Init(void)

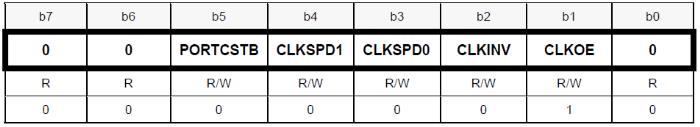

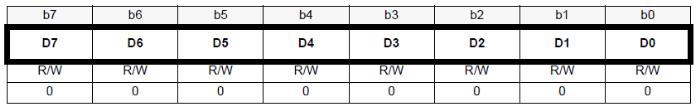

1、设置CPU即68013时钟为24MHZ。设置时钟寄存器CPUCS=0x0a;其中CPUCS寄 存器如下所示:

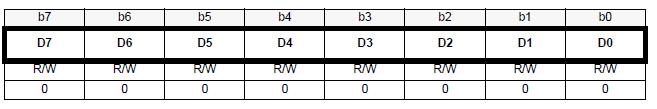

CPUCS

•PORTCSTB --- 1表示读写端口C时产生RD#和WR#信号,0不产生读写信号,默认 为0。

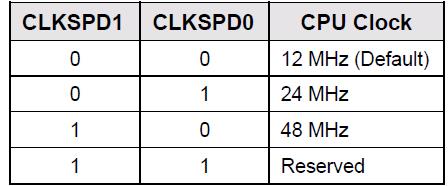

•CLKSPD1,CLKSPD0 --- CPU时钟设置。如下表所示:

在CC1601采集卡版本中,可以通过此寄存器修改给cmos提供的时钟,12M、24M、48M。

注意:时钟设置太高,可能导致cmos输出不正常。降低时钟可以降低帧率,会增加稳定性。

•CLKINV --- 时钟状态反转

•CLKOE --- 时钟使能

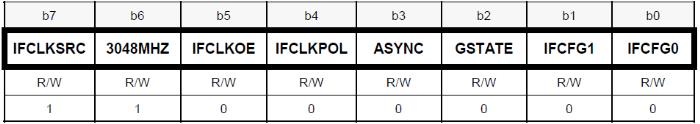

2、接口配置寄存器IFCONFIG

设置IFCONFIG=0x03; //选择为外部时钟,同步SlaveFIFO模式,输入//IFCLK(5-48MHZ)(0000_0011)

IFCONFIG

•IFCLKSRC --- 0外部时钟源,1内部时钟源。

•3048MHZ --- 0 IFCLK时钟为30M,1 IFCLK时钟为48M。

•IFCLKOE --- IFCLK时钟输出使能,0关闭,1打开。

•IFCLKOL ---IFCLK信号反正,0不反转,1反转

•ASYNC --- GPIF同步或异步操作,0同步,1异步

•GSTATE---GPIF状态输出使能,0关闭,1使能,引脚PE0 PE1 PE2和GPIF状态GSTATE0,GSTATE1,GSTATE2。

•IFCFG0,IFCFG1 --- 模式设置,决定了端口引脚功能。

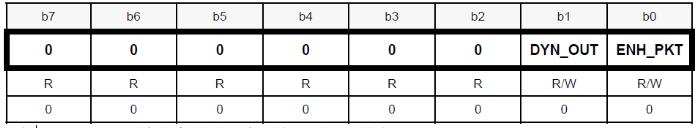

3、REVCTL芯片版本控制寄存器

设置REVCTL=0x03;

REVCTL

该寄存器在SLAVE FIFOS编程中用到,建议设置b1b0=11。

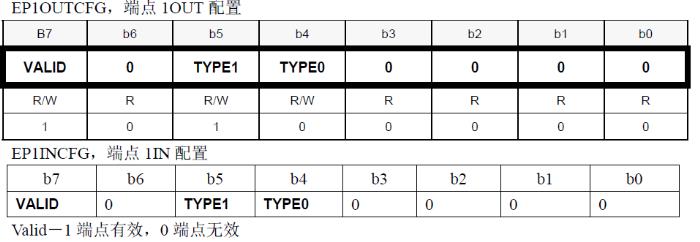

4、端点1IN和1OUT配置寄存器

由驱动设计可知,只用到了FIFO 2。因此这两个寄存器直接采用默认值即可,只作简单介绍。

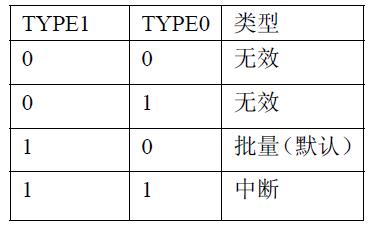

TYPE1,TYPE0 --- 端点类型见下表。

5、端点2、4、6、8配置寄存器

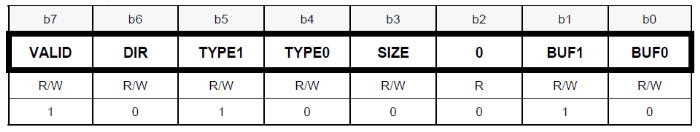

由于只用到了端点2,因此设置EP2CFG=0xE0;对于EP2CFG寄存器如下所示。

•VALID --- 0端点无效,1端点有效。

•DIR --- 端点方向,0=OUT方向,1=IN方向,默认端点2,4位IN,端点6,8为OUT。

•TYPE1,TYPE0 --- 端点类型,如下表所示。

•SIZE --- 缓冲区大小(仅端口2和端点6),0=512字节,1=1024字节

•BUF1,BUF0 --- 端点缓冲区个数(仅端口2和端点6)。

将其设置为端点2有效,IN方向,批量传输方式,传输字节为512B,四缓冲方式。

而将EP4CFG、EP6CFG、EP8CFG均设置为无效。

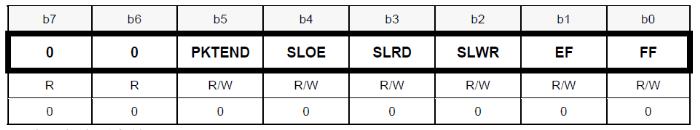

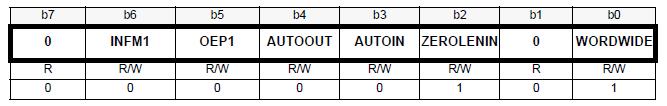

6、Slave FIFO端点2/4/6/8 FIFO配置

设置EP2FIFOCFG=0x08;表示FIFO 8位输入模式。

•INFM1 --- 1表示IN端点满减1。

•OEP1 --- 1表示OUT端点空加1。

•AUTOOUT --- 1表示数据自动提交OUT端点FIFO,0表示手动。

•AUTOIN --- 1表示IN端点FIFO数据自动呈交SIE,0表示手动。

•ZEROLENIN --- 1表示使能零长度IN端点数据包,0表示非使能。

•WORDWIED --- 数据宽度,0表示8bit,1表示16bit。

对于其他FIFO,由于没用到,直接配置成0x00。

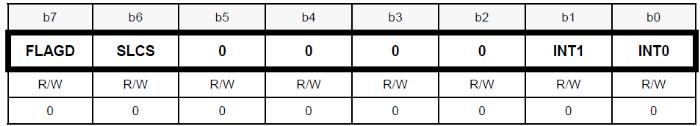

7、设置SLWR为高电平有效,其他为低电平有效。通过PORTACFG和FIFOPINPOLAR 寄存器来设置。

PORTACFG

PORTACFG |=0x40表示SLCS设置为复用引脚功能,且低电平有效。

FIFOPINPOLAR

0 表示低电平有效

1表示高电平有效

这里FIFOPINPOLAR = 0x07将SLWR设置为高电平有效,其余的设置为低电平 有效。

8、端点2 AUTOIN数据长度设置

设置EP2AUTOINLENH = 0x02;//包长度高字节,自动传送包大小为512B。

EP2AUTOINLENL=0x00;

9、AUTOPTRSETUP |= 0x01;//使能自动指针特征,可以很方便在两个内存间传输数 据。

10、SLAVE FIFOs FLAGx配置寄存器

PINFLAGSAB = 0x00;

SYNCDELAY;

PINFLAGSCD = 0x00;

SYNCDELAY;

硬件驱动中都没用到该部分,忽略不计。

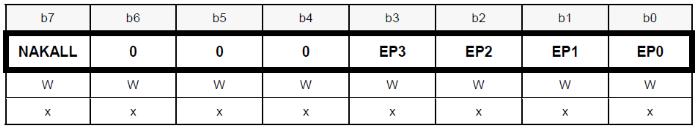

11、复位FIFO寄存器

FIFORESET

NAKALL --- 0表示关闭NAK功能,1表示用NAK响应主控器请求。在复位端点 时,为了保证复位正常,防止主控器请求的干扰,先写入0x80,复位完成后,再 写入0x00,以此响应请求。如下所示:

FIFORESET = 0x80;// activate NAK-ALL to avoid race conditions

FIFORESET = 0x02;// reset, FIFO 2

FIFORESET = 0x04;// reset, FIFO 4

FIFORESET = 0x06;// reset, FIFO 6

FIFORESET = 0x08;// reset, FIFO 8

FIFORESET = 0x00;// deactivate NAK-AL

12、配置68013内核引脚

如原理图所示,USB_PA0作为中断源,输入至USB68013,设置USB_PA0引脚为 输入引脚。而USB_PD5作为USB_Trigger,输出至FPGA,可认为是68013给予 FPGA的反馈信号。因此,设置USB_PD5为输出引脚。

•程序中设置PD5为输出引脚,且初始化PD5为0。

OED |= (1<<5);//PD5 0:Input; 1:output

//OED = 0x20;

PD5 = 0;

OED端口D输出使能寄存器

•程序中设置PA0为中断触发源。

OEA端口A输出使能寄存器

设置PA0为输入引脚,即默认D0=0;并将PA0设置为外部中断INT0#。

OEA &= ~(1<<0); //PA0-INT0 0:Input

//OEA=0x00;

PORTACFG |= (1<<0); //Configure PA0 as INT0#

//PORTACFG = 0x01;

13、特殊功能寄存器TCON

通过特殊功能TCON来设定INT0#的中断类型。当IT0=1时,采用上升沿触发中 断,当IT0=0时,采用低电平触发中断。设置IE=1允许中断,IE=0禁止中断。

IT0 = 1; //When ITx = 1, posedge edge Sample; When ITx = 0, low-level //Sample.

IE |= (1<<0);//Enable INT0

■ISR_EXTR0(void) interrupt 0

CB的中断处理,可一言以蔽之:抽帧。由于PC机自身的局限性,为了降低PC的带宽,对获取的640*480像素大小的图像进行抽帧处理。USB68013只接收部分图像,来有效降低PC的带宽。其过程如下所示:

•PA0作为中断源,采取上升沿触发中断,连接至CMOS_VSYNC,即摄像头场信号。当 场信号出现上升沿时标志着一帧图像的结束和下一帧的开始。

•frame_interval_en做为抽帧的使能信号,初始值为1。每次进入中断,帧计数器自动加1,通过判断帧计数器来实现抽帧处理。

•PD5信号是USB连接至FPGA的信号,由assign USB_WR = i2c_config_done & cmos_href & USB_Trigger;可以得知,PD5=1时,USB允许数据写入。

•当frame_cnt%2==0时,以15FPS写入FIFO;

•当满足条件frame_cnt%2==0时,PD5=1,允许写入FIFO,不满足时,PD5=0,禁止 写入FIFO。

•在每次禁止写入FIFO时,复位FIFO 2。以使FIFO 2数据为空,这样就不存在FIFO 满状态。以此来防止因FIFO满状态而引起的数据丢失。

void ISR_EXTR0(void) interrupt 0 //using 0

{

if(frame_interval_en == 1)

{

frame_cnt++;

if((frame_cnt%2)==0) //5:6FPS; 4:7.5FPS; 3:10FPS; 2:15FPS; 1:30FPS;

{

PD5 = 1; //Enable image input

}

else

{

PD5 = 0; //Disable image input

//Reset FIFO of EDP2

SYNCDELAY;

FIFORESET = 0x80;// activate NAK-ALL to avoid race conditions

SYNCDELAY;

FIFORESET = 0x02;// reset, FIFO 2

SYNCDELAY;

FIFORESET = 0x00;// deactivate NAK-AL

SYNCDELAY;

}

}

else

{

PD5 = 1; //Enable image input continue , and no frame interval

}

}

以上是关于usb2.0高速视频采集之68013A寄存器配置说明的主要内容,如果未能解决你的问题,请参考以下文章