MSR和MRS指令操作CPSR寄存器

Posted NQian

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了MSR和MRS指令操作CPSR寄存器相关的知识,希望对你有一定的参考价值。

1.MSR和MRS指令介绍

MRS 指令: 对状态寄存器CPSR和SPSR进行读操作。通过读CPSR可以获得当前处理器的工作状态。读SPSR寄存器可以获得进入异常前的处理器状态(因为只有异常模式下有SPSR寄存器)。

MSR指令: 对状态寄存器CPSR和SPSR进行写操作。与MRS配合使用,可以实现对CPSR或SPSR寄存器的读-修改-写操作,可以切换处理器模式、或者允许/禁止IRQ/FIQ中断等。

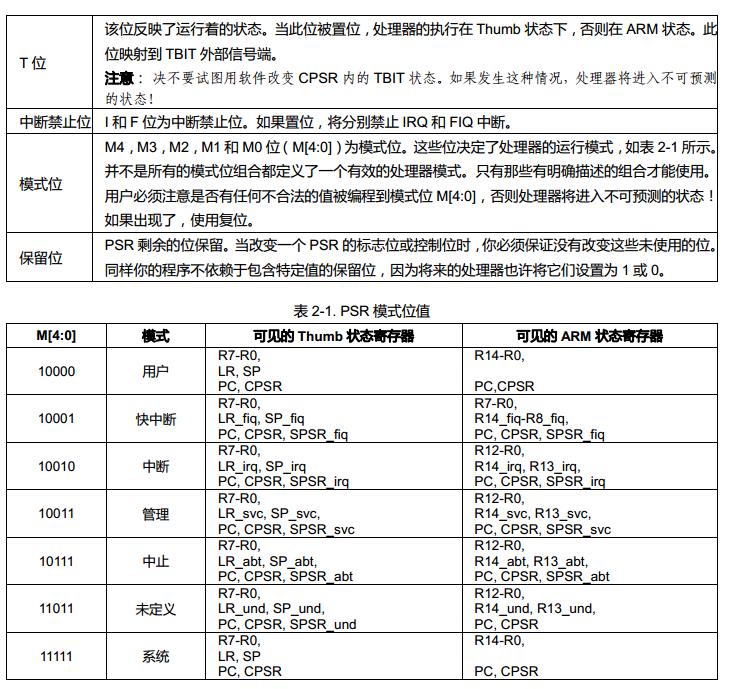

2.CPSR 程序状态寄存器(current program status register)

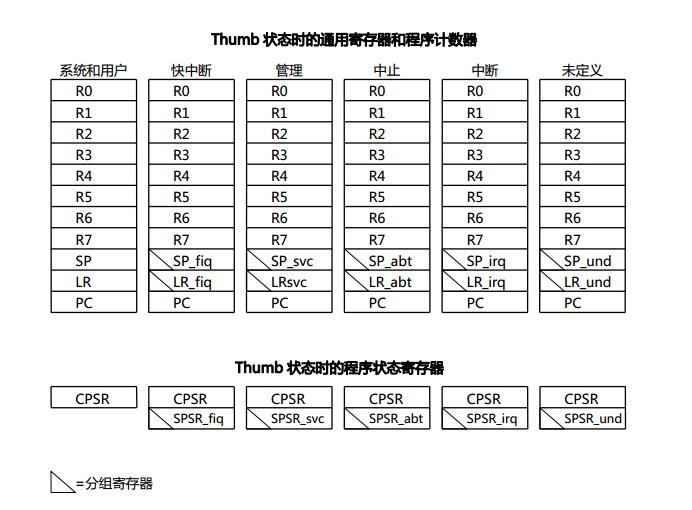

如图所示,ARM每种工作模式除R0~R15共16个寄存器外,还有第17个寄存器CPSR,叫做 当前程序状态寄存器

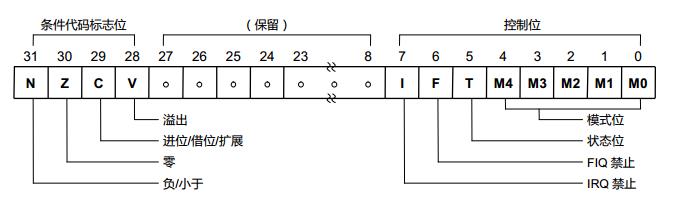

CPSR寄存器格式:

在CPSR寄存器中主要用到了控制位,每个标志位如下图所示:

3.使用MSR指令写入数据

例:

msr cpsr_c, #0xd2 @0xd2=1100 0010//禁止中断使能,进入中断模式 msr cpsr_c, #0x53 @0x53=0101 0011//开IRQ中断,禁止FIQ中断,进入ARM状态,设为管理(svc32)模式

其中cpsr_c是因为CPSR有4个8位区域:

- C 控制域屏蔽字节([7:0])

- X 扩展域屏蔽字节([15:8])

- S 状态域屏蔽字节([23:16])

- F 标志域屏蔽字节([31:24])

所以cpsr_c表示的是CPSR控制位、

4.使用MRS和MSR来设置2440位管理模式,实例:

mrs r0,cpsr //读状态寄存器cpsr的数据到r0中 bic r0,r0,#0x1f //对r0低5位进行清0,清除模式位 orr r0,r0,#0xd3 //低8位或(110 10011), 设为管理(svc32)模式,禁止IRQ和FIQ中断 msr cpsr,r0 //写入状态寄存器cpsr,更新。

5.SPSR程序保存状态寄存器(saved program status register)

SPSR用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。在异常中断退出时,可以用SPSR来恢复CPSR。

(注意:用户user模式和系统system模式不是异常中断模式,所以他没有SPSR。当用户在用户模式或系统模式访问SPSR,将产生不可预知的后果。)

在异常模式返回时,如果指令带有S后缀(除了比较指令以外),同时又以PC为目标寄存器进行操作,则操作的同时从SPSR恢复CPSR。以下都是可以恢复CPSR寄存器

例如:

movs pc, #0xff // cpsr = spsr; pc = 0xff adds pc, r1, #0xffffff00 //cpsr = spsr; pc = r1 + 0xffffff00 ands pc, r1, r2 //cpsr = spsr; pc = r1 & r2; ldmia sp!, { r0-r12,pc }^ //中断返回, ^表示将spsr的值复制到cpsr

以上是关于MSR和MRS指令操作CPSR寄存器的主要内容,如果未能解决你的问题,请参考以下文章