ddr3调试经验分享——KC705_MIG时钟清单

Posted 清霜一梦

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ddr3调试经验分享——KC705_MIG时钟清单相关的知识,希望对你有一定的参考价值。

最近阿威也在玩MIG ,然后对我问了一大堆问题,主要针对MIG的时钟。后来发现自己理解得还是不够。这么一讨论更加清晰了,做个笔记吧。

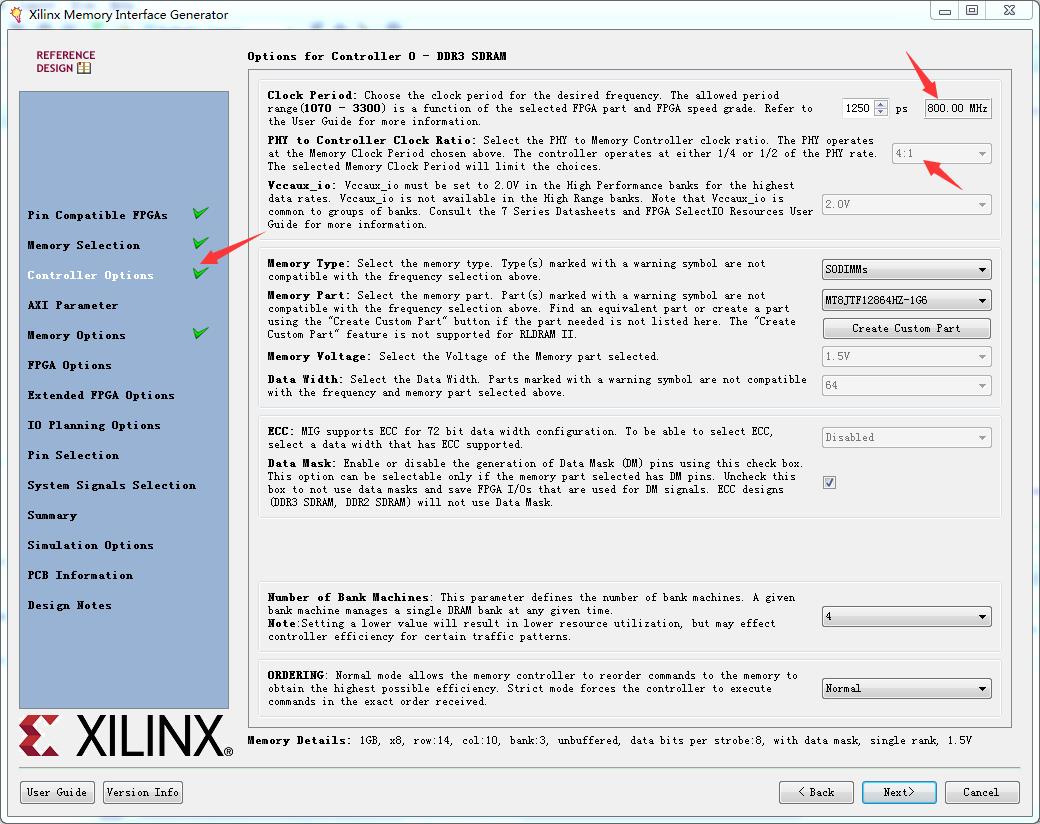

第一个时钟,也就是MIG 对DDR接口的时钟。因为我用的是ddr3,K7的器件。所以选择了800M,那么也就是说我请求的MIG对ddr接口的速率是800M *2=1600M (双沿,所以乘2)

下面有一个4:1, 证明MIG 输出到app接口上的时钟ui_clk 是 800M/4=200M 。这里为啥是灰色呢,估计应该是到了app接口上限:200M的运行速率,data位宽512bit。具体哪一个是上限

没有去尝试。(应该是200M吧,因为我还没有告诉MIG 我的ddr数据位宽是16bit还是64bit)

这里如果选择了clock period 是400M ,那么下面的4:1可选为4:1—— app接口时钟100M ,或者选择2:1—— app接口时钟200M

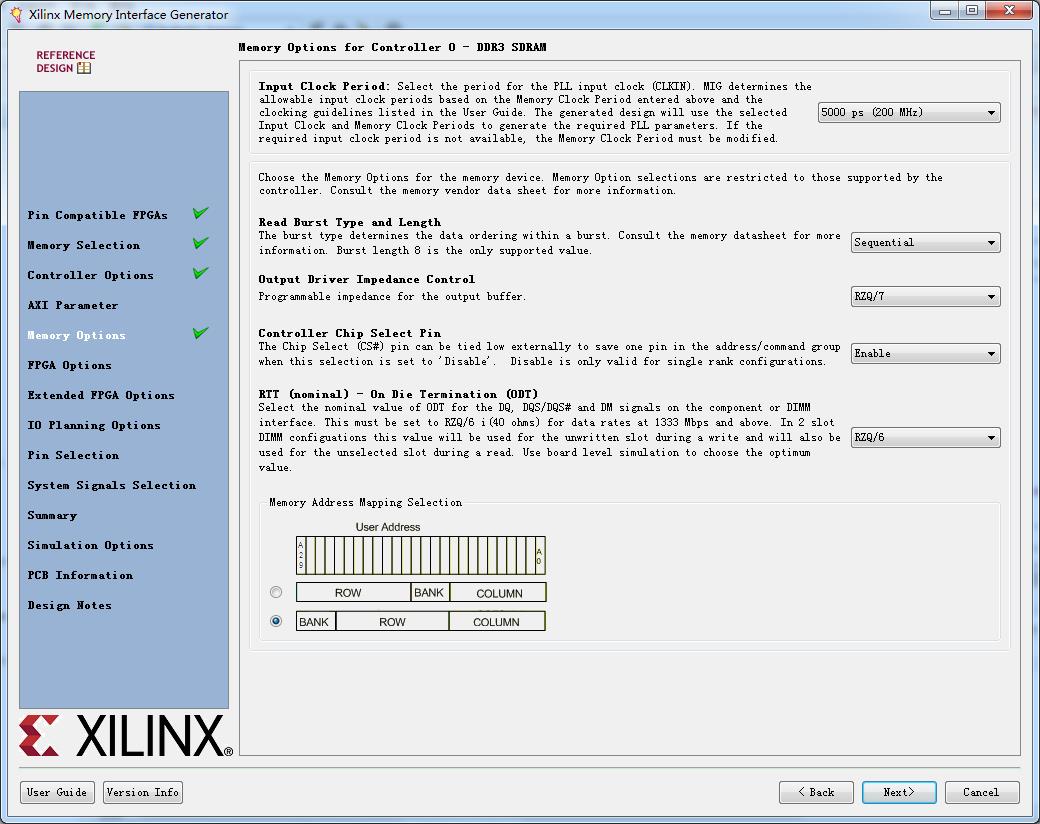

第二个时钟

这里是输入给MIG 的时钟,kc705上晶振是差分200M ,所以这个就选择200M 。但是不要勉强,什么意思呢,就是这个时钟是你的top 层input clock 。不要在中间接东西。因为我是差分信号的clock,

总想自己分一个出来用,结果怎么弄都是报错,不管接gds,bufg,还是pll都不行。所以你的晶振是多少就选择多少。这里的200M 对于后面有好处。

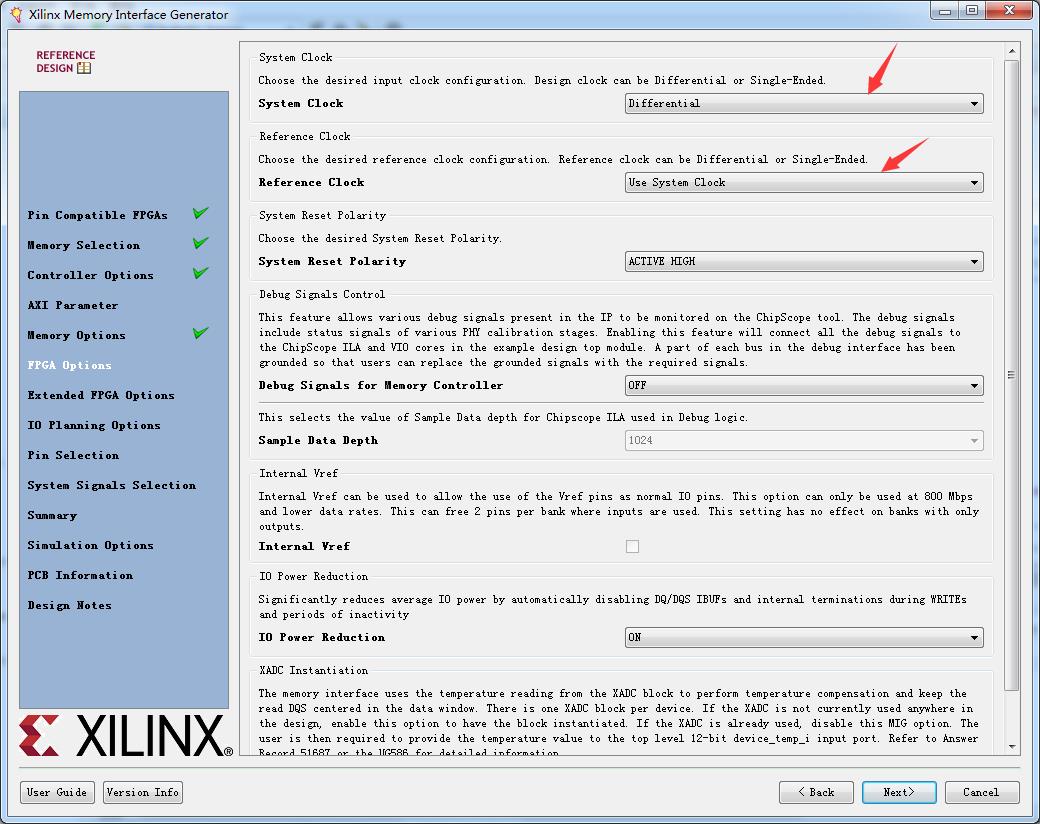

第三个时钟:

不明白为啥这个MIG 不能一次把话讲完,第二张图中已经设定了输入是200M 的时钟,这里的system clock还是设定输入时钟是差分还是单端的,因为我的晶振是差分200M

所以设定为差分。下面的这个reference clock就是MIG 需要一个200M 的时钟作为参考 —— 硬性需求啊。又因为我的第二张图中告诉了MIG ,我给他的clock就已经是200M 了,

所以这个地方就多了一个选项卡 use system clock —— 这个system clock 和第二张图中的input clock 是同一个东西。

如果你的第二张图中input clock不是200M,这里就没有这个use system clock的选项卡,那么你就需要选择其他的选项。最后MIG最后生成的.v 就多了一个ref_clk的接口问你要200M时钟。

最后感谢一下阿威,精明的娃忽悠不住!!! 非得解释清楚。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

以上是关于ddr3调试经验分享——KC705_MIG时钟清单的主要内容,如果未能解决你的问题,请参考以下文章