FPGA学习之数码管(封装)显示时间

Posted 古月照今尘

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA学习之数码管(封装)显示时间相关的知识,希望对你有一定的参考价值。

一、实验目的:学习数码管封装以及显示时间。

二、实验环境:FPGA开发板AX301,Quartus ii

三、实验介绍:将数码管显示模块封装起来,同时通过不断读取RTC时钟的时分秒值,将之显示在数码管。实验时,将实时时间的时分秒写入程序,运行程序后可以看到数码管显示的时间会不断的刷新。

四、源码

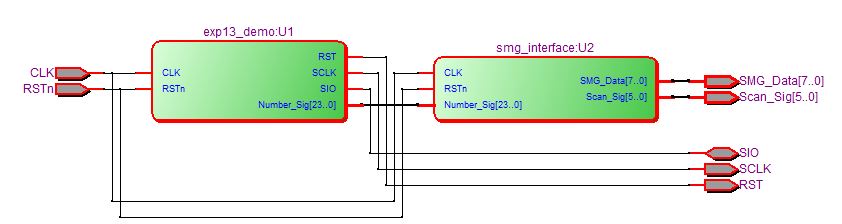

module smg_interface_demo ( input CLK, input RSTn, output RST, output SCLK, inout SIO, output [7:0]SMG_Data, output [5:0]Scan_Sig ); /******************************/ wire [23:0]Number_Sig; exp13_demo U1 ( .CLK( CLK ), .RSTn( RSTn ), .Number_Sig(Number_Sig), .RST( RST ), .SCLK( SCLK ), .SIO( SIO ) ); /******************************/ smg_interface U2 ( .CLK( CLK ), .RSTn( RSTn ), .Number_Sig( Number_Sig), // .Number_Sig( Number_Sig ), // input - from U1 .SMG_Data( SMG_Data ), // output - to top .Scan_Sig( Scan_Sig ) // output - to top ); /******************************/ endmodule

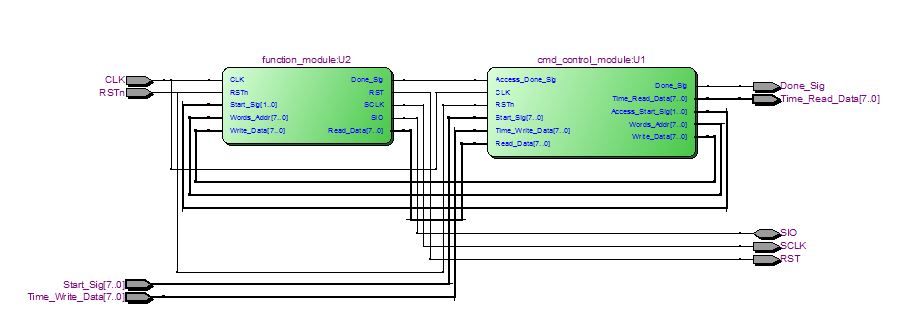

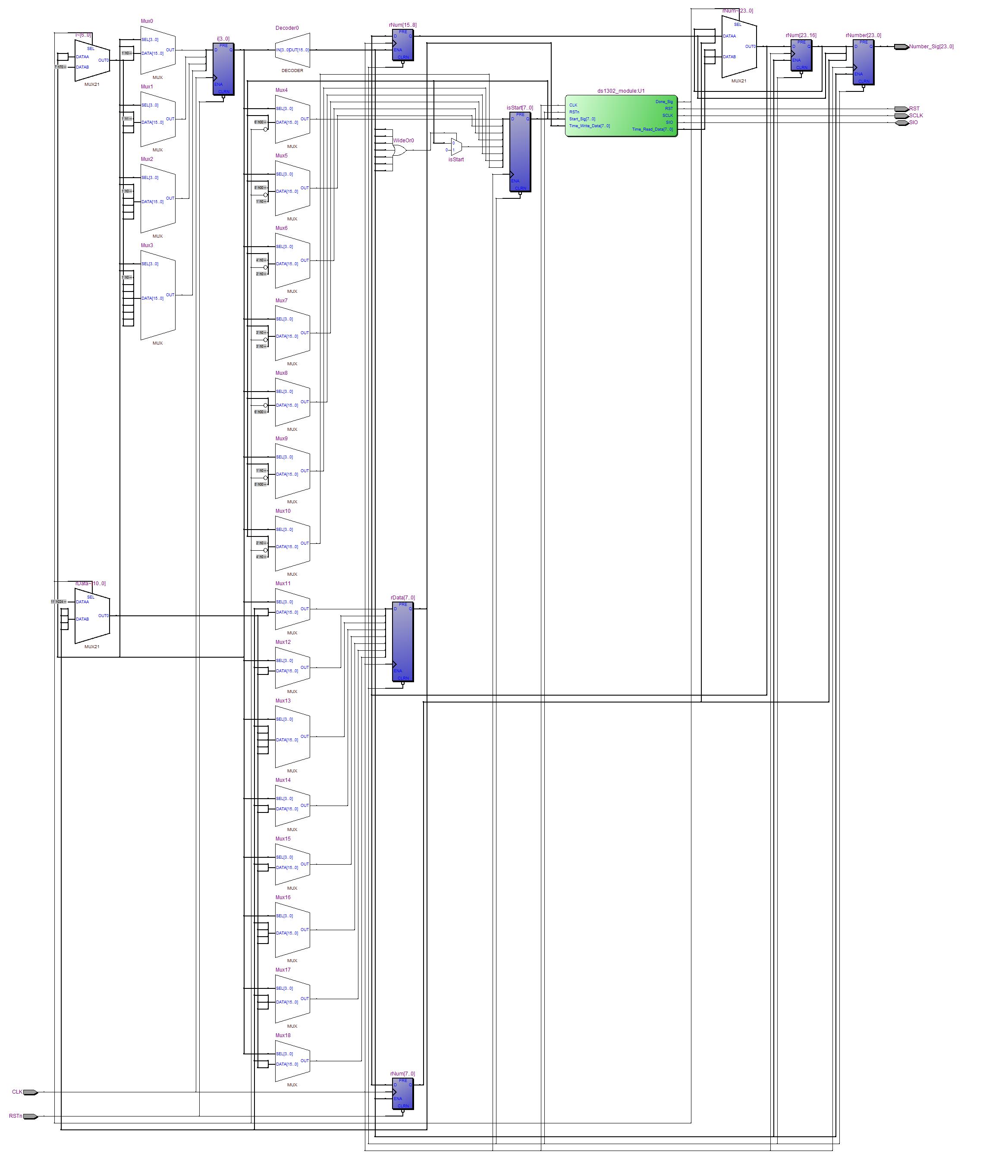

module exp13_demo //将DS1302的时分秒显示在六位数码管上 ( CLK, RSTn, Number_Sig, //Second_data0, Second_data1, Mini_data0,Mini_data1,Hour_data0,Hour_data1, // LED, RST, SCLK, SIO ); input CLK; input RSTn; output RST; output SCLK; inout SIO; // output [3:0]LED; // output [19:0]showdata; output [23:0] Number_Sig; // output [7:0]Row_Scan_Sig; // output [5:0]Column_Scan_Sig; // output [3:0]Second_data0; // output [3:0]Second_data1; // output [3:0]Mini_data0; // output [3:0]Mini_data1; // output [3:0]Hour_data0; // output [3:0]Hour_data1; /*******************************/ /******************************/ parameter T100MS = 23\'d4_999_999; /******************************/ reg [22:0]C1; always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) C1 <= 23\'d0; else if( C1 == T100MS ) C1 <= 23\'d0; else C1 <= C1 + 1\'b1; /*******************************************************/ reg [3:0]i; reg [7:0]isStart; reg [7:0]rData; //reg [3:0]rLED; reg [3:0]rSecond_data0; reg [3:0]rSecond_data1; reg [3:0]rMini_data0; reg [3:0]rMini_data1; reg [3:0]rHour_data0; reg [3:0]rHour_data1; reg [23:0]rNum; reg [23:0]rNumber; // always @ ( posedge CLK or negedge RSTn ) // if( !RSTn ) // begin // i <= 4\'d0; // rNum <= 24\'d0; // rNumber <= 24\'d0; // end // else // case( i ) // // 0: // if( C1 == T100MS ) begin rNum[3:0] <= rNum[3:0] + 1\'b1; i <= i + 1\'b1; end // // 1: // if( rNum[3:0] > 4\'d9 ) begin rNum[7:4] <= rNum[7:4] + 1\'b1; rNum[3:0] <= 4\'d0; i <= i + 1\'b1; end // else i <= i + 1\'b1; // // 2: // if( rNum[7:4] > 4\'d9 ) begin rNum[11:8] <= rNum[11:8] + 1\'b1; rNum[7:4] <= 4\'d0; i <= i + 1\'b1; end // else i <= i + 1\'b1; // // 3: // if( rNum[11:8] > 4\'d9 ) begin rNum[15:12] <= rNum[15:12] + 1\'b1; rNum[11:8] <= 4\'d0; i <= i + 1\'b1; end // else i <= i + 1\'b1; // // 4: // if( rNum[15:12] > 4\'d9 ) begin rNum[19:16] <= rNum[19:16] + 1\'b1; rNum[15:12] <= 4\'d0; i <= i + 1\'b1; end // else i <= i + 1\'b1; // // 5: // if( rNum[15:12] > 4\'d9 ) begin rNum[19:16] <= rNum[19:16] + 1\'b1; rNum[15:12] <= 4\'d0; i <= i + 1\'b1; end // else i <= i + 1\'b1; // // 6: // if( rNum[19:16] > 4\'d9 ) begin rNum[23:20] <= rNum[23:20] + 1\'b1; rNum[19:16] <= 4\'d0; end // else i <= i + 1\'b1; // // 7: // if( rNum[23:20] > 4\'d9 ) begin rNum <= 24\'d0; i <= i + 1\'b1; end // else i <= i + 1\'b1; // // 8: // begin rNumber <= rNum; i <= 4\'d0; end // // endcase /*******************************************************/ always @ ( posedge CLK or negedge RSTn ) if( !RSTn ) begin i <= 4\'d0; isStart <= 8\'d0; rData <= 8\'d0; rNum <= 24\'d0; rNumber <= 24\'d0; //rLED <= 4\'d0; end else case( i ) 0: if( Done_Sig ) begin isStart <= 8\'d0; i <= i + 1\'b1; end else begin isStart <= 8\'b1000_0000; rData <= 8\'h00; end 1: if( Done_Sig ) begin isStart <= 8\'d0; i <= i + 1\'b1; end else begin isStart <= 8\'b0100_0000; rData <= { 4\'d2, 4\'d0 }; end //HOUR 2: if( Done_Sig ) begin isStart <= 8\'d0; i <= i + 1\'b1; end else begin isStart <= 8\'b0010_0000; rData <= { 4\'d0, 4\'d6 }; end//MINITU 3: if( Done_Sig ) begin isStart <= 8\'d0; i <= i + 1\'b1; end//SECOND else begin isStart <= 8\'b0001_0000; rData <= { 4\'d2, 4\'d2 }; end 4: //if( Done_Sig ) begin rLED <= Time_Read_Data[3:0];rSecond_data0<= Time_Read_Data[3:0];rSecond_data1<= Time_Read_Data[7:4]; isStart <= 8\'d0; i <= 4\'d4; end if( Done_Sig ) begin rNum[7:4]<=Time_Read_Data[7:4];rNum[3:0]<=Time_Read_Data[3:0];rSecond_data0<= Time_Read_Data[3:0];rSecond_data1<= Time_Read_Data[7:4]; isStart <= 8\'d0; i <= i + 1\'b1; end else begin isStart <= 8\'b0000_0001; end 5: if( Done_Sig ) begin rNum[15:12]<=Time_Read_Data[7:4];rNum[11:8]<=Time_Read_Data[3:0];rMini_data0<= Time_Read_Data[3:0];rMini_data1<= Time_Read_Data[7:4]; isStart <= 8\'d0; i <= i + 1\'b1; end else begin isStart <= 8\'b0000_0010; end 6: if( Done_Sig ) begin rNum[23:20]<=Time_Read_Data[7:4];rNum[19:16]<=Time_Read_Data[3:0];rHour_data0<= Time_Read_Data[3:0];rHour_data1<= Time_Read_Data[7:4]; isStart <= 8\'d0; i <= i + 1\'b1; end else begin isStart <= 8\'b0000_0100; end 7: if(i==7) begin rNumber <= rNum;i<= 4\'d4;end endcase /********************************************/ wire Done_Sig; wire [7:0]Time_Read_Data; ds1302_module U1 ( .CLK( CLK ), .RSTn( RSTn ), .Start_Sig( isStart ), .Done_Sig( Done_Sig ), .Time_Write_Data( rData ), .Time_Read_Data( Time_Read_Data ), .RST( RST ), .SCLK( SCLK ), .SIO( SIO ) ); /********************************************/ // assign LED = rLED; // assign Second_data0 = rSecond_data0; // assign Second_data1 = rSecond_data1; // assign Mini_data0 = rMini_data0; // assign Mini_data1 = rMini_data1; // assign Hour_data0 = rHour_data0; // assign Hour_data1 = rHour_data0; //assign Number_Sig = rSecond_data0+rSecond_data1*10+rMini_data0*100+rMini_data1*1000+rHour_data0*10000+rHour_data1*100000; // assign //assign Number_Sig[23:20] = rHour_data1; // assign Number_Sig[19:16] = rHour_data0; // assign Number_Sig[15:12] = rMini_data1; // assign Number_Sig[11:8] = rMini_data0; // assign Number_Sig[7:4] = rSecond_data1; // assign Number_Sig[3:0] = rSecond_data0; //assign Number_Sig={rHour_data1,rHour_data0,rMini_data1,rMini_data0,rSecond_data1,rSecond_data0}; //assign Number_Sig = 24\'d123456; assign Number_Sig = rNumber; /*********************************************/ endmodule

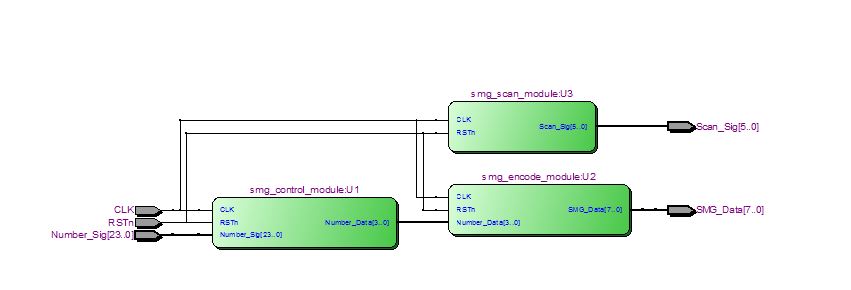

module smg_interface ( input CLK, input RSTn, input [23:0]Number_Sig, output [7:0]SMG_Data, output [5:0]Scan_Sig ); /******************************************/ wire [3:0]Number_Data; smg_control_module U1 ( .CLK( CLK ), .RSTn( RSTn ), .Number_Sig( Number_Sig ), // input - from top .Number_Data( Number_Data ) // output - to U2 ); /******************************************/ smg_encode_module U2 ( .CLK( CLK ), .RSTn( RSTn ), .Number_Data( Number_Data ), // input - from U2 .SMG_Data( SMG_Data ) // output - to top ); /*******************************************/ smg_scan_module U3 ( .CLK( CLK ), .RSTn( RSTn ), .Scan_Sig( Scan_Sig ) // output - to top ); /*******************************************/ endmodule

五、RTL图

六、总结

前几次编译下载程序总是显示异常,最后发现是PIN管脚问题,以后需要注意检查硬件配置是否正确。

以上是关于FPGA学习之数码管(封装)显示时间的主要内容,如果未能解决你的问题,请参考以下文章