小梅哥SOPC学习笔记SOPC开发常见问题及解决办法集锦

Posted 小梅哥

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了小梅哥SOPC学习笔记SOPC开发常见问题及解决办法集锦相关的知识,希望对你有一定的参考价值。

SOPC开发常见问题及解决办法集锦

一、Symbol \'NULL\' could not be resolved

近期在评估使用Nios II处理器进行项目的开发,我使用的软件是Quartus II 13.0的版本,一路下来,在Qsys系统中搭建NIOS II片上系统,在Quartus II中建立工程文件等等过程,没有太多的问题,这里暂且不表。只是在NIOS II Software build tools for Eclipse中进行软件开发时,一个非常让人不解的问题就是:我在工程向导中创建一个Hello World的模版工程,然后编译下载运行都没问题。然后关闭NIOS II Software build tools for Eclipse软件,再次打开时,结果就冒出一大堆错误,错误描述如下:

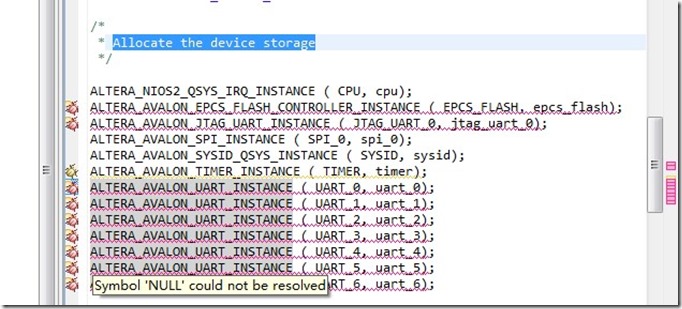

在alt_sys_init.c这个文件中,报错“Symbol \'NULL\' could not be resolved”,此报错主要集中在分配设备存储(Allocate the device storage)这一部分,例如,我的系统中报错如下所示:

提示我NULL未定义。可是NULL明明是在stddef.h这样一个标准头文件中明确定义了的,怎么还会发生这种情况呢?

另外,由于本系统中使用到了UART IP,所以系统在自动生成时也提供了对应的驱动,打开一个驱动程序“altera_avalon_uart_write.c”,发现同样有报错的地方,这里主要提示:“Symbol \'O_NONBLOCK\' could not be resolved”,其它文件中也有类似的提示,这就让人很是纳闷了。O_NONBLOCK这个宏定义明明是在” sys/_default_fcntl.h”这个文件中定义了的,为什么总是说找不到呢?

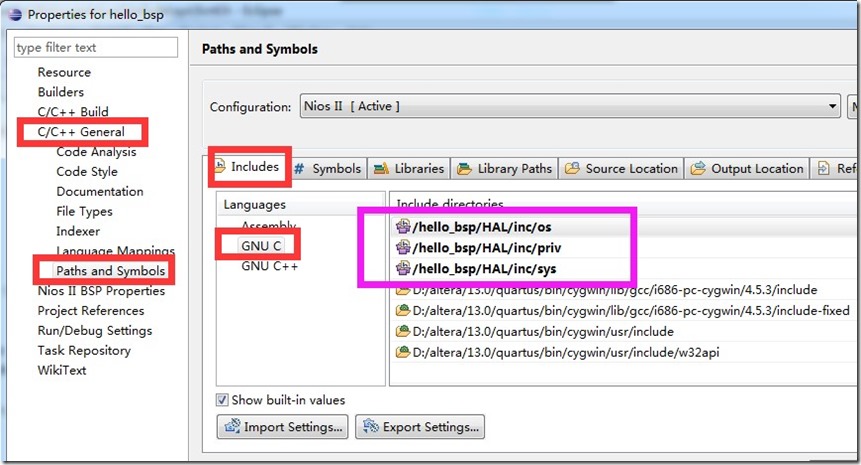

参考网上的方法,说是需要手动添加包头文件包含路径,怀着试一试的心态,我打开了bsp工程的选项对话框(选中XXX_bsp工程,单击右键,选中properties),在打开的对话框中,切换到C/C++ general选项下的paths and Symbols选项栏,选择GUN C,在里面添加了三个路径

/hello_bsp/HAL/inc/os

/hello_bsp/HAL/inc/priv

/hello_bsp/HAL/inc/sys

如下图所示:

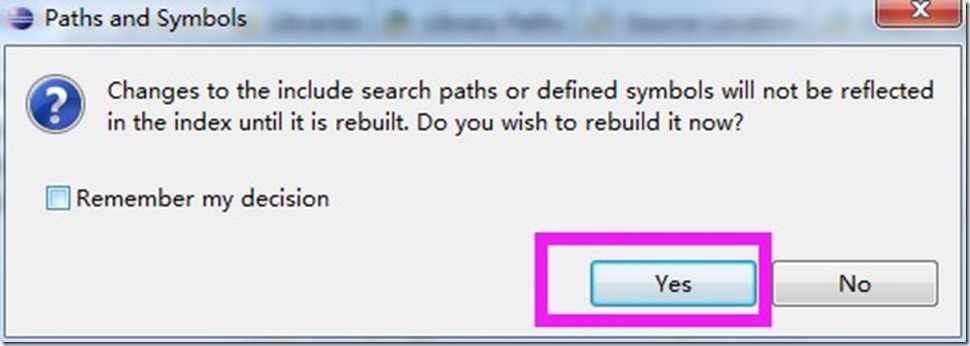

添加完成之后点击Apply,此时会弹出如下对话框:

点击YES即可,然后点击OK关闭设置窗口。

此时对XXX_bsp工程执行Clean操作,然后build。待build完成之后,再次打开前面提到的报错的若干文件,发现没有了报错信息,关闭NIOS II Software build tools for Eclipse软件,然后再打开,都没有再出现这种报错信息,因此问题成功解决。

二、NIOS II CPU复位异常

近期在用nios ii做项目时,发现一个奇怪的现象,在NIOS II EDS软件中编写好的代码,烧写到芯片中,第一次能够正常运行,但是当我按下板卡上的复位键之后,系统却卡死了,再也运行不起来,除非重新下载程序。经过分析系统可知,系统的硬件设计和Qsys系统中NIOS II CPU系统的搭建都是没有任何问题的。那么为什么会存在这样的问题呢,这里我先简单介绍下我的系统:

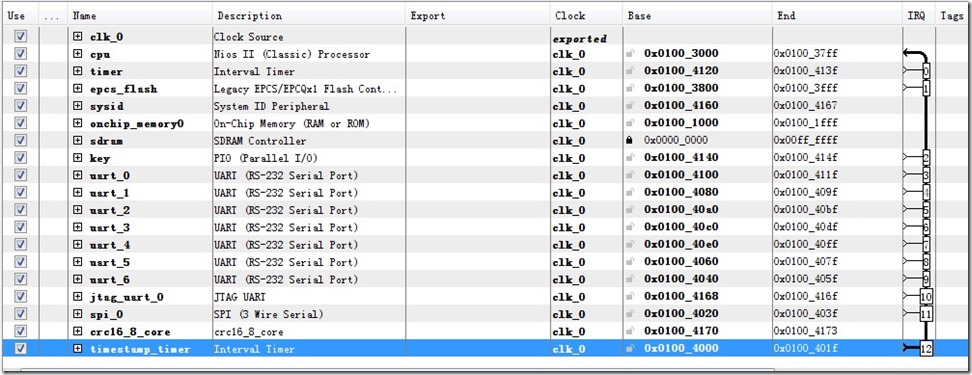

我的系统主要由NIOS II最强板CPU,SDRAM、预留系统定时器、预留时间戳定时器、system ID、EPCS控制器以及JTAG_UART组成。具体如下图所示:

在Qsys环境中,我一开始将CPU的复位向量(Reset Vector)设定在了EPCS上,然后在NIOS II EDS中建立了软件工程,编译,下载运行都没有问题,但是并没有将fpga配置文件和代码固化到EPCS中去,因此复位时存在问题是肯定的。后来为了调试方便,在Qsys系统中将CPU的复位向量也修改指向了SDRAM,然后在NIOS II EDS软件中,重新生成了BSP之后,软件的编译,下载运行都没有问题,只是每当我按下板卡上的复位键之后,系统却卡死了,再也运行不起来。

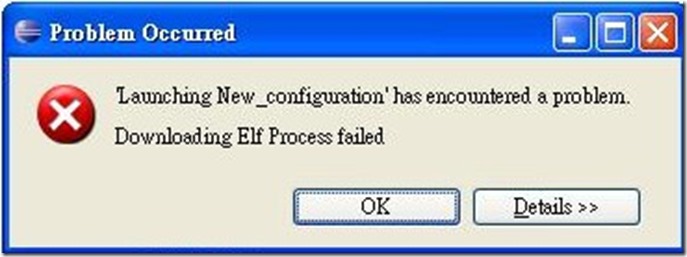

记起去年做毕业设计时,曾经为在含有EPCS的系统中无法下载程序的问题苦恼过,当时下载程序时,每次都在进度为64%时报如下的错误,“Nios II ‘Launching New_configuration’ has ecountered a problem.Dowenloading Elf Process failed.”相信这个报错也是大家最深恶痛绝的(注,此图是我从网上下载的,自己做系统已经很久不出这个问题了,想弄张这样的图片只能百度了):

在网上找了一大堆问题,有说是SDRAM相位不对的,这个我以前也确实遇见过,不过自从我将SDRAM的时钟相移设定为-90度后,就基本没遇到过这个问题了。还有说是硬件本身有问题的,这里不排除此种情况,但是我的系统中却并非如此。最终是在新浪博客还是百度空间中的某位前辈的文章中找到的答案我忘记了。当时忘了记下博客地址了,只是将内容复制出来,存了一个word文档。现在这篇文档已经能够在百度文库中直接检索到了,尊重他人版权,我这里就只发文章在文库中的地址了:

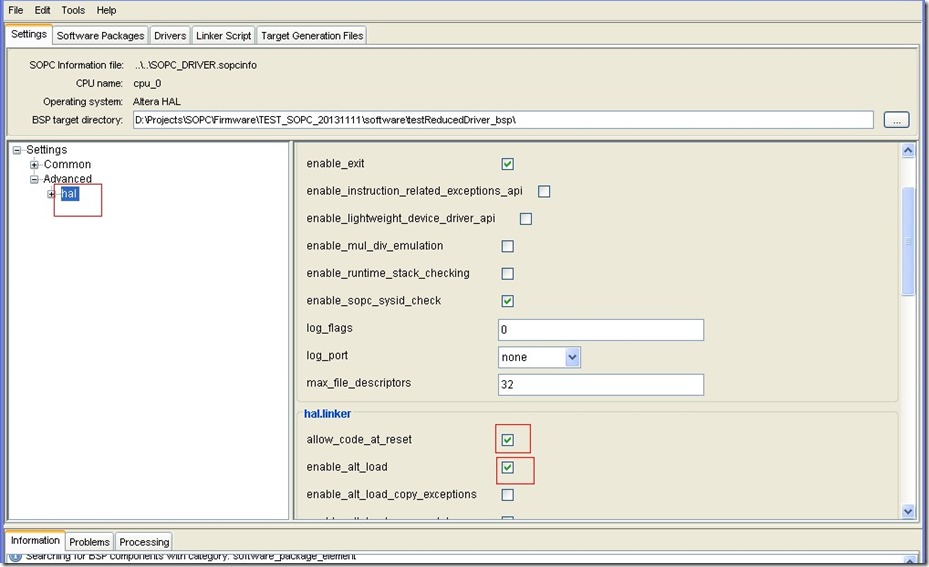

他的解决方案就是在BSP editor中修改了两个与bootloader位置相关的选项,将allow_code_at_reset和enable_alt_load两个选项的勾选取消了,如下图:

该文章中介绍,当创建不带EPCS控制器的NIOS II系统时,在NIOS II EDS中创建工程时,bsp editor中这两项是勾选上的。当创建了带EPCS控制器的NIOS II系统时,在NIOS II EDS中创建工程时,bsp editor中这两项是没有勾选上的。由此可知,当复位向量为SDRAM时,这两个选项应该勾选上。具体的原因见该文中作者在Altera提供的相关手册中找到原始解释。

当我在系统中将此两项勾选上后,再次生成bsp,然后编译、下载,处理器就能够正常执行复位了。

三、SOPC开发易错点归纳

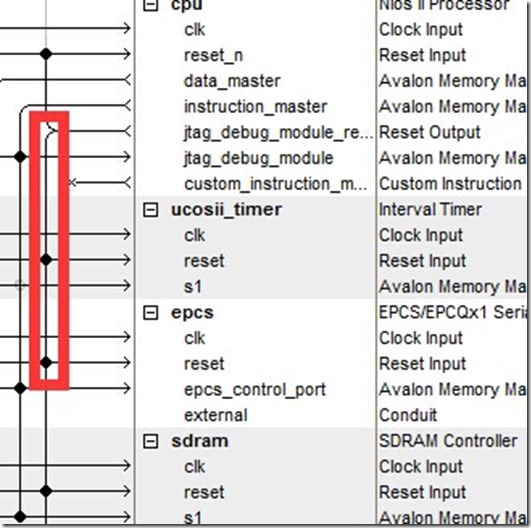

1、 在需要最终将程序固化到EPCS的系统中,需要添加EPCS/EPCQx1 Serial Flash Control。该控制器的reset信号一定要与jtag debug module reset信号(cpu模块中)相连,另外,最好其他所有模块的reset信号都与jtag debug module reset信号连接上,否则,在最终通过Flash Programmer固化程序时,会出错。如下图所示:

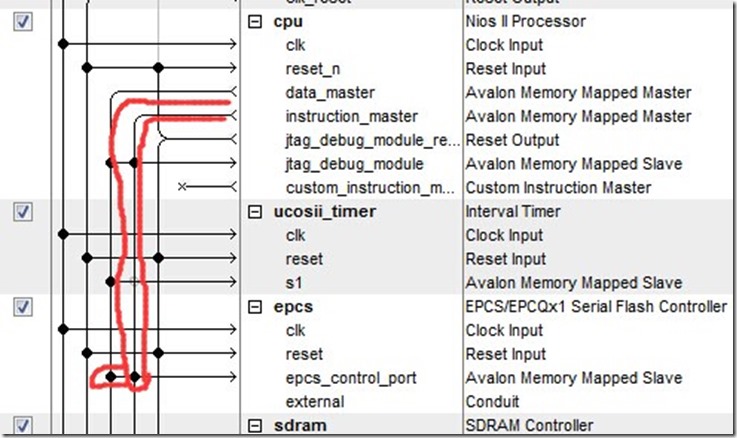

2、 epcs的Avalon Memory Mapped端口需要与CPU的data_master和instruction_master均进行连接。如下图所示:

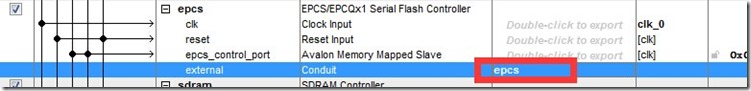

3、 EPCS的external信号需要导出到顶层(针对Cyclone III和Cyclone IV器件),以便进行引脚分配,如下图所示:

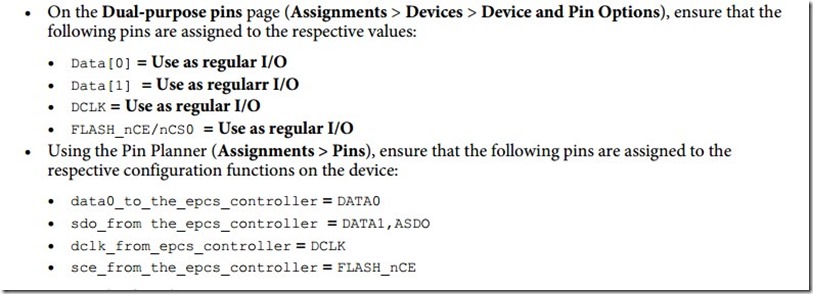

这里,导出到顶层后具体怎么分配引脚,在Altera的《Embedded Peripheral IP User Guide》中有相关介绍,

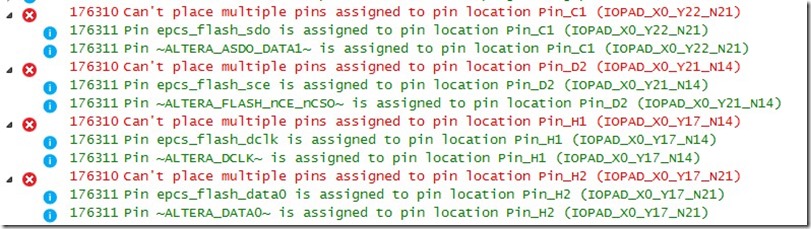

引脚分配完成后,需要在Quartus II中依次点击【Assigments】-> 【Device】,在弹出的界面中选择“Device and Pin Options”, 在Dual-Purpose Pins中设置DCLK、Data[0]、Data[1]/ASDO、FLASH_nCE/nCSO的Value为“Use as regular I/O”(双击值,然后在下拉菜单中选择)。否则Quartus II进行全编译会报如下错误:

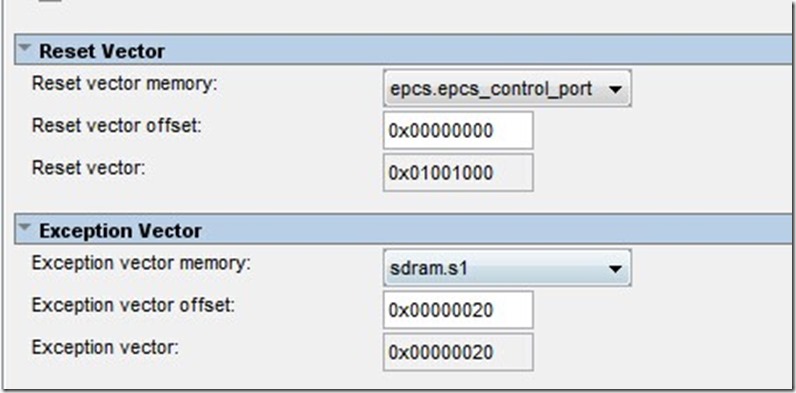

4、CPU的复位向量设置为EPCS,CPU的异常向量设置为内存(on_chip_memory或SDRAM),如下图所示:

四、拔掉下载器或者关闭NIOS II EDS软件,开发板上的系统即停止运行

问题原因

这是因为NIOS II系统中使用了JTAG UART,而在NIOS II系统中,JTAG UART的驱动是阻塞的,而且,该串口是使用JTAG模拟的,因此,NIOS II通过JTAG UART发送数据实际是将数据送入了JTAG的FIFO中,需要电脑端使用软件(如Eclipse中的Console)来读取数据,如果数据不被读走,则NIOS II中的程序会一直在这里等待数据被读走,才能发送下一个数据,因此卡在该处无法继续运行,就出现死机的现象。

解决建议

实际调试时建议使用RS232串口,不要使用JTAG UART。

五、编译NIOS软件工程提示” Permission denied”

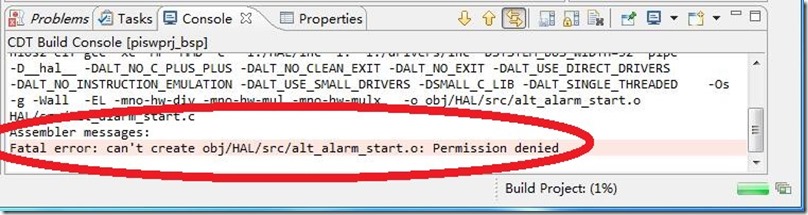

在编译一个由其他电脑创建的NIOS II软件工程时,提示:” Fatal error: can’t create obj/../../xxxxxxx.o, Permission denied”,如图所示:

问题原因

不同电脑对该文件夹的权限设置不一样,因此当文件被复制过来后,当前用户环境下没有权限对该文件进行编译,因此报错。

解决建议

首先关会NIOS II IDE软件,然后将该文件夹取得管理员所有权,再打开软件,编译就不会有问题了。

如有更多问题,欢迎加入芯航线 FPGA 技术支持群交流学习:一群 472607506(已满) 二群 615381411

小梅哥

芯航线电子工作室

以上是关于小梅哥SOPC学习笔记SOPC开发常见问题及解决办法集锦的主要内容,如果未能解决你的问题,请参考以下文章