译x86程序员手册15-5.2页转换

Posted 马如风

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了译x86程序员手册15-5.2页转换相关的知识,希望对你有一定的参考价值。

5.2 Page Translation 页转换

In the second phase of address transformation, the 80386 transforms a linear address into a physical address. This phase of address transformation implements the basic features needed for page-oriented virtual-memory systems and page-level protection.

在地址转换的第二阶段,80386将一个线性地址转换为物理地址。这个阶段的地址转换特性需要页定向的虚拟内存系统和页级的保护机制。

The page-translation step is optional. Page translation is in effect only when the PG bit of CR0 is set. This bit is typically set by the operating system during software initialization. The PG bit must be set if the operating system is to implement multiple virtual 8086 tasks, page-oriented protection, or page-oriented virtual memory.

这一步的页转换是可选的。仅当CR0寄存器的PG位被置位时,页转换才有效。该位是操作每户初始化时典型的设置。如果操作系统实现虚拟0886多任务、基于页的保护或者基于页的虚拟内存,PG位必须设置。

5.2.1 Page Frame 页帧

A page frame is a 4K-byte unit of contiguous addresses of physical memory. Pages begin onbyte boundaries and are fixed in size.

一个页帧是一个连续的4K大小的物理单元。页以字节为边界并且大小可变。

5.2.2 Linear Address 线性地址

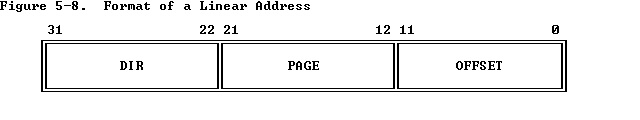

A linear address refers indirectly to a physical address by specifying a page table, a page within that table, and an offset within that page. Figure 5-8 shows the format of a linear address.

线性地址通过指定的页表目录、页表和页内偏移来直接引用一个物理地址。图5-8展示了一个线性地址的格式。

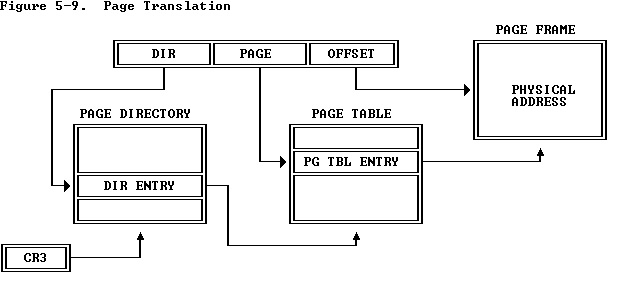

Figure 5-9 shows how the processor converts the DIR, PAGE, and OFFSET fields of a linear address into the physical address by consulting two levels of page tables. The addressing mechanism uses the DIR field as an index into a page directory, uses the PAGE field as an index into the page table determined by the page directory, and uses the OFFSET field to address a byte within the page determined by the page table.

图5-9展示了处理器如何通过参考二级页表将一个线性地址中的页目录(DIR)、页表(PAGE)和页内偏移(OFFSET)转换为物理地址。寻址机制将页目录(DIR)作为一个页目录的索引,将页表(PAGE)作为页目录中的页表索引,使用页内偏移(OFFSET)来寻址一个由页表决定的的页中的字节。

5.2.3 Page Tables 页表

A page table is simply an array of 32-bit page specifiers. A page table is itself a page, and therefore contains 4 Kilobytes of memory or at most 1K 32-bit entries.

页表是一个用来指定页的32位的数组。一个页表本身就是一个页,因些占用4K大小的内存并且包含最多1K个32位的项。

Two levels of tables are used to address a page of memory. At the higher level is a page directory. The page directory addresses up to 1K page tables of the second level. A page table of the second level addresses up to 1K pages. All the tables addressed by one page directory, therefore, can address 1M pages (2^(20)). Because each page contains 4K bytes 2^(12) bytes), the tables of one page directory can span the entire physical address space of the 80386 (2^(20) times 2^(12) = 2^(32)).

寻址一个内存中的页需要二级页表。其高位部分是一个页目录。页目录用来寻址最多1K个二级页表。一个二级页表可以寻址1K个页。因此,一个页目录可以用来寻址1M(2^20)个页。因为每个页包含4K(2^12)个字节,所以一个页目录可以直接寻址的页面可以表示80386的整个物理地址空间(2^20 * 2^12 = 2^32)。

The physical address of the current page directory is stored in the CPU register CR3, also called the page directory base register (PDBR).

当前页目录的物理地址存储在CR3寄存器中,也叫做页目录基址寄存器(PDBR)。

Memory management software has the option of using one page directory for all tasks, one page directory for each task, or some combination of the two. Refer to Chapter 10 for information on initialization of CR3 . Refer to Chapter 7 to see how CR3 can change for each task .

内存管理系统可以选择用所有任务使用一个页目录,或者每个任务使用一个页目录,或者两个任务使用一个。初始化CR3寄存器的更多信息参见第10章。如何为每个任务修改CR3寄存器见第7章。

5.2.4 Page-Table Entries 页表项

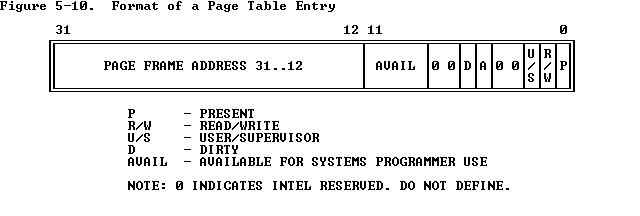

Entries in either level of page tables have the same format. Figure 5-10 illustrates this format.

各级别的页表项都有同样格式。图5-10解释了这个格式。

5.2.4.1 Page Frame Address 页帧地址

The page frame address specifies the physical starting address of a page. Because pages are located on 4K boundaries, the low-order 12 bits are always zero. In a page directory, the page frame address is the address of a page table. In a second-level page table, the page frame address is the address of the page frame that contains the desired memory operand.

页帧地址指定一个页的物理起始地址。因为页总是以4K为边界定位,所以其低12位训是0。在页目录中,页帧地址是一个页表的地址。在二级页表中,页帧地址是一个包含内存操作所需要的页帧地址。

5.2.4.2 Present Bit 存在位

The Present bit indicates whether a page table entry can be used in address translation. P=1 indicates that the entry can be used.

存在位表明一个页表项是否可以被地址转换设备使用。当P为1时表明可用。

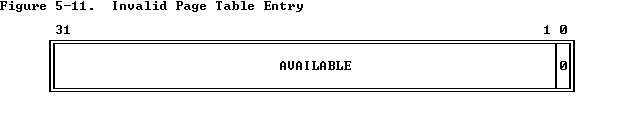

When P=0 in either level of page tables, the entry is not valid for address translation, and the rest of the entry is available for software use; none of the other bits in the entry is tested by the hardware. Figure 5-11 illustrates the format of a page-table entry when P=0.

无论在哪级页表中,当P为0时,该项对于页地址转换不可用,余下各位可以被软件使用;硬件不会检测其他位。图5-11解释了当P为0时页表项的格式。

If P=0 in either level of page tables when an attempt is made to use a page-table entry for address translation, the processor signals a page exception. In software systems that support paged virtual memory, the page-not-present exception handler can bring the required page into physical memory. The instruction that caused the exception can then be reexecuted. Refer to Chapter 9 for more information on exception handlers .

当P为0时,无论在哪级页表中,试图将一个页表项转换为地址时,处理器触发一个异常。在支持页级虚拟内存的软件系统中,页不存在异常处理例程可以用来将一个需求页装入物理内存。更多关于异常处理信息参见第9章。

Note that there is no present bit for the page directory itself. The page directory may be not-present while the associated task is suspended, but the operating system must ensure that the page directory indicated by the CR3 image in the TSS is present in physical memory before the task is dispatched . Refer to Chapter 7 for an explanation of the TSS and task dispatching.

注意,页目录本身没有存在位。当相关任务被挂起时,页目录可以不存在。但操作系统必须确保TSS映像中CR3所引用的页目录在任务被分派时可用。关于TSS和任务分派参见第7章。

5.2.4.3 Accessed and Dirty Bits 访问位和脏位

These bits provide data about page usage in both levels of the page tables. With the exception of the dirty bit in a page directory entry, these bits are set by the hardware; however, the processor does not clear any of these bits.

在两级的页表中这些位都用来表示页数据是否被使用。在页目录项中的脏位引起的异常时,由硬件置位;然而,处理器并不清除这些位。

The processor sets the corresponding accessed bits in both levels of page tables to one before a read or write operation to a page.

在读写一个页之前,处理器会对两级页表的置为1。

The processor sets the dirty bit in the second-level page table to one before a write to an address covered by that page table entry. The dirty bit in directory entries is undefined.

当页表项中地址被覆盖前,处理器将二级页表的脏位置为1。页目录中的脏位没有定义。

An operating system that supports paged virtual memory can use these bits to determine what pages to eliminate from physical memory when the demand for memory exceeds the physical memory available. The operating system is responsible for testing and clearing these bits.

当内存需求达到物理内存上限时,支持页虚拟内存的操作系统使用这些位来决定哪些页可以从物理内存中移除。操作系统负责测试和清除这些位。

Refer to Chapter 11 for how the 80386 coordinates updates to the accessed and dirty bits in multiprocessor systems.

参见第11章关于80386在多处理器系统中如何协调更新访问位和脏位。

5.2.4.4 Read/Write and User/Supervisor Bits 读/写位和用户/超级用户位

These bits are not used for address translation, but are used for page-level protection, which the processor performs at the same time as address translation . Refer to Chapter 6 where protection is discussed in detail.

地址转换并不使用这些位,在处理器执行页转换的同时页保护机制使用它们。参见第6章在何处进行保护对此进行了讨论。

5.2.5 Page Translation Cache 页转换缓冲

For greatest efficiency in address translation, the processor stores the most recently used page-table data in an on-chip cache. Only if the necessary paging information is not in the cache must both levels of page tables be referenced.

为加速页转换,处理器将最近使用的页表数据存储在一个芯片缓存中。仅当需要的页信息不在缓存中时,二级页表信息必须被刷新。

The existence of the page-translation cache is invisible to applications programmers but not to systems programmers; operating-system programmers must flush the cache whenever the page tables are changed. The page-translation cache can be flushed by either of two methods:

对于应用程序而言,页转换缓存是不可见的,但对于系统程序可见;操作系统设计者必须在页表修改时刷新缓存。页转换缓存可以使用以下两种方法刷新:

- By reloading CR3 with a MOV instruction; for example:

使用MOV指令重新载入CR3;例如:

MOV CR3, EAX

- By performing a task switch to a TSS that has a different CR3 image than the current TSS . (Refer to Chapter 7 for more information on task switching.)

执行任务切换时,一个与当前TSS不同的CR3映像会装入TSS,也会刷新缓存。(参见第7章查看任务切换的更多信息。)

以上是关于译x86程序员手册15-5.2页转换的主要内容,如果未能解决你的问题,请参考以下文章