V3学院带你学习-如何让chipscope里面的信号不被优化掉

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了V3学院带你学习-如何让chipscope里面的信号不被优化掉相关的知识,希望对你有一定的参考价值。

此文章为原创出自 V3学院 www.v3edu.org,FPGA培训专家

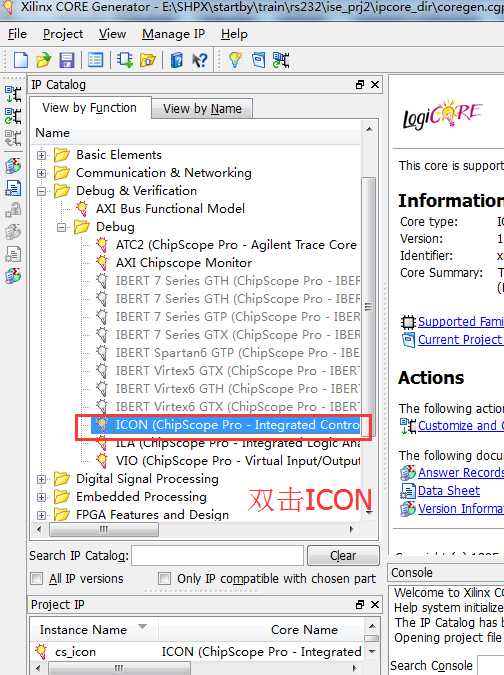

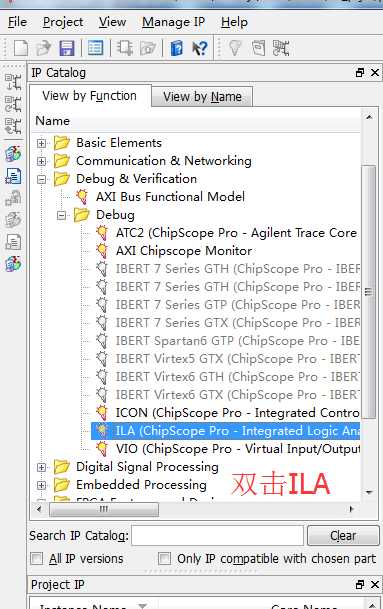

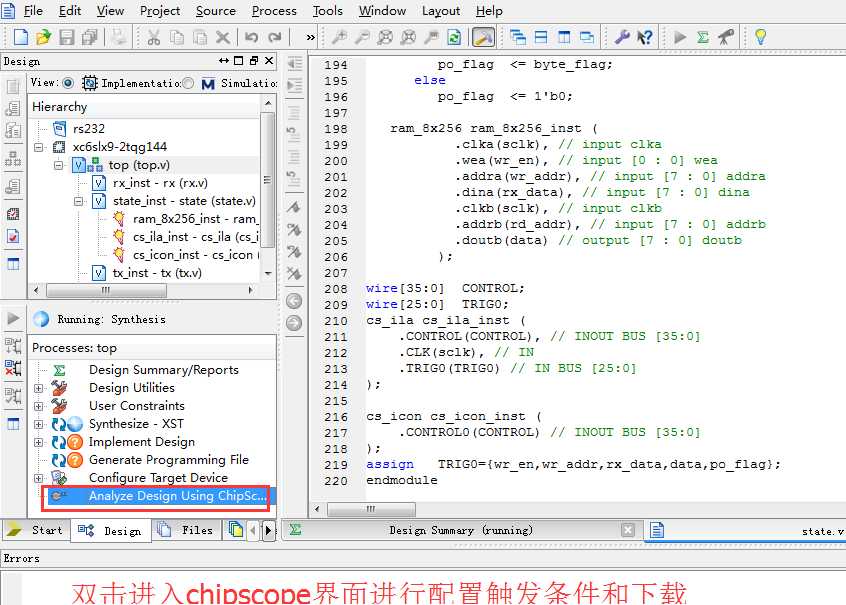

ise里面的chipscope是一个非常实用的在线逻辑分析仪,在我们仿真通过了而实际下载到板卡上的时候,也有可能出错,这时这款软件的作用就非常明显了。但是,也有让人非常不舒适的地方:很多信号常常不能抓,这是因为ise里面的综合工具把一些信号优化掉了。而恰好我们有时是很需要查看这些信号的,用以下的方法可以轻松的让模块内部所定义的所有信号都呈现在chipscope的波形窗口里面,下面的方法采用的是调用ip核的方法添加chipscope:

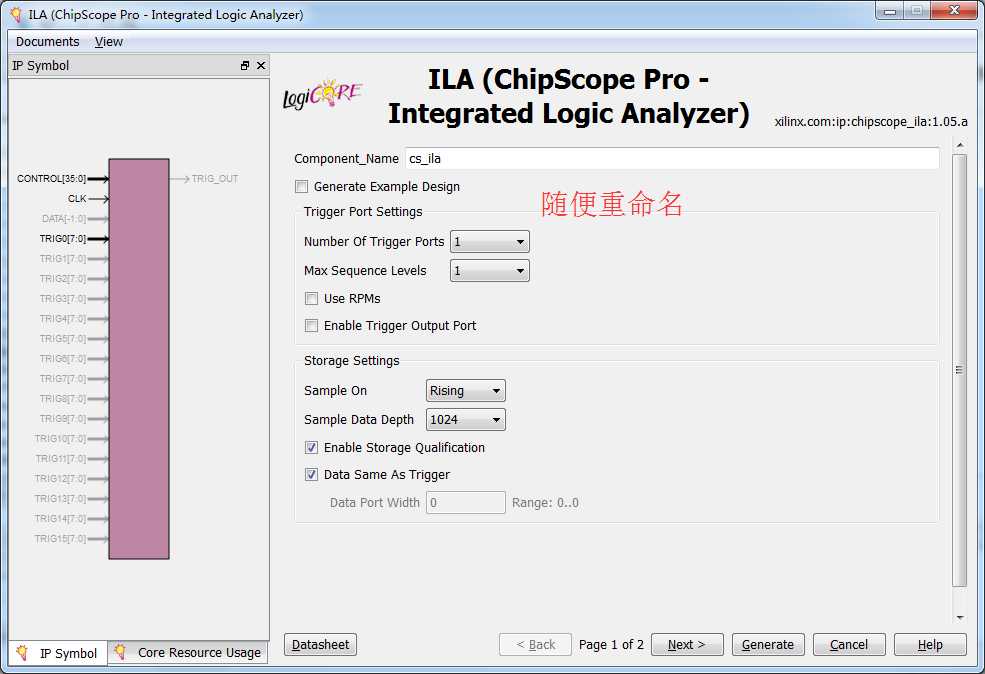

重命名后,点“generate”。

重命名后,点击“next”。

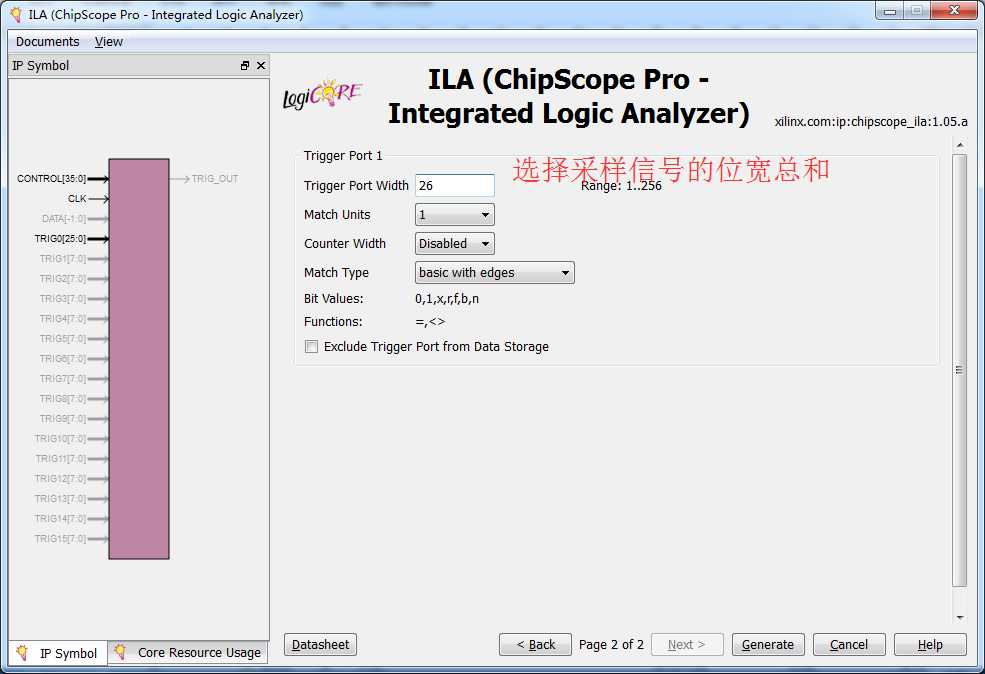

填入位宽总和之后,点击“generate”。

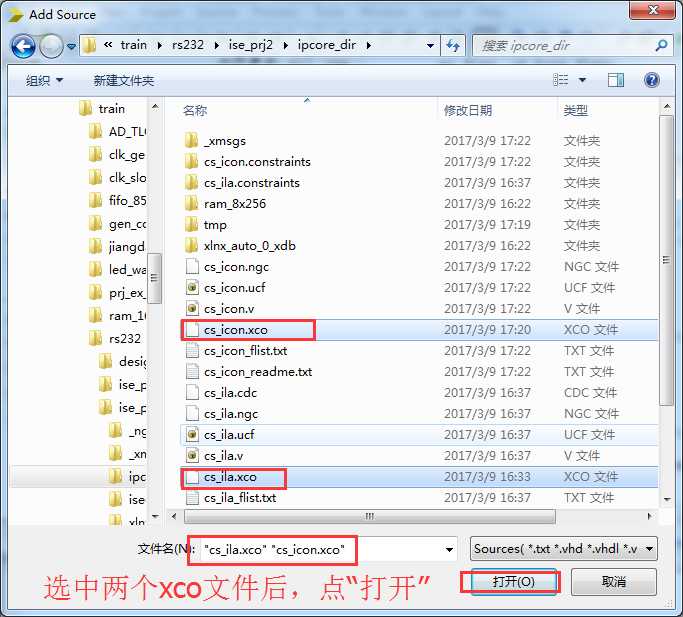

回到工程界面,并把两个ip和的xco文件添加到工程里面。

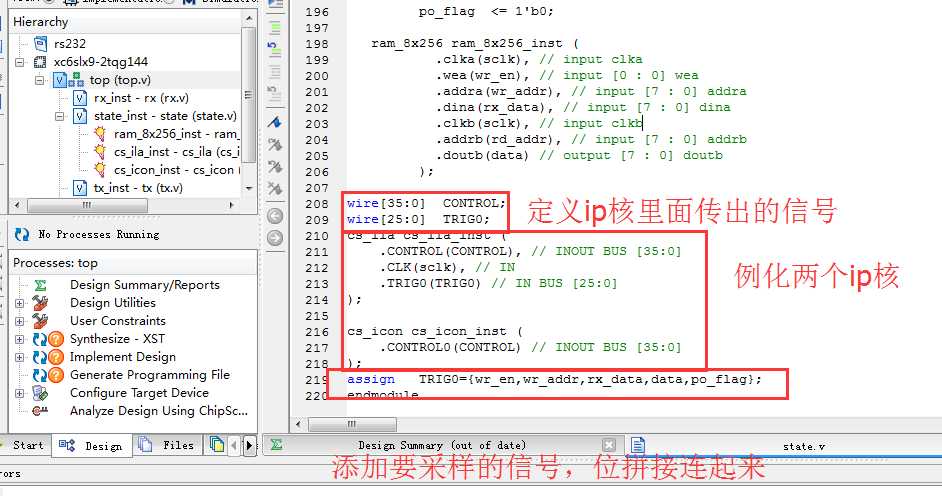

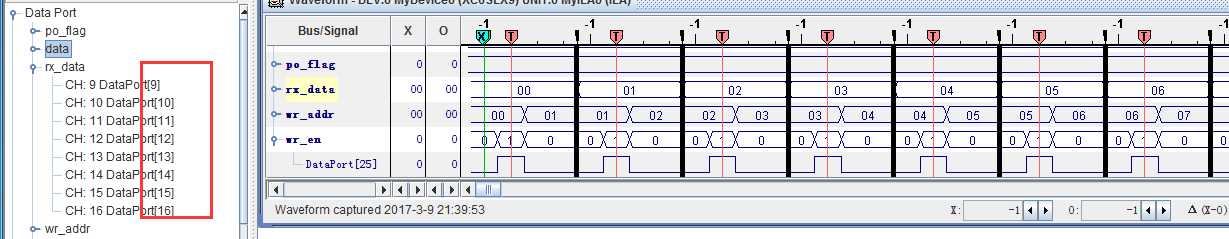

TRIG0={wr_en,wr_addr,rx_data,data,po_flag};这些变量的位宽加起来为26位。

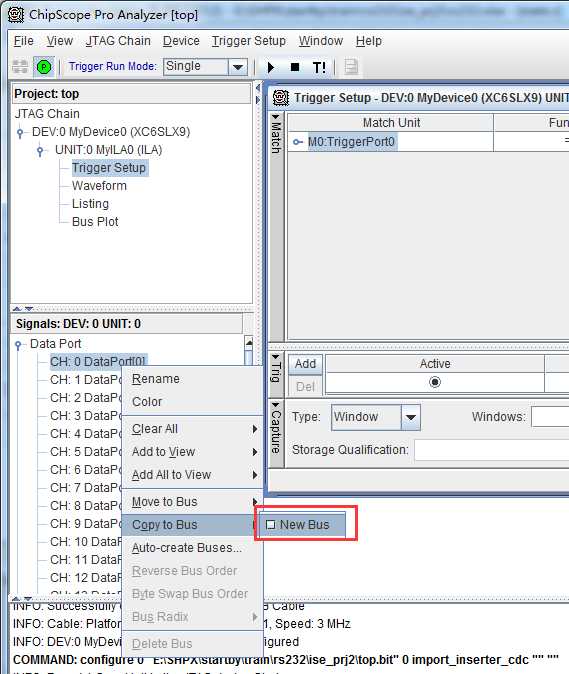

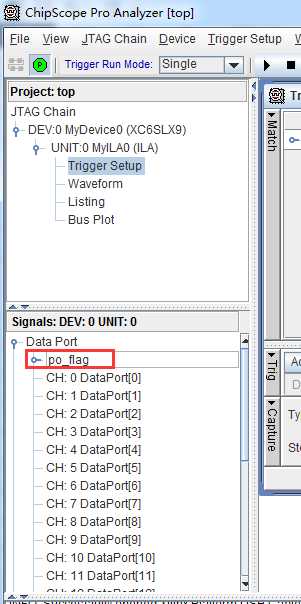

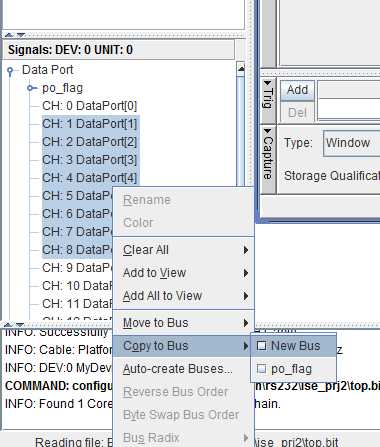

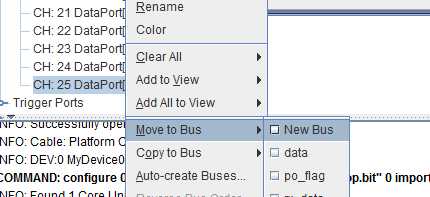

依次选中上图中的几个选项,新建一个总线,并取名叫“po_flag”。

上面dataport[1]~data_port[7]命名为”data”。

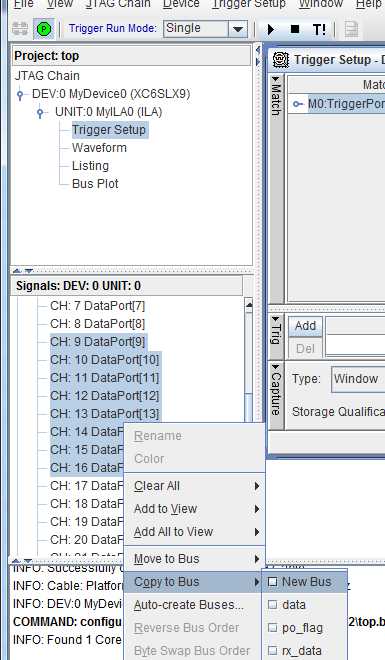

上面dataport[9]~dataport[16]命名为“rx_data”。

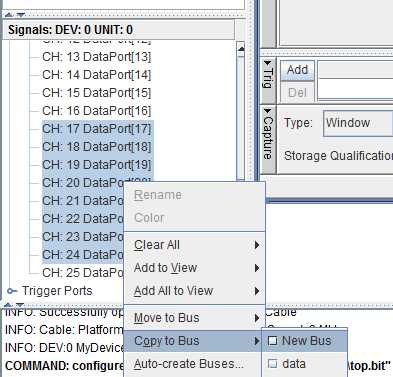

上面dataport[17]~dataport[24]命名为“wr_addr”。

Dataport[25]命名为“wr_en”。

调整每个变量的排列顺序,从小到大,如下:(选中变量-右键-reverse bus order可以调整)。

此文章为原创出自 V3学院 www.v3edu.org

以上是关于V3学院带你学习-如何让chipscope里面的信号不被优化掉的主要内容,如果未能解决你的问题,请参考以下文章

V3学院带你学习-缩短汉明码Hamming(12,8)的FPGA实现