nios II--实验7——数码管IP硬件部分

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了nios II--实验7——数码管IP硬件部分相关的知识,希望对你有一定的参考价值。

数码管

硬件开发

新建原理图

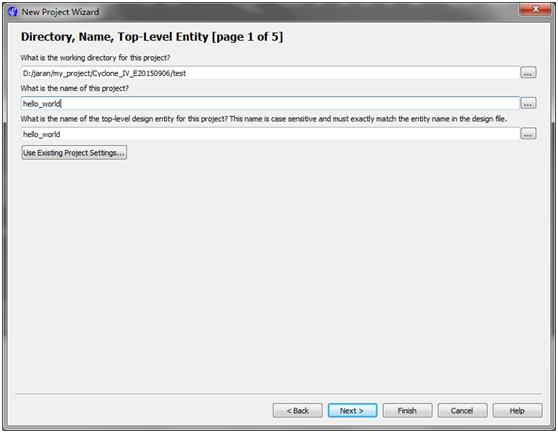

- 打开Quartus II 11.0,新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击?Next>?进入下一步。分别设置工程工作目录、工程名称。这里需要注意的是工程工作目录中请使用英文,不要含有空格等,否则在后面使用Nios II IDE的时候会出现问题。设置好后如图1所示。然后进行下一步。这里工程命名为lab6_seg

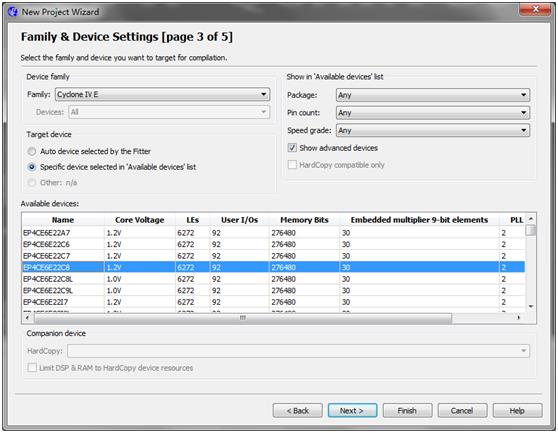

2、添加已经存在的文件,这里没有需要添加的文件,直接单击?Next>?进入下一步。进行器件设置。使用的?是Cyclone IV家族的?EP4CE6E22C8芯片,选择好后直接进入下一步。进行EDA工具设置,由于工程中不进行仿真等,故不进行设置,如果需要进行ModelSim仿真,则在Simulation行中,选择Tool Name?为ModelSim-Altera(这里根据所安装的ModelSim版本进行选择),Format(s)选择为Verilog HDL(这里也是根据所掌握的硬件描述语言进行选择)。点击?Next>?,进入了Summary(摘要)页面,然后单击?Finish?完成即可。

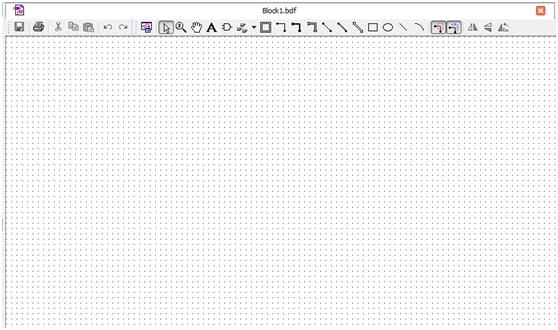

3、新建?Block Diagram/Schematic File?(方块图/原理图文件)。单击?File -> New..,选择Design Files中的Block Diagram/Schematic File,单击OK即可。

?

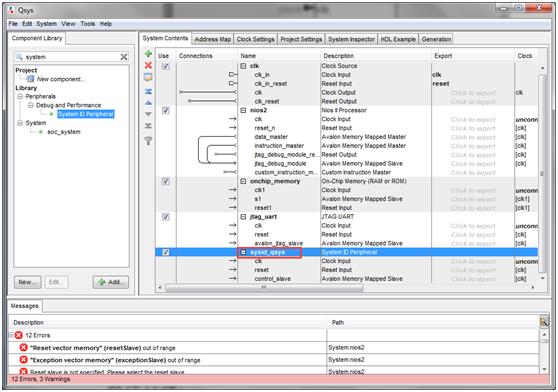

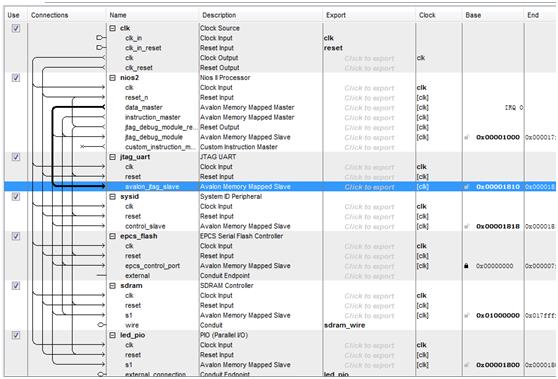

QSys调用模块

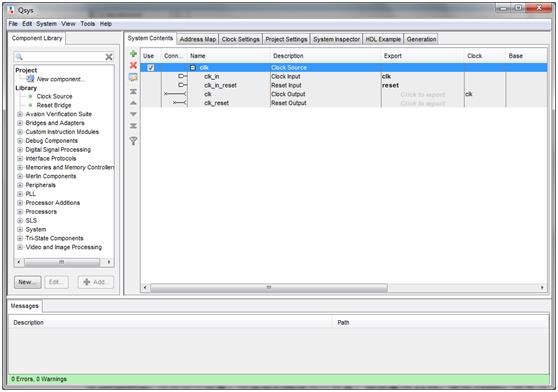

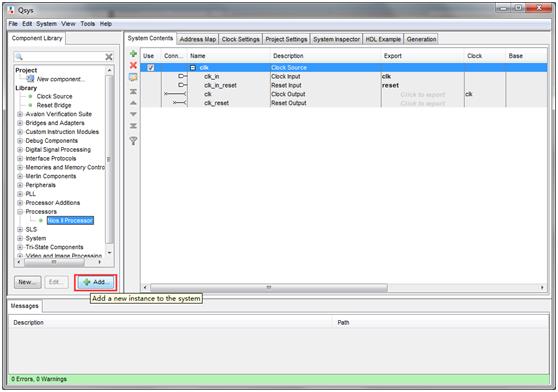

- 启动Qsys?工具,进行IP模块的调用。单击?Tools -> Qsys

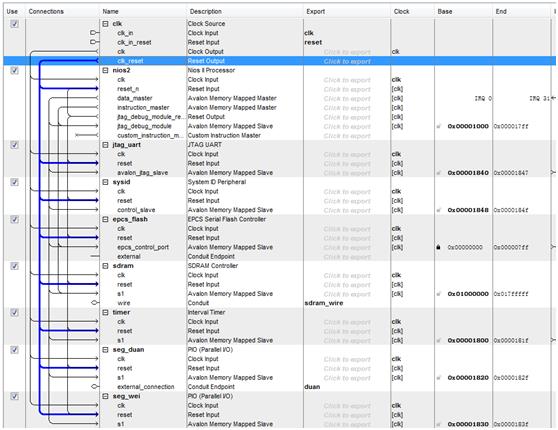

?,进入Qsys设置界面。系统已经默认添加了时钟模块,名称为?clk_0?,这里选中?clk_0,右击,选择Rename,将其名称更改为clk。以下再添加任何模块,都进行类似的名称更改,更改名称的方法类似,就不在重复叙述了。

?,进入Qsys设置界面。系统已经默认添加了时钟模块,名称为?clk_0?,这里选中?clk_0,右击,选择Rename,将其名称更改为clk。以下再添加任何模块,都进行类似的名称更改,更改名称的方法类似,就不在重复叙述了。

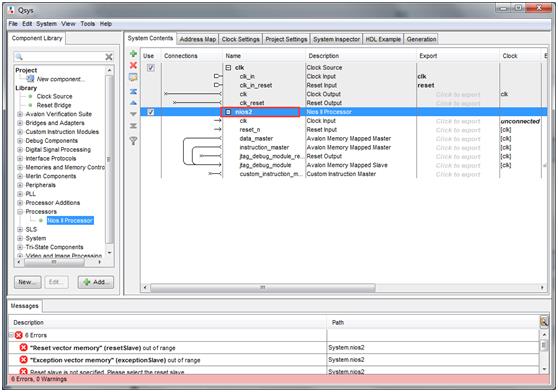

- 添加软核处理器的各部分模块。总共需要添加

Nios II Processor、

JTAG UART、

System ID Peripheral

EPCS Serial Flash Controller

Sdram controller

Pio

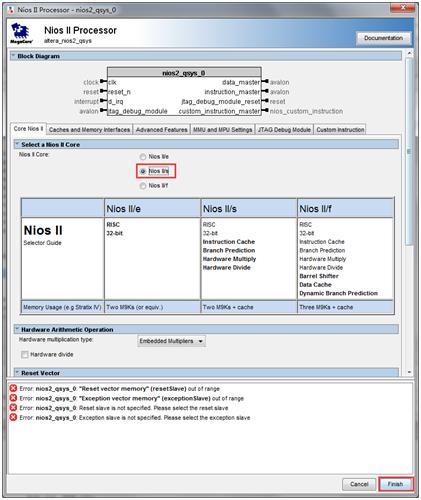

timer

这7个模块。首先熟悉一下?Qsys?的界面。左面Component Library,是系统提供的元件库,里面有一些构成处理器的常用模块。右面是已经添加到系统的模块,也就是说,Nios II?软核处理器是可以定制的,根据具体需要来。在Component Library中搜索Nios II Processor,双击即可进行配置。首先需要选择的是Nios II?核心的类型。Nios II?软核的核心共分成三种,为e型、s型以及f型。e型核占用的资源最少,功能也最简单,速度最慢。s型核占用资源其次,功能和速度较前者都有所提升,f型核的功能最多,速度最快,相应的占用资源也最多,选择的时候根据需求和芯片资源来决定,这里选择s核。然后单击?Finish,结束当前配置。

?

?

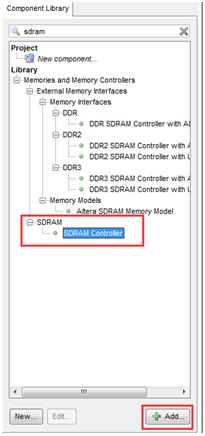

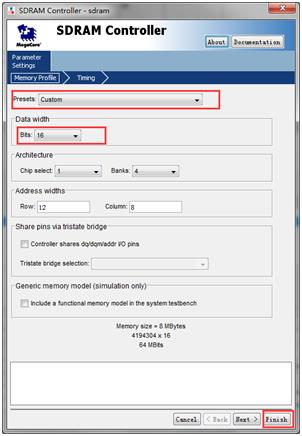

- 添加SDRAM Controller,这里使用的SDRAM芯片,大小为64M??????B = 1M x 16Bit x 4Banks,具体的其他内容大家可以查看其datesheet。

重命名为sdram;

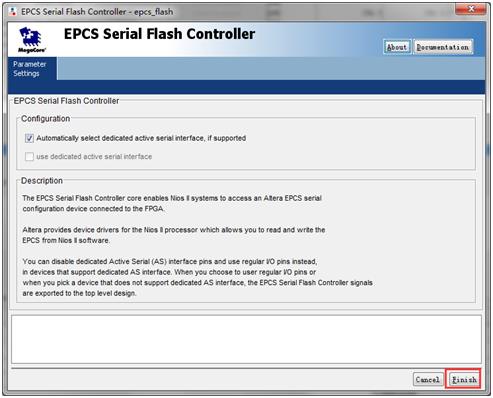

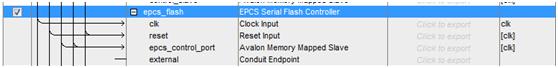

- 添加EPCS/EPCQx1 Serial Flash Controller,这里不用进行任何设置,直接单击Finish完成即可。

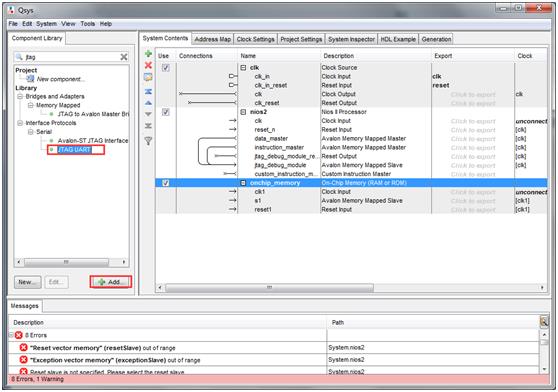

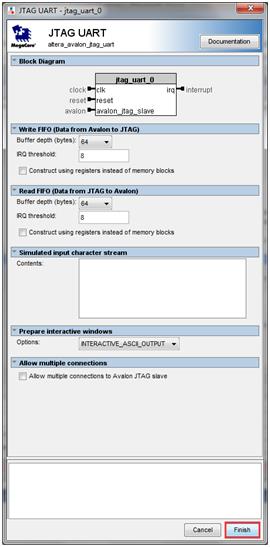

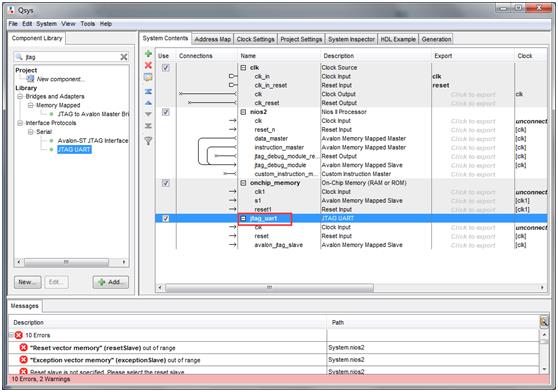

- 添加Jtag下载调试接口。在元件库中搜索?jtag uart。双击进行设置。由于系统没有特殊要求,因此这里选择默认配置即可。单击?Finish?结束当前配置。

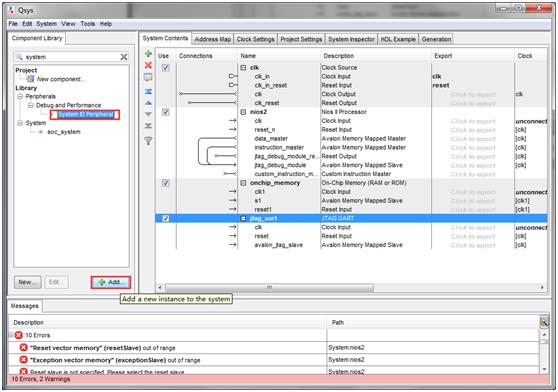

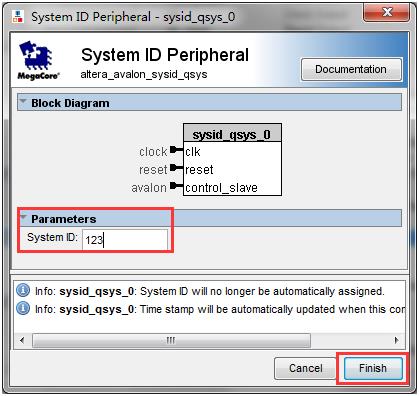

- 添加系统ID模块。系统ID是系统与其他系统区别的唯一标识。在元件库中搜索?system id peripheral,双击进行设置。这里随便进行设置,如设置为123。单击?Finish,结束当前配置。

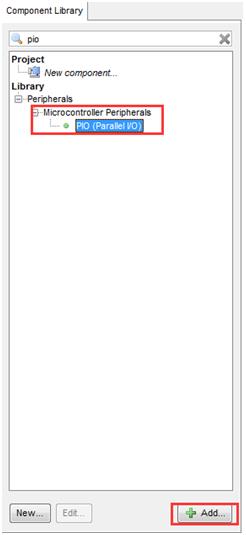

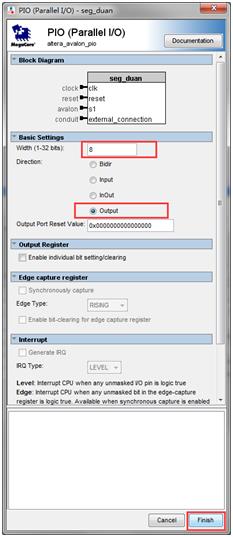

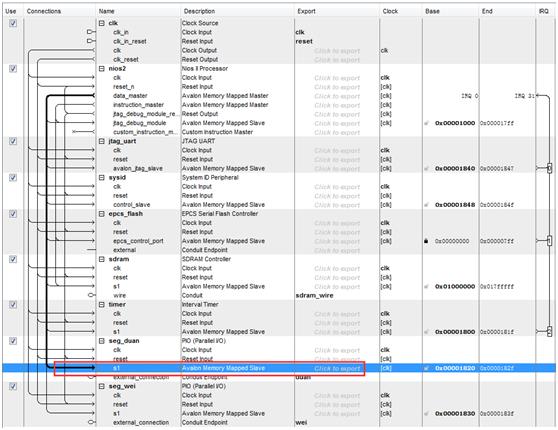

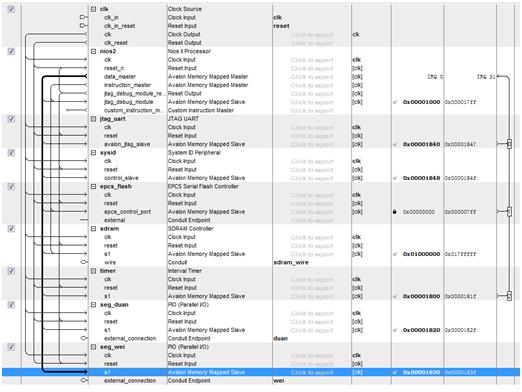

- 添加PIO,作为数码管的段选信号。双击打开后,根据实际需要选择位宽(Width)和方向(Direction),所以Width设置为8,Direction设置为Output。单击Finish完成设置。

重命名如下:

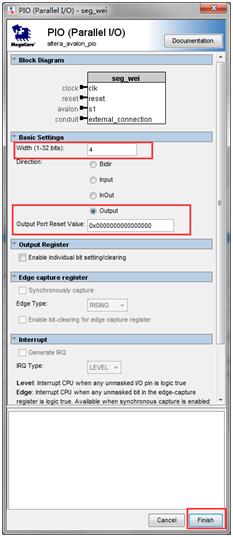

- 添加PIO,作为数码管的位选信号。双击打开后,根据实际需要选择位宽(Width)和方向(Direction),所以Width设置为4,Direction设置为Output。单击Finish完成设置。

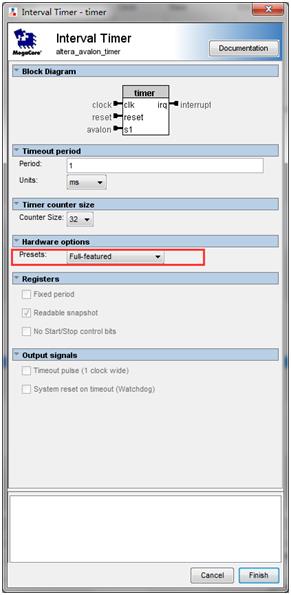

- 添加定时器模块timer

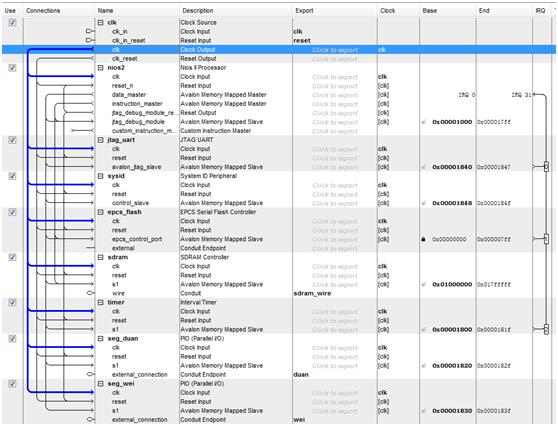

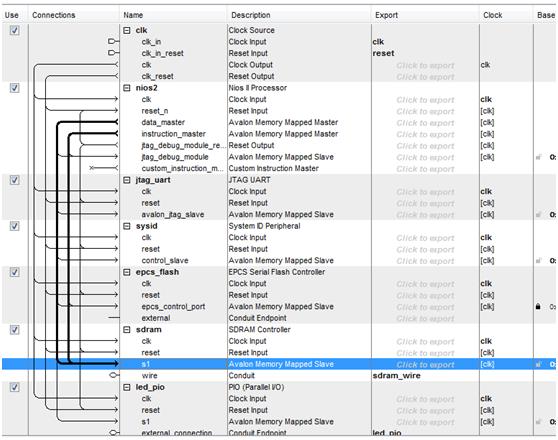

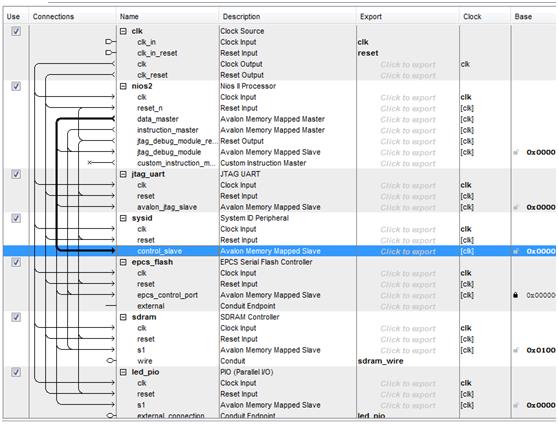

- 连线,即将右面?Connections栏目中的相关线通过设置节点进行连接。首先所有模块的clk连接起来。

然后片内存储器sdram的s1和处理器nios2的data_master和instruction_master相连。

JTAG调试模块jtag_uart的avalon_jtag_slave和处理器nios2的data_master相连。

系统ID模块sysid_qsys的control_slave和处理器nios2的data_master相连。

?

- Seg_duan模块的S1连接处理器nios2的data_master;

设置Seg_duan的输出端口,并重命名端口名;

- Seg_wei模块的S1连接处理器nios2的data_master;

设置Seg_wei的输出端口,并重命名端口名;

- timer模块的S1连接处理器nios2的data_master;

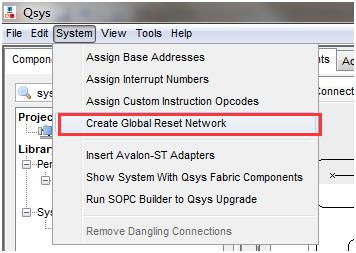

- 设置复位信号。

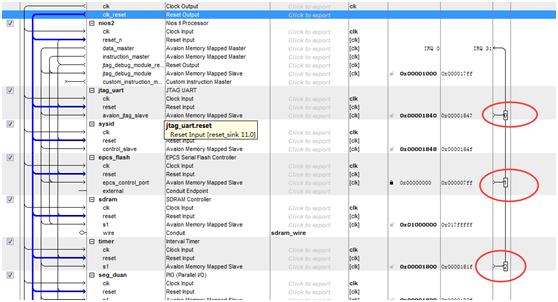

- 处理器nios2的中断和jtag_uart的中断、epcs_flash的中断、定时器中断相连接。

- epcs_flash后面的小锁单击,将其锁上。

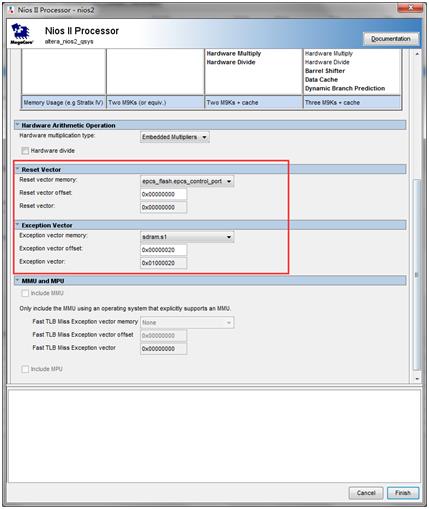

- 进行软核的相关设置。首先双击nios2,进入处理器设置模块。在Core Nios II标签下,Reset vector memory设置为epcs_flash.epcs_control_port,Exception vector memory设置为sdram.s1,然后单击Finish完成设置。

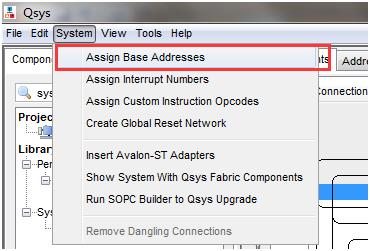

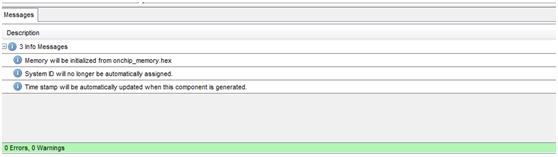

- 单击?System -> Assign Base Addresses,这时候会发现下部Messages窗口中原先的错误全部没有了,变为0 Errors,0 Warnings。如果不是这个结果,返回去按步骤检查。

- 单击?File -> Save,进行保存,这里保存文件名为lab6_seg。

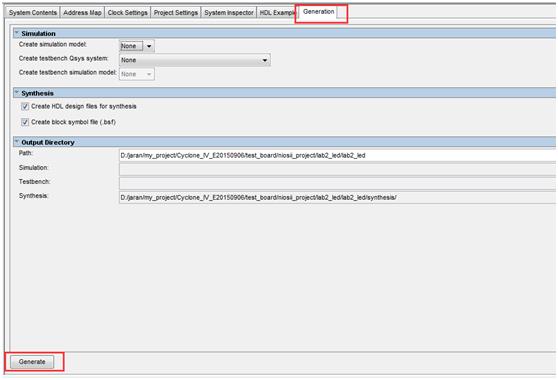

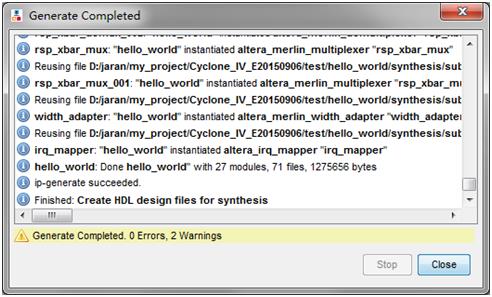

- 最后,选择Generation选项卡,设置Create simulation model为None,然后单击下面的Generate,进行生成。时间较长,大家耐心等待。

- 完成后单击close即可,然后关闭Qsys回到Quartus II界面。

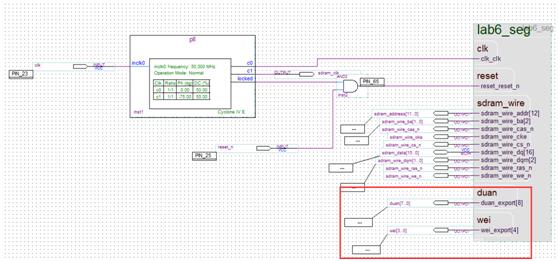

原理图添加IP模块

参照实验二(led),重新调用脚本对引脚进行配置

以上是关于nios II--实验7——数码管IP硬件部分的主要内容,如果未能解决你的问题,请参考以下文章