s5pv210——初始化时钟

Posted biaohc

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了s5pv210——初始化时钟相关的知识,希望对你有一定的参考价值。

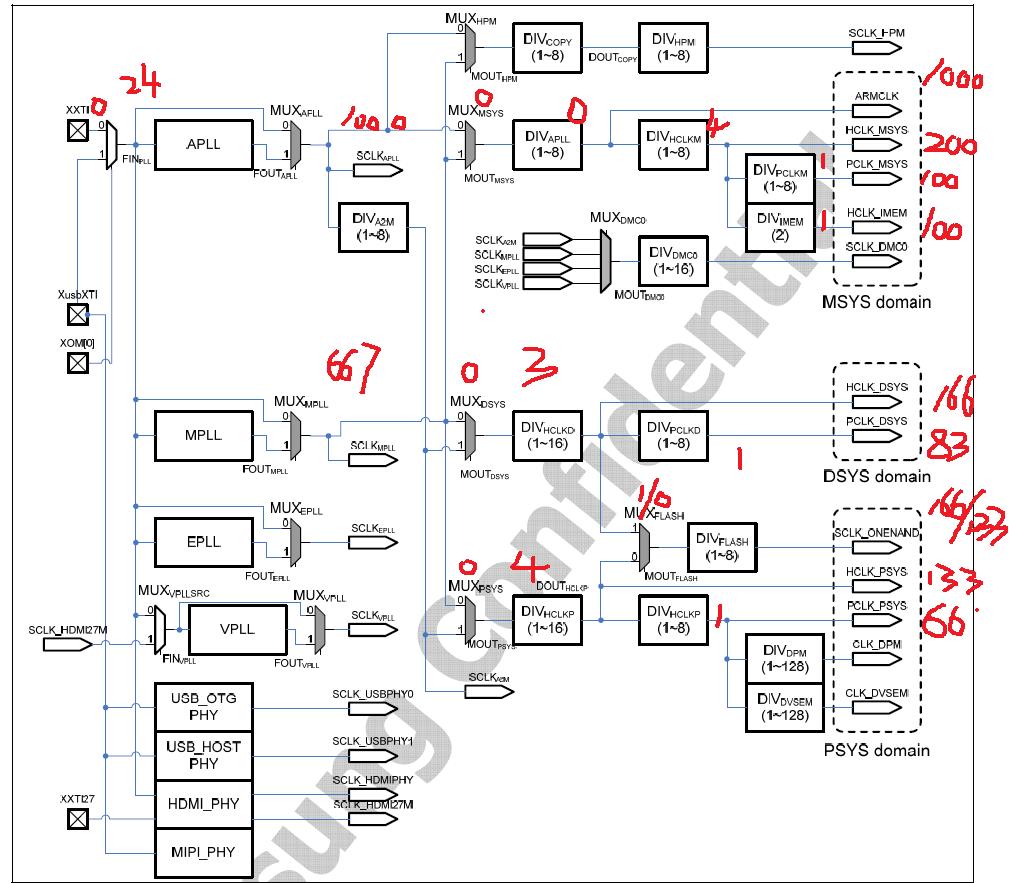

1:s5pv210的时钟域

MSYS Domain:为处理器、3D、intc(中断)、DMC0、DMC1、IRAM、IROM提供时钟,HCLK_MSYS:200MHZ、PCLK_MSYS:100MHz

DSYS Domain:为音视频等设备提供时钟,HCLK_DSYS:166MHZ、PCLK_DSYS:83MHz

PSYS Domain:为外设提供时钟,如GPIO、I2C、PWM、UART、WDT等。HCLK_PSYS:133MHZ、PCLK_PSYS:66MHz

2:s5pv210的晶振

s5pv210有4个晶振时钟,

XRTCXTI:提供32.768KHz,RTC 使用;XRTCXTI and XRTCXTO pins

XXTI:CMU and PLL使用这个时钟为APLL、MPLL、VPLL、EPLL提供时钟。推荐频率24MHz。XXTI and XXTO pins

XUSBXTI:为APLL、MPLL、VPLL、EPLL、USB PHY提供时钟,推荐24MHz。XUSBXTI and XUSBXTO pins.

XHDMIXTI :27MHz,VPLL、HDMI PHY为TV解码器提供54MHz时钟。XHDMIXTI and XHDMIXTO pins

3: s5pv210推荐时钟设置:

根据推荐值来设置相应的MUX开关、PLL锁相环倍频、DIV分频器的值来得到相应的时钟。

对应下面框图进行寄存器设置;

4:相应寄存器

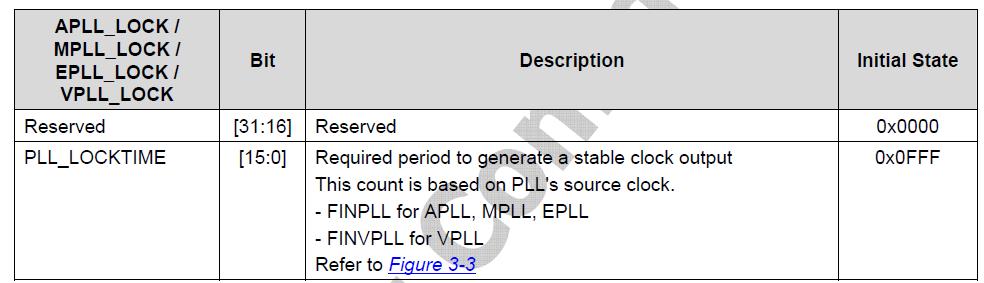

xPLL_LOCK寄存器,设置locking period,一般为默认值。因为PLL倍频需要一定时间才能达到相应的频率。

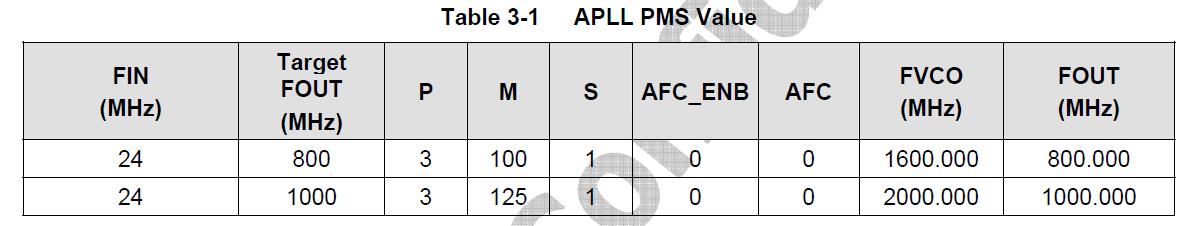

APLL_CON0寄存器:用来设置APLL的倍频率,

FOUT = MDIV X FIN / (PDIV × 2SDIV-1)

频率1000 MDVI:125、 PDIV:3、 SDIV:1;FOUT = MDIV X FIN / (PDIV × 2SDIV-1) 根据公式计算 FOUT = 1000MHz;

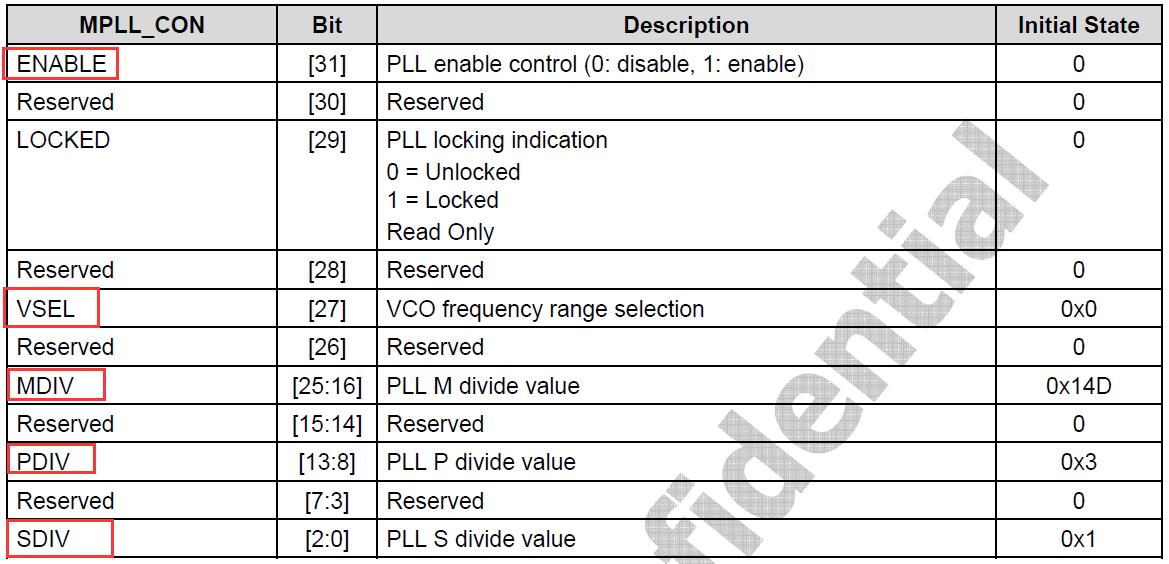

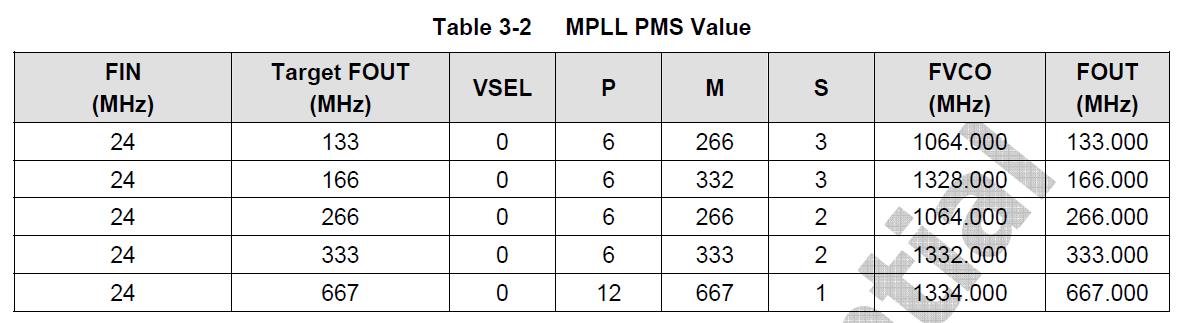

MPLL_CON:寄存器,设置MPLL的倍频率

FOUT = MDIV X FIN / (PDIV X 2SDIV)

SDIV:1、 PDIV:12、 MDIV:667;FOUT = 667MHz;

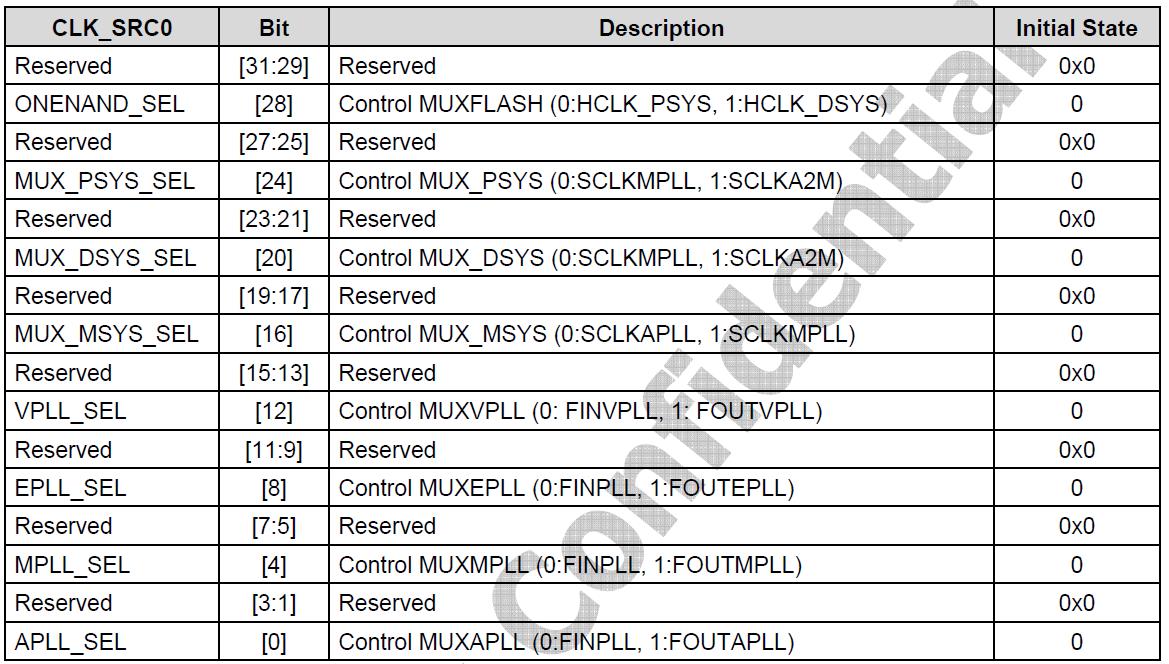

CLK_SRC0 寄存器,设置MUX开关。

设置各时钟前首先要关闭4个PLL的MUX开关,设置好相应寄存器以后在把PLL的MUX开关打开。

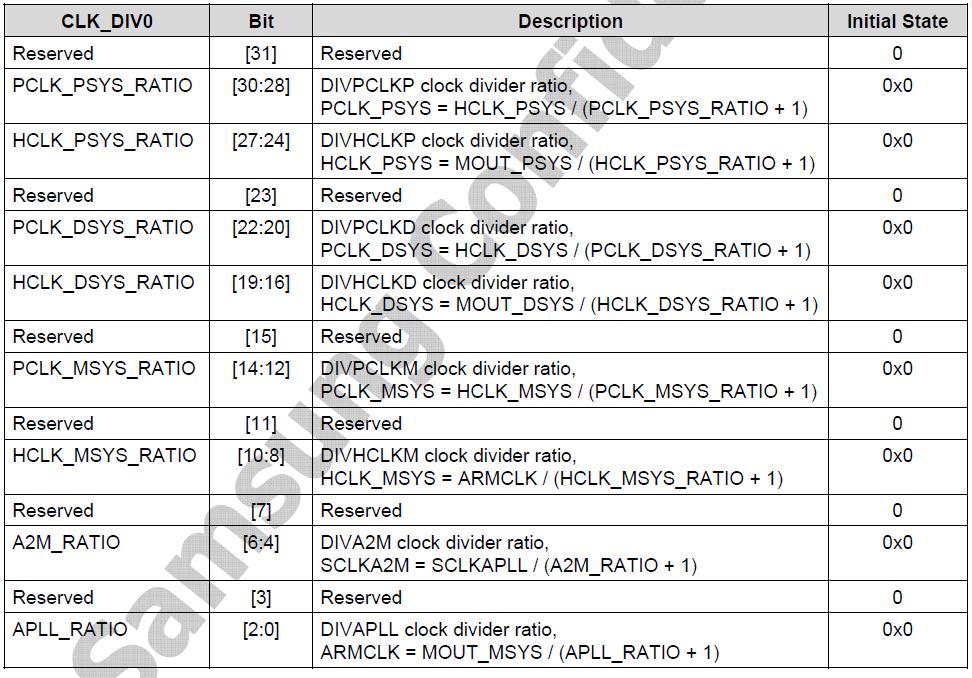

CLK_DIV0寄存器:

设置各个分频器的值,最终得到各个时钟。

5:实战代码

#define _REG_APLL_LOCK *((unsigned int*)0xE0100000) #define _REG_MPLL_LOCK *((unsigned int*)0xE0100008) #define _REG_EPLL_LOCK *((unsigned int*)0xE0100010) #define _REG_VPLL_LOCK *((unsigned int*)0xE0100020) #define _REG_APLL_CON0 *((unsigned int*)0xE0100100) #define _REG_MPLL_CON *((unsigned int*)0xE0100108) #define _REG_CLK_SRC0 *((unsigned int*)0xE0100200) #define _REG_CLK_DIV0 *((unsigned int*)0xE0100300) #define APLL_SDIV (1) #define APLL_PDIV (3) #define APLL_MDIV (125) #define APLL_EN (1) #define MPLL_SDIV (1) #define MPLL_PDIV (12) #define MPLL_MDIV (667) #define MPLL_EN (1) void clock_init(void) { //第一步关闭PLL的MUX开关 _REG_CLK_SRC0 = 0x0; //第二步设置LOCK时间,设置为默认值0x0FFF _REG_APLL_LOCK = 0x0FFF; _REG_MPLL_LOCK = 0x0FFF; _REG_EPLL_LOCK = 0x0FFF; _REG_VPLL_LOCK = 0x0FFF; //第三步设置DIV分频器的值 _REG_CLK_DIV0 = 0x14131400; //第四步设置APLL、MPLL的倍频值。 _REG_APLL_CON0 = (APLL_EN<<31) | (APLL_MDIV<<16) | (APLL_PDIV<<8) | (APLL_SDIV<<0); _REG_MPLL_CON = (MPLL_EN<<31) | (MPLL_MDIV<<16) | (MPLL_PDIV<<8) | (MPLL_SDIV<<0); //第五步设置MUX开关 _REG_CLK_SRC0 = 0x1111; }

以上是关于s5pv210——初始化时钟的主要内容,如果未能解决你的问题,请参考以下文章