STM32F407加FPGA用FSMC总线怎么连接

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STM32F407加FPGA用FSMC总线怎么连接相关的知识,希望对你有一定的参考价值。

参考技术A STM32F407的FSMC总线连接FPGA,FPGA内部设置为FSMC与SRAM直接连接。 参考技术B 硬件么?硬件的话fpga的IO比较自由,只需按stm的IO进行分配就好,

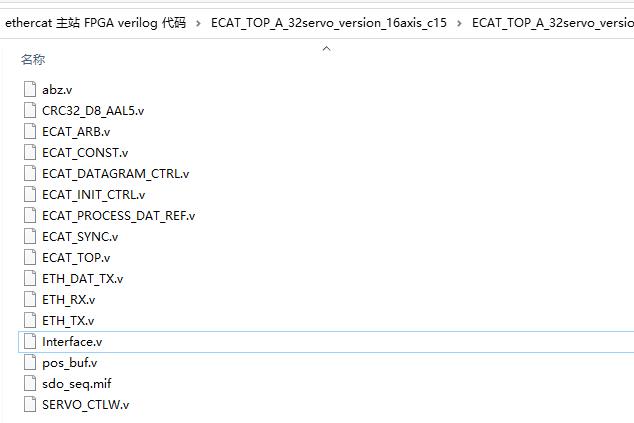

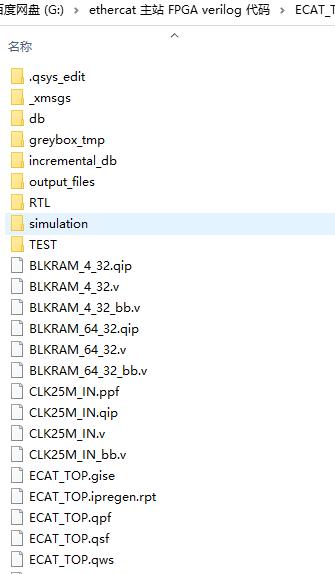

基于 FPGA verilog 的 Ethercat 主站工程代码

EtherCAT 总线 demo 板介绍

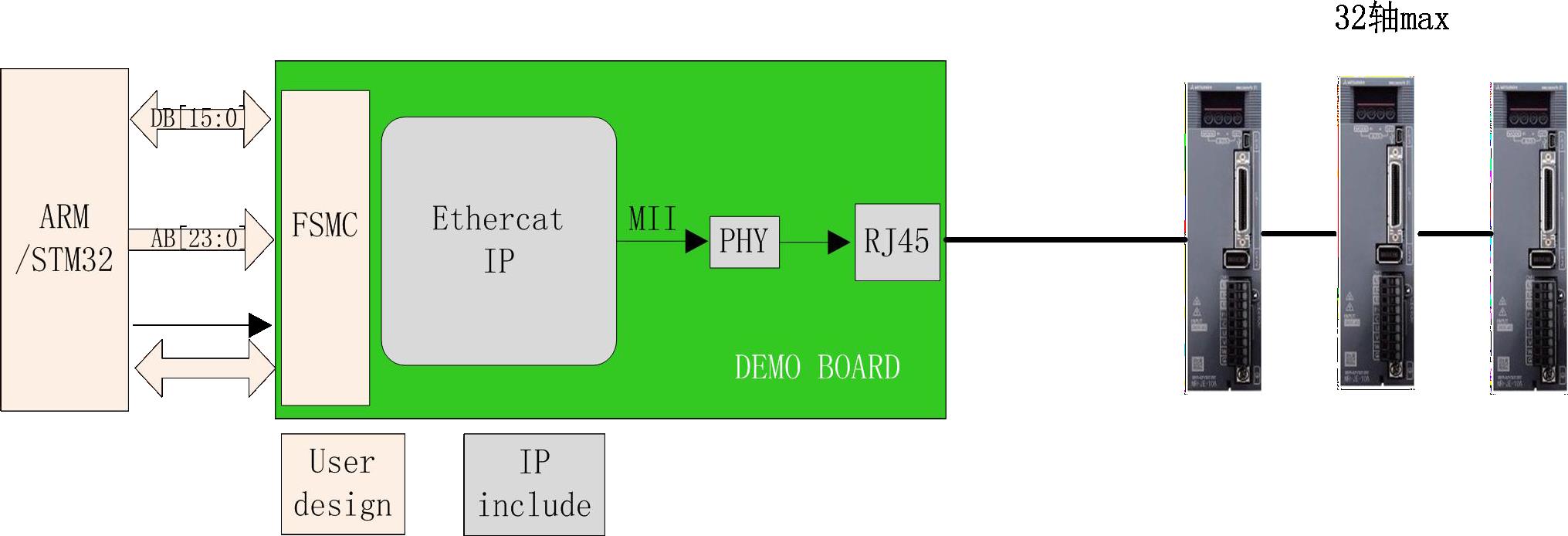

一、测试架构介绍

- 总线部分包括 EtherCAT 协议、Canopen 协议、1588 同步协议,全部在 FPGA上实现,纯 Verilog 实现,无软核,时间精准。

- FPGA 挂百兆网口串接伺服,布线简单。

- 支持驱动 1-32 轴,自动侦测。

- CPU 和FPGA 的接口,根据 CPU 的不同而不同,常用的如 FSMC 接口、GPMC 接口、PCI/PCIE 接口等等。

- 运动控制部分用户可以选择在 STM32、ARM、X86 等 CPU 上实现 (此部分代码 demo 板不包含)

- DEMO 板具备参数固定自动运行模式,可测试总线的通讯和驱动器侦测运行正常。

- 图中 User design 部分为用户自行设计。

- 图中 IP include 部分为 demo 或 IP 提供的。

二、具体性能参数

1、循环周期和抖动

- 循环周期支持 31.25us、62.5us、125us、250us、500us、1ms、2ms 等。

- 主站在循环周期 2ms 时抖动为 50us,循环周期越短,抖动越小,从站抖动10ns。

2、支持轴数与FPGA 资源消耗量

- 支持 1-32 轴,消耗资源 12K 逻辑 Slice 左右,如用户有自己的 IP 或功能模块需要集成,则建议采用 30K 资源的 FPGA,这样才有足够冗余以备所需。某些运动控制器需要添加手轮,IO 开关量,其他用户自定义功能。

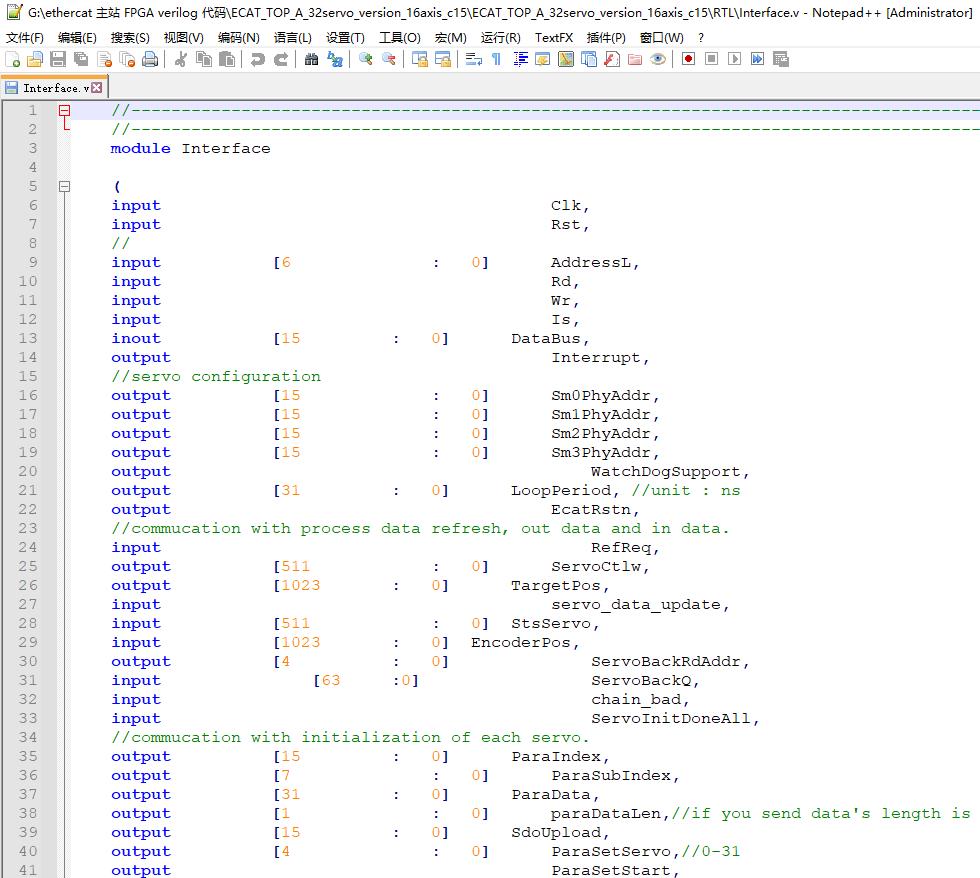

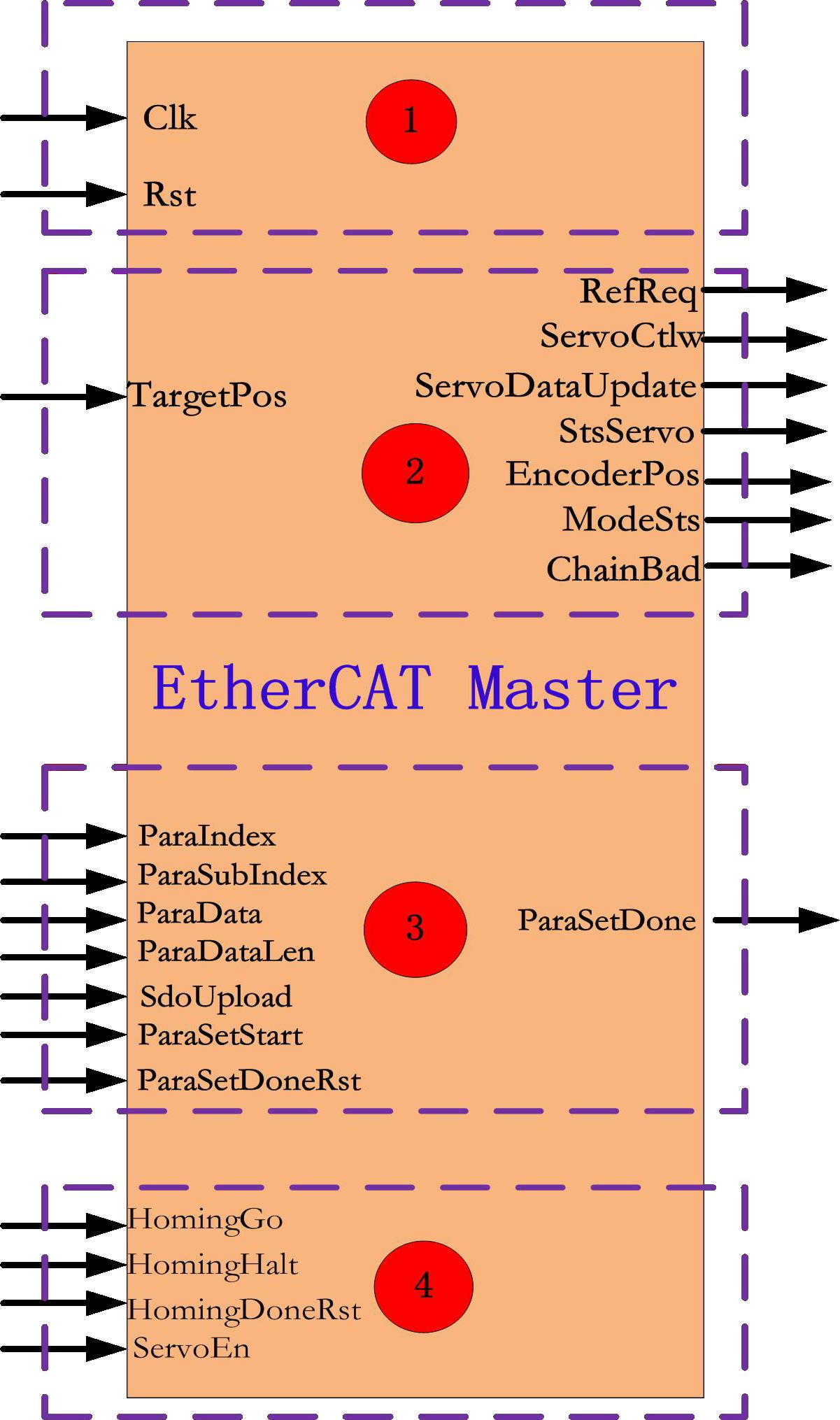

三、用户接口

该 DEMO 中接口分为 4 个部分:系统部分,过程数据部分,伺服参数配置部分,回零部分,具备与外部处理器交互的接口为过程数据部分,伺服参数配置部分,具体信号如下图所示。

| 标号 | 信号部分 | 功能 |

| 1 | 系统部分 | 时钟域复位信号,用于复位 Ethercat master 主

站 |

| 2 | 过程数据部分 | 用于处理器与驱动器之间的指令和状态交互,包

括位置,状态及其对应的有效信号 |

| 3 | 伺服参数配置部分 | 用于处理器配置主站参数,包括数据的地

址,数据的长度,数据以及设置启动和复位信号 |

| 4 | 测试接口 | 测试接口包括回零的启动和复位等信号,用户无

需使用 |

注:自测试模式为以上端口固定数字量自运行模式,驱动器将持续运转。

ECAT运动控制器ARM软件设计

一、ARM向FPGA发送目标位置

1、对应的操作地址

`define CUR_POS_SERVO 1

`define TARGET_CUR_POSL 2

`define TARGET_CUR_POSH 3

2、操作步骤

- 下发每个轴的位置时,先通过写地址1,告知FPGA接下来要发送目标位置的伺服;

- 再通过写地址2向FPGA写目标位置的低16bit;

- 再通过写地址3向FPGA写目标位置的高16bit。

3、注意

通过地址1,向FPGA写接下来要操作的伺服,写0表示第一个伺服,写31表示第32个伺服,以此类推。

在读写操作完成之前,不要改变指定的伺服。也就是说指定伺服+读写数据,是一整套。

二、ARM向FPGA读取当前位置

1、对应的操作地址,与目标位置共享一套地址

`define CUR_POS_SERVO 1

`define TARGET_CUR_POSL 2

`define TARGET_CUR_POSH 3

2、操作步骤

- 下发每个轴的位置时,先通过写地址1,告知FPGA接下来要读取当前位置的伺服;

- 再通过读地址“2”向FPGA读取当前位置的低16bit;

- 再通过读地址“3”向FPGA读取当前位置的高16bit。

三、ARM向FPGA发送控制字

1、对应的操作地址

`define CUR_POS_SERVO 1

`define STS_SERVO 4

2、操作步骤

- 下发每个轴的控制字时,先通过写地址1,告知FPGA接下来要发送控制字的伺服;

- 再通过写地址4向FPGA写伺服的控制字;FPGA会根据第一步的伺服去对应该控制字是给哪个伺服的。

当ARM通过地址58检测到所有伺服进入OP状态后,可以通过控制字来控制各个伺服进入伺服使能状态,具体的操作流程为:顺序发送控制字6、7、15。每发送一个控制字,伺服对应的状态字就会发生变化。通过检测状态字的变化来确定发送下一个控制字。

回零的控制字为15到31,回零完成后,控制字要返回15。

四、ARM向FPGA读取状态字

1、对应的操作地址

`define CUR_POS_SERVO 1

`define STS_SERVO 4

2、操作步骤

- 下发每个轴的控制字时,先通过写地址1,告知FPGA接下来要读取控制字的伺服;

- 再通过读地址4向FPGA读取对应伺服的控制字。

五、ARM读取轴的位置缓存数据的个数

1、对应的操作地址

`define CUR_POS_SERVO 1

`define ECAT_POS_FIFO_CNT 65

2、操作步骤

FPGA为每个轴的目标位置都对应设计了一个32深度的缓存,ARM根据缓存和需要将目标位置发送到这个缓存,供FPGA的ECAT刷新。

- 先通过写地址1,告知FPGA接下来要读取数据个数的伺服;

- 再通过读地址65来读取对应伺服的轴数据缓存中数据个数。

六、ARM在启动FPGA的ECAT之前需要配置的内容

1、配置FPGA内容的相关写地址

`define SM0_PHYADDR 49

`define SM1_PHYADDR 50

`define SM2_PHYADDR 51

`define SM3_PHYADDR 52

`define WATCHDOG_SUPPORT 53

`define LOOP_PERIOD_H 55

`define LOOP_PERIOD_L 56

2、具体含义

- SM0_PHYADDR,SM0的地址,16bit,xml文件中的高低8bit交换后,下发给FPGA。

- SM1_PHYADDR,SM1的地址,16bit,xml文件中的高低8bit交换后,下发给FPGA。

- SM2_PHYADDR,SM2的地址,16bit,xml文件中的高低8bit交换后,下发给FPGA。

- SM3_PHYADDR,SM3的地址,16bit,xml文件中的高低8bit交换后,下发给FPGA。

- WATCHDOG_SUPPORT,伺服是否支持看门狗,写1表示支持,写0表示不支持,从测试的5家伺服来看,除久同外,其他家均支持。

- LOOP_PERIOD_H ,为循环周期的高16bit。

- LOOP_PERIOD_L ,为循环周期的低16bit。

七、控制和状态寄存器

1、相关操作地址

`define ECAT_RSTN 57

`define SERVO_INIT_DONE_ALL 58

2、具体含义

- ECAT_RSTN ,ARM向该地址写1,启动FPGA的ECAT运行。

- SERVO_INIT_DONE_ALL,ARM通过该地址读取所有伺服是否初始化完毕,1表示完毕。

八、伺服参数配置功能寄存器

1、相关操作地址

`define PARA_INDEX 77

`define PARA_SUB_INDEX 78

`define PARA_DATA_H 79

`define PARA_DATA_L 80

`define PARA_DATA_LEN 81

`define PARA_DATA_UpLOAD 82

`define PARA_DATA_UpLOAD_H 83

`define PARA_DATA_UpLOAD_L 84

`define PARAM_SET 85

`define PARAM_SET_RST 86

`define PARAM_SET_SERVO 87

九、伺服回零功能

多个伺服同时回零的流程:

通过参数设置端口,依次将各个伺服设置成模式6,再依次发送控制字31,再依次去读取状态字,如果读到某个轴的状态字是回零完成,就将该轴的控制字写回15,并然后通过参数设置接口将其模式设置为8。

十、伺服IO读取与写入

在启动ECAT之前,通过如下两个地址,分别配置伺服IO的地址:

`define M2S_IO_PHYADDR 47 //master output

`define S2M_IO_PHYADDR 48 //master input

地址47为运动控制器输出到伺服的IO指令;

地址48为运动控制器从伺服获取的IO状态。

启动ECAT后,通过地址99来输出IO指令到伺服,或者从伺服获取IO状态。

`define SERVO_IO 99

同理,通过地址4来指定所要操作的伺服。

初定为8输入8输出,16位数据线的低8bit有效。

十一、其他标志

轴数据缓存的空满标志、ECAT断线等等标志

以上是关于STM32F407加FPGA用FSMC总线怎么连接的主要内容,如果未能解决你的问题,请参考以下文章