X-005 FriendlyARM tiny4412 uboot移植之时钟初始化

Posted LoTGu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了X-005 FriendlyARM tiny4412 uboot移植之时钟初始化相关的知识,希望对你有一定的参考价值。

<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<

开发环境:win7 64位 + VMware12 + Ubuntu14.04 64位

工具链:linaro提供的gcc-linaro-6.1.1-2016.08-x86_64_arm-linux-gnueabi

要移植的u-boot版本:u-boot-2016-11

Tiny4412开发板硬件版本为:

底板: Tiny4412/Super4412SDK 1506

核心板:Tiny4412 - 1412

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

在上一节中我们可以通过点亮tiny4412核心板上的LED灯开始调试u-boot。接下来要做的是初始化exynos4412的时钟。

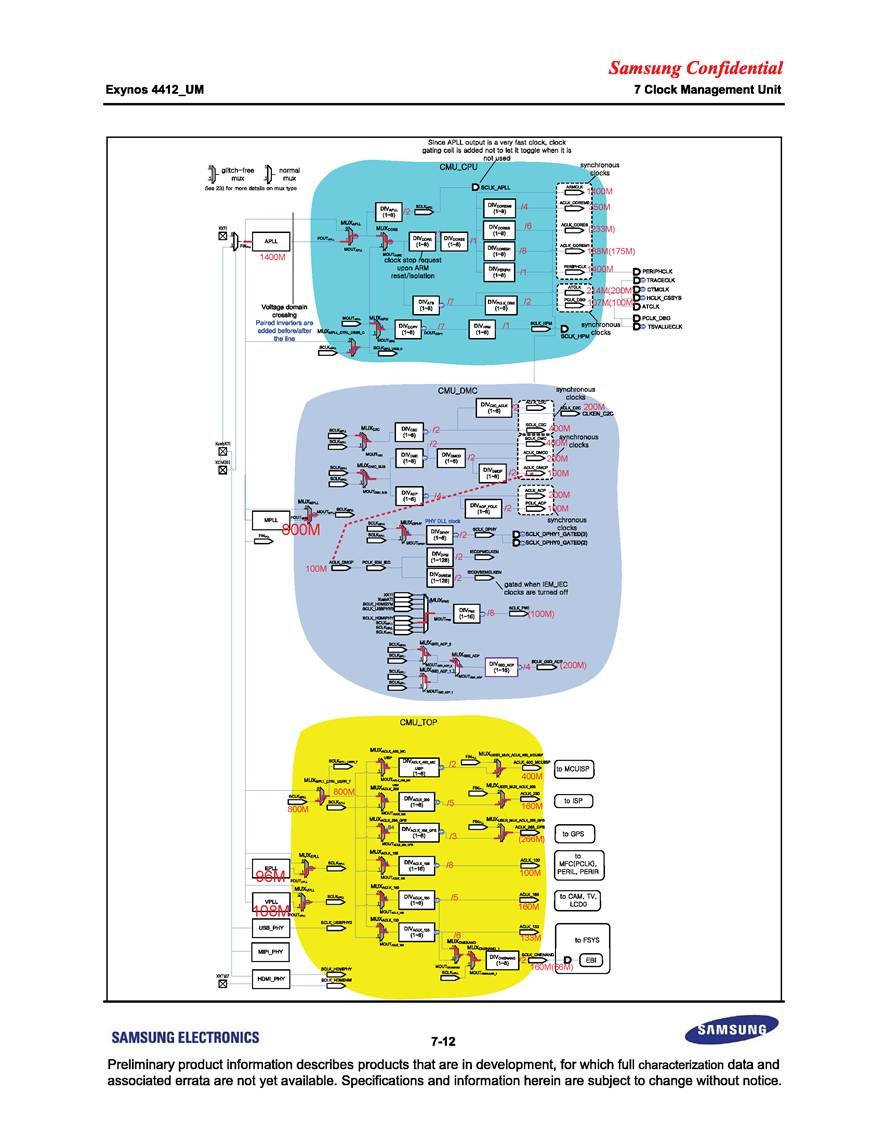

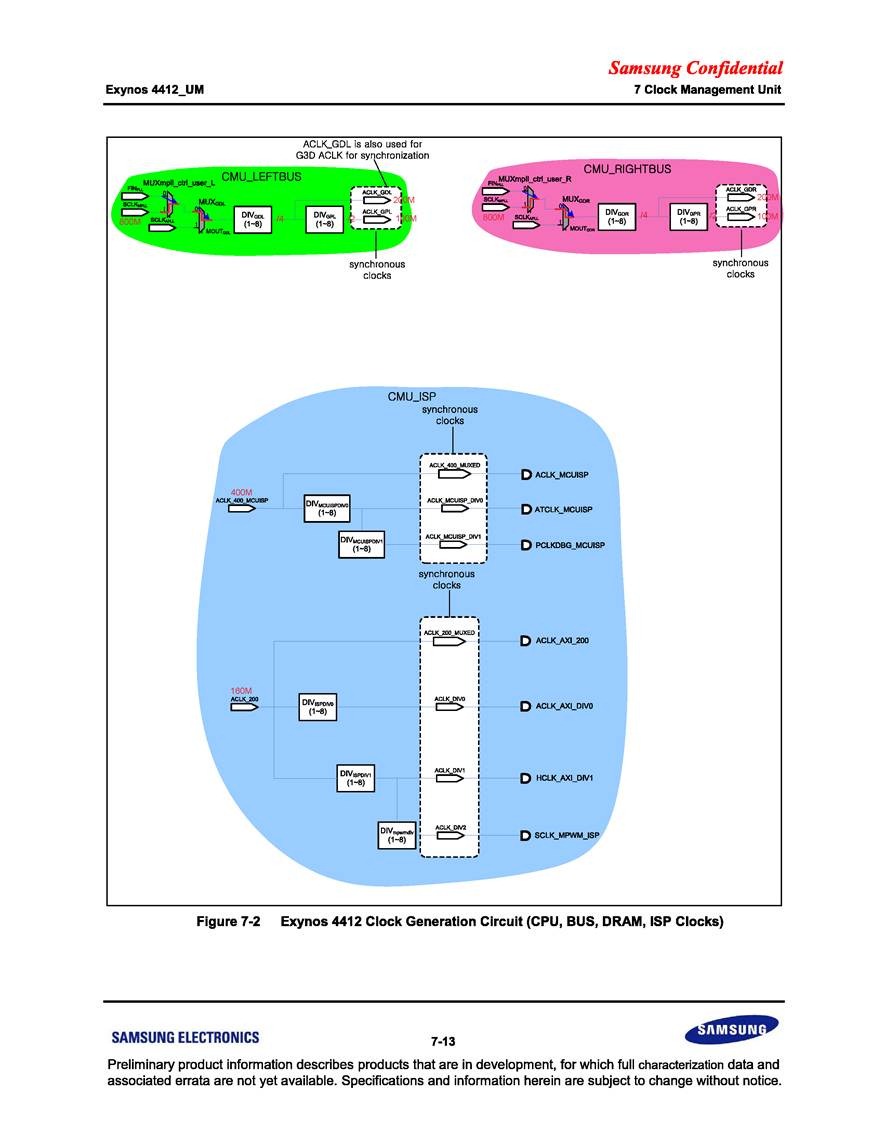

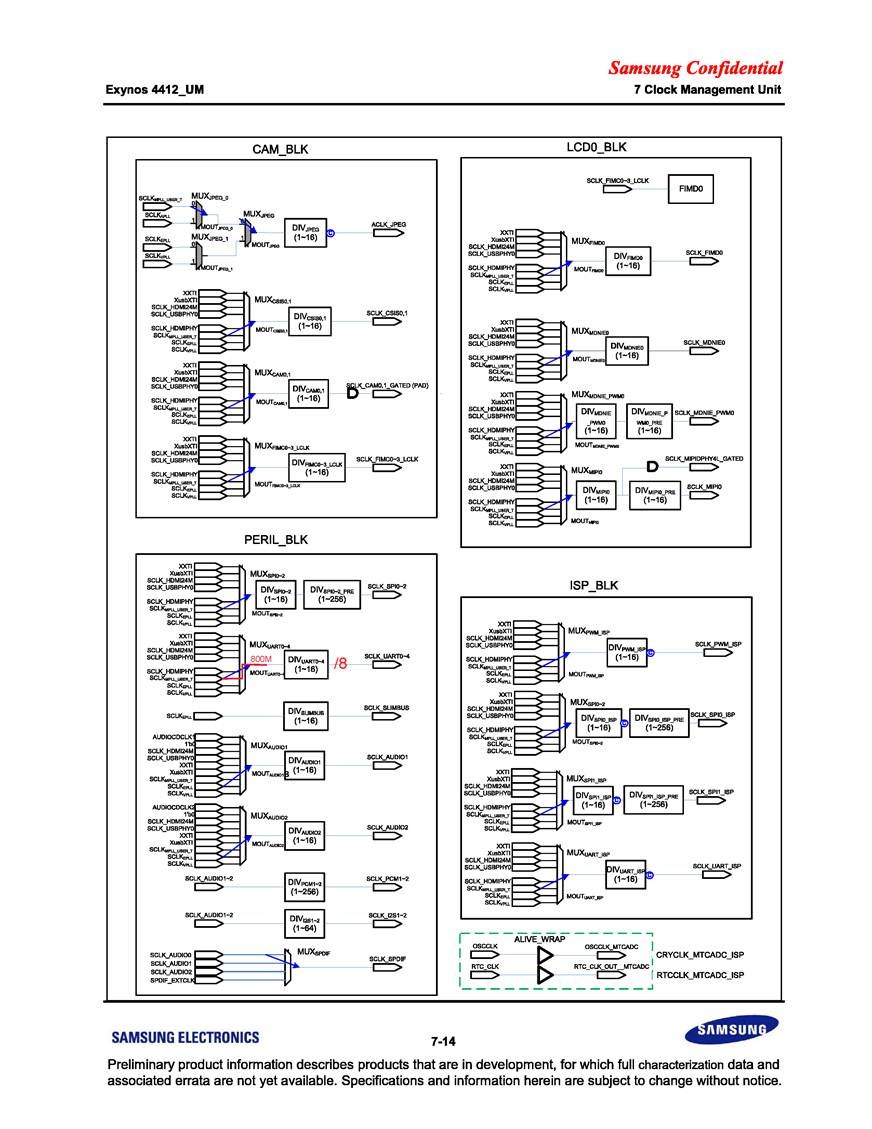

1、Exynos4412的时钟体系

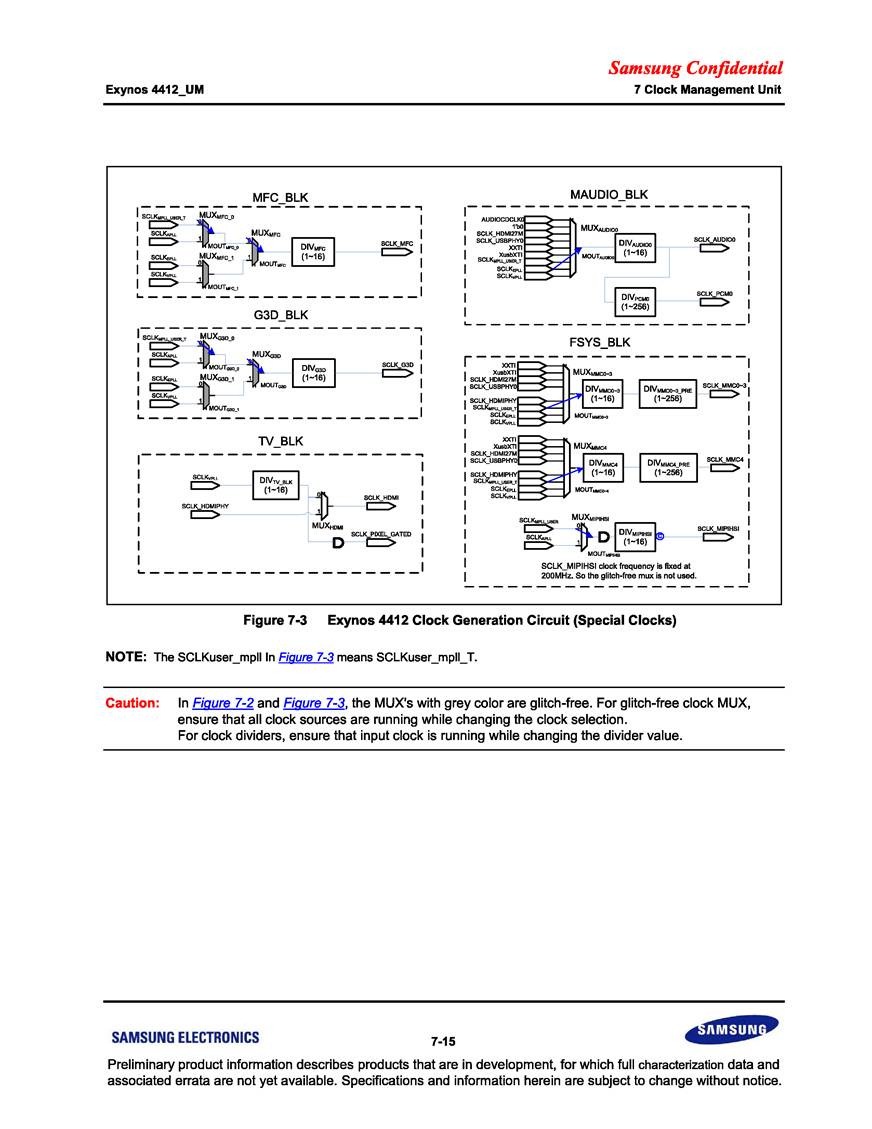

exynos4412芯片时钟体系的介绍在《Exynos 4412 SCP_Users Manual_Ver.0.10.00_Preliminary.pdf》的第七章节。

Exynos4412有3个初始时钟源:

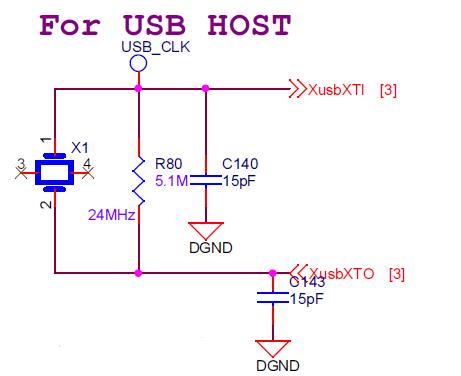

① XRTCXTI引脚 :接 32KHz的晶振,用于实时钟 (RTC) 。

② XXTI引脚 :接12M ~50 MHz的晶振, 用于向系统提供时钟,也可以不接。

③ XUSBXTI引脚 :接24MHz的晶振 ,用于向系统提供时钟。

在友善之臂tiny4412的开发板中, XRTCXTI 上没有外接晶振,系统时钟来源是XUSBXTI引脚上接的24MH 晶振,如下图所示:

2、Exynos4412的时钟设置

相关的设置结果如下:

3、Exynos4412的时钟设置代码

| diff --git a/arch/arm/mach-exynos/Makefile b/arch/arm/mach-exynos/Makefile index ac47ab2..f2cd76d 100644 --- a/arch/arm/mach-exynos/Makefile +++ b/arch/arm/mach-exynos/Makefile @@ -15,7 +15,7 @@ ifdef CONFIG_SPL_BUILD obj-$(CONFIG_EXYNOS5) += clock_init_exynos5.o obj-$(CONFIG_EXYNOS5) += dmc_common.o dmc_init_ddr3.o obj-$(CONFIG_EXYNOS4210)+= dmc_init_exynos4.o clock_init_exynos4.o -obj-$(CONFIG_EXYNOS4412)+= dmc_init_exynos4.o clock_init_exynos4.o +obj-$(CONFIG_EXYNOS4412)+= dmc_init_exynos4412.o clock_init_exynos4412.o obj-y += spl_boot.o tzpc.o obj-y += lowlevel_init.o endif diff --git a/arch/arm/mach-exynos/clock_init_exynos4412.c b/arch/arm/mach-exynos/clock_init_exynos4412.c new file mode 100644 index 0000000..cd70185 --- /dev/null +++ b/arch/arm/mach-exynos/clock_init_exynos4412.c @@ -0,0 +1,554 @@ +/* + * Clock Initialization for board based on EXYNOS4412 + * + * 2016 + * Modified by AP0904225 <ap0904225@qq.com> + * + * Copyright (C) 2013 Samsung Electronics + * Rajeshwari Shinde <rajeshwari.s@samsung.com> + * + * See file CREDITS for list of people who contributed to this + * project. + * + * This program is free software; you can redistribute it and/or + * modify it under the terms of the GNU General Public License as + * published by the Free Software Foundation; either version 2 of + * the License, or (at your option) any later version. + * + * This program is distributed in the hope that it will be useful, + * but WITHOUT ANY WARRANTY; without even the implied warranty of + * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the + * GNU General Public License for more details. + * + * You should have received a copy of the GNU General Public License + * along with this program; if not, write to the Free Software + * Foundation, Inc., 59 Temple Place, Suite 330, Boston, + * MA 02111-1307 USA + */ + +#include <common.h> +#include <config.h> +#include <asm/io.h> +#include <asm/arch/cpu.h> +#include <asm/arch/clk.h> +#include <asm/arch/clock.h> +#include "common_setup.h" + +#include "exynos4412_setup.h" + +/* + * system_clock_init: Initialize core clock and bus clock. + * void system_clock_init(void) + */ +void system_clock_init(void) +{ + unsigned int set, clr, clr_src_cpu, clr_pll_con0, clr_src_dmc; + struct exynos4x12_clock *clk =(struct exynos4x12_clock *) + samsung_get_base_clock(); + + /* + * APLL= 1400 MHz + * MPLL=800 MHz + * EPLL=96 MHz + * VPLL=108 MHz + * freq (ARMCLK) = 1400 MHz at 1.3 V + * freq (ACLK_COREM0) = 350 MHz at 1.3V + * freq (ACLK_COREM1) = 188 MHz at 1.3 V + * freq (PERIPHCLK) = 1400 MHz at 1.3 V + * freq (ATCLK) = 214 MHz at 1.3 V + * freq (PCLK_DBG) = 107 MHz at 1.3 V + * freq (SCLK_DMC) = 400 MHz at 1.0 V + * freq (ACLK_DMCD) = 200 MHz at 1.0 V + * freq (ACLK_DMCP) = 100 MHz at 1.0 V + * freq (ACLK_ACP) = 200 MHz at 1.0 V + * freq (PCLK_ACP) = 100 MHz at 1.0 V + * freq (SCLK_C2C) = 400 MHz at 1.0 V + * freq (ACLK_C2C) = 200 MHz at 1.0 V + * freq (ACLK_GDL) = 200 MHz at 1.0 V + * freq (ACLK_GPL) = 100 MHz at 1.0 V + * freq (ACLK_GDR) = 200 MHz at 1.0 V + * freq (ACLK_GPR) = 100 MHz at 1.0 V + * freq (ACLK_400_MCUISP) = 400 MHz at 1.0 V + * freq (ACLK_200) = 160 MHz at 1.0 V + * freq (ACLK_100) = 100 MHz at 1.0 V + * freq (ACLK_160) = 160 MHz at 1.0 V + * freq (ACLK_133) = 133 MHz at 1.0 V + * freq (SCLK_ONENAND) = 160 MHz at 1.0 V + */ + + /* + *before set system clocks,we switch system clocks src to FINpll + */

|