hcs12 microcontroller 笔记

Posted This is bill

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了hcs12 microcontroller 笔记相关的知识,希望对你有一定的参考价值。

文章来由

来到美国后,选了微处理器课,有幸老教授是 MIT 贝尔实验室出来的,希望好好学习这门课。

零、Chapter 0 绪论

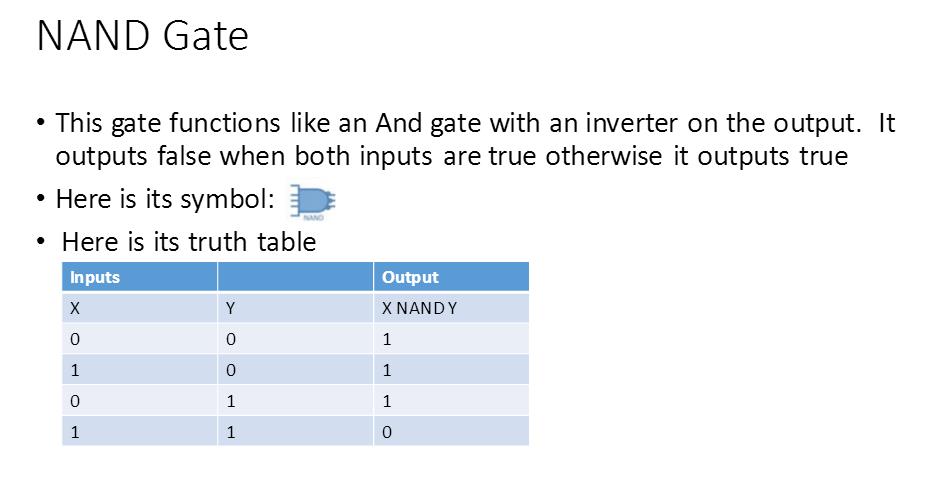

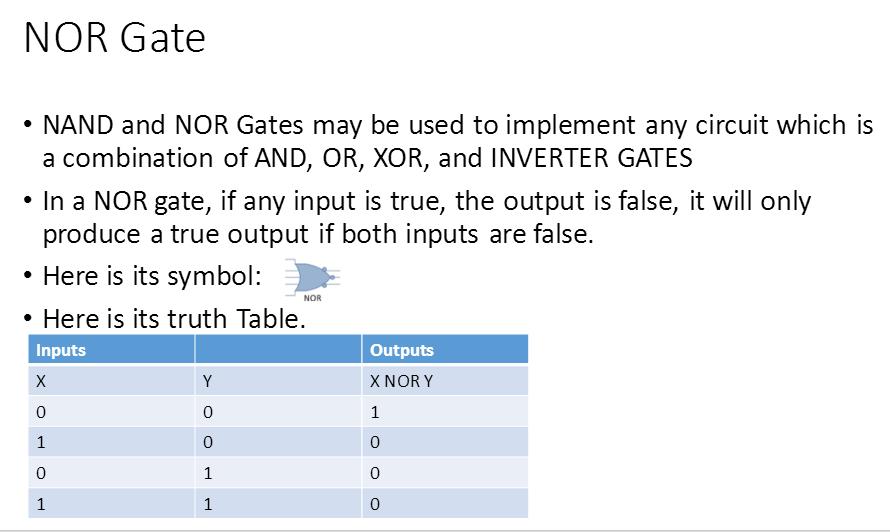

0-2 Logic Gates

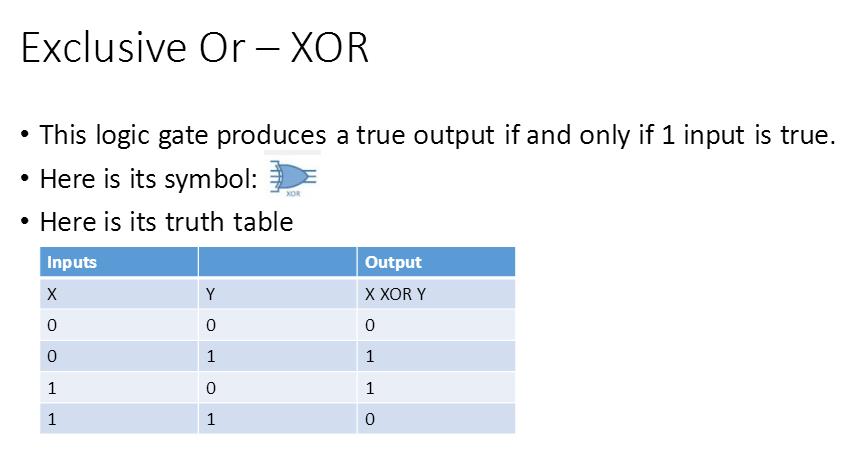

1、基础逻辑门(注意记住符号)

2、三态缓冲器

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

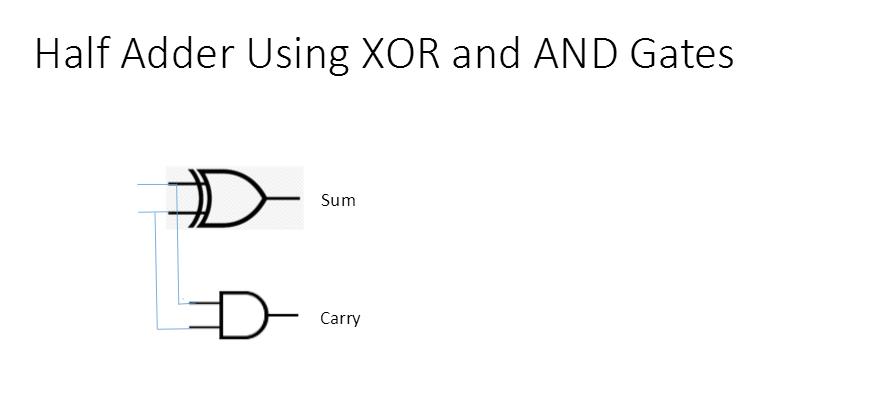

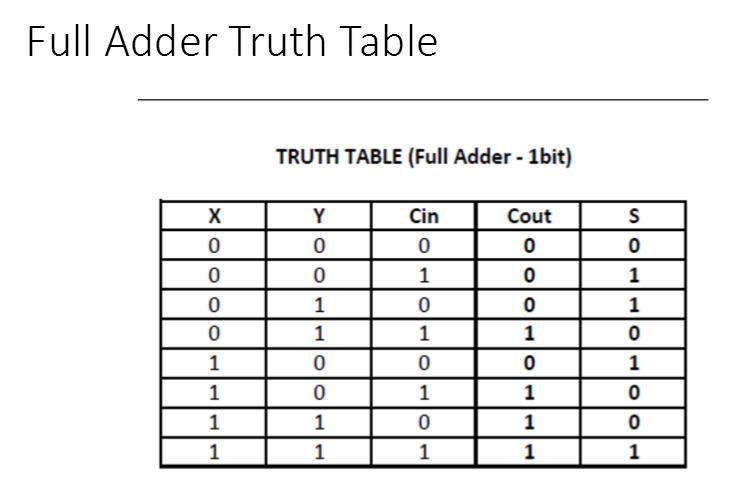

3、Logic Design using Gates 为什么可以用 and 做 carry

•Note that there are 4 possible outcomes when adding a pair of binary numbers

•0 + 0 = carry 0, sum 0

•0 + 1 = carry 0, sum 1

•1 + 0 = carry 0, sum 1

•1 + 1 = carry 1, sum 0

•Recall that the AND gate only outputs 1 if both inputs are true, thus it could be used to output the carry bit.

•Recall that the XOR gate only outputs 1 if and only if one of the inputs are true.

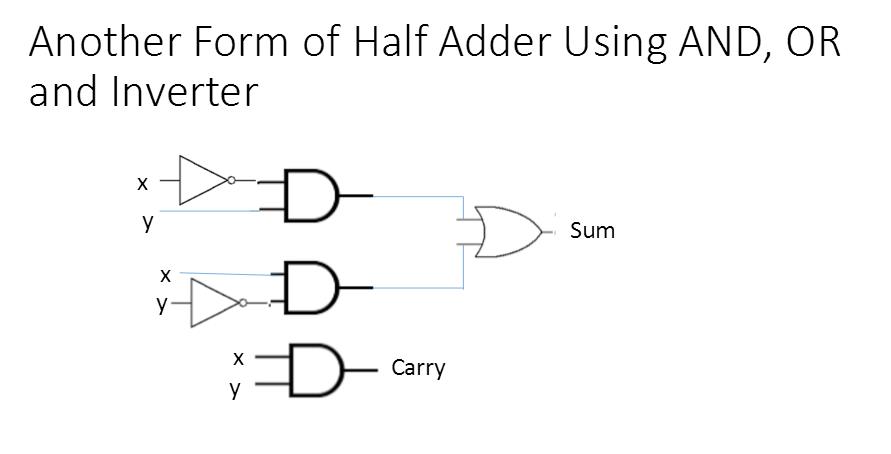

4、半加器

另一种形式

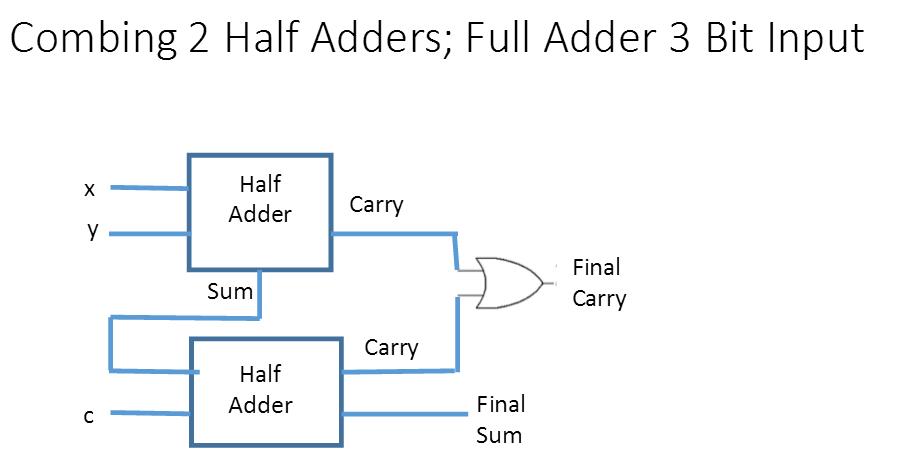

5、全加器

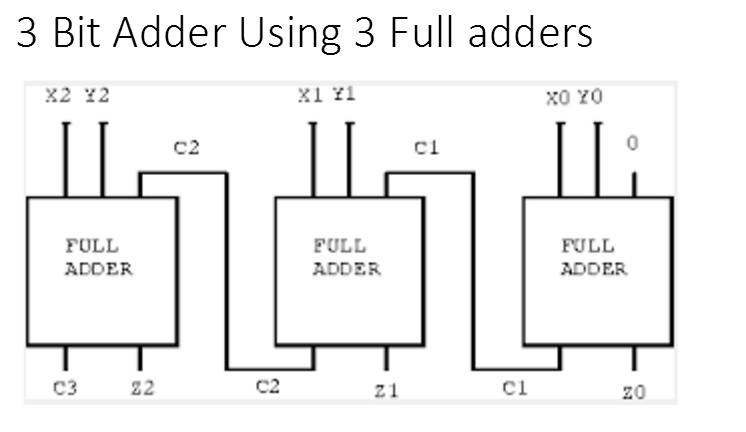

6、三位全加器

Application of the previous 3 Bit Adder

•Assume we want to add the binary numbers 010 and 011..

•Using the truth table shows before..

•We know that 0+1 with no carry in will result in Sum of 1 with no carry

•Also, 1+1 with no carry in will result in sum of 0 with carry out of 1 •Finally, 0+0 with carry in will result in sum of 1 with no carry

•Result is 0101

•The take away here is that we can cascade as many full adders as we want to add as large of a pair of binary numbers as we want.

•For example a 64 bit sum would require 64 cascaded adders

0-3 Semiconductor Memory(ROM、RAM类型)

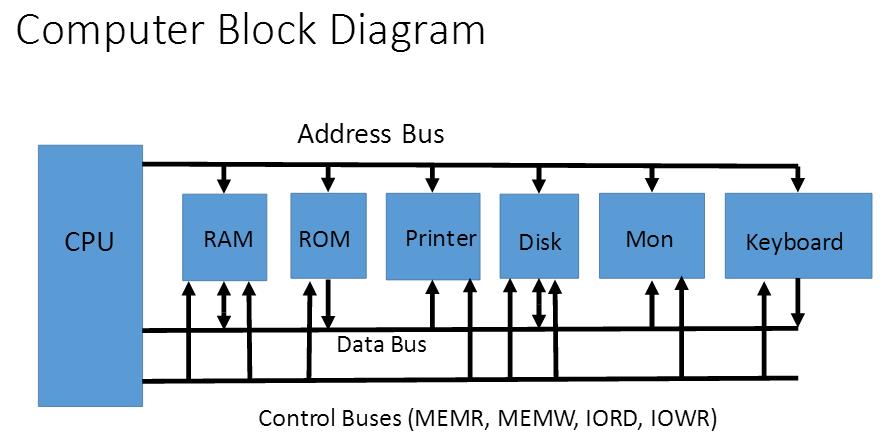

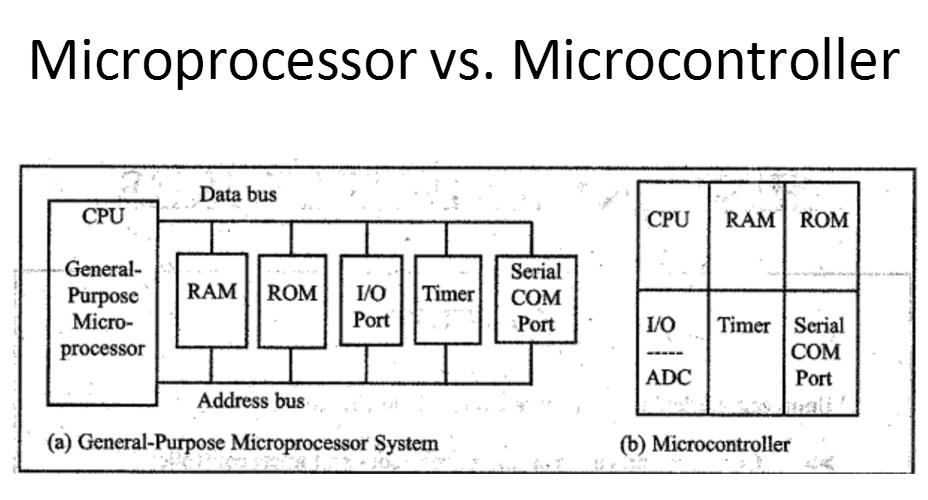

1、Internal Organization of computers

•3 major subsystems

•CPU – Central Processing Unit •Memory •I/O Input Output

•Connected by buses

•Data •Address •Control

More About the Data Bus

•Analogous to Highway

•The more lanes, the more simultaneous traffic

•The more data buses the better

•This adds to expense

•Note that we currently have 64 bit CPUs and operating systems

•The size of the data bus is related to both size and precisions of arithmetic operations

More About the Address Bus

•Every addressable device must have a unique address

•The larger the address bus, the larger number of devices which may be addressed by the CPU

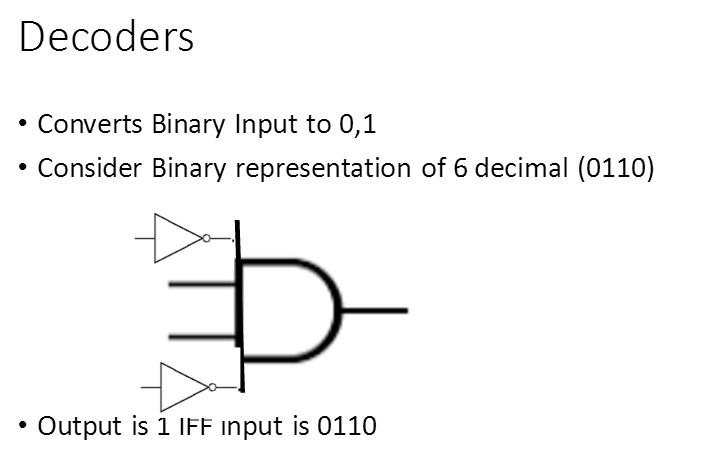

•Recall that decoders are used on addressable device to establish their address.

•The number of devices which may be addressed is always equal to 2^x where x is the number of address lines.

•For example, a 16 bit address bus can access 64k of addressable memory

•This is a unidirectional bus (send only from CPU)

2、Relation of CPU to RAM and ROM

3、Memory Capacity

•This is the number of bits a memory chip can store

•Chip capacity has units of bits, Computer system capacity has units of bytes

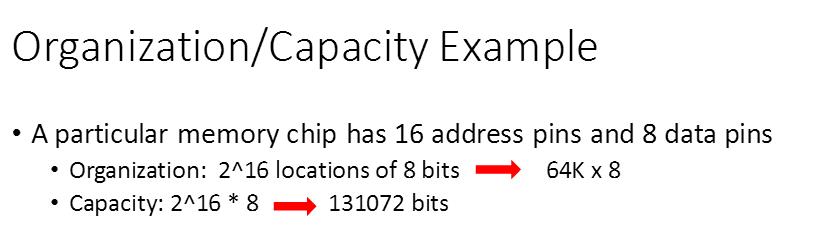

4、Memory Organization

•Memory chips are organized into a number of locations within the IC

•Each location can hold 1, 4, 8, 16, or more bits

•The number of bits that each location will hold is equal to the number of data

pins on the chip.

•The number of locations on the chip is determined by the number of address pins on the chip say x. 2^x is the number of locations (addresses) on the chip

•Total number of bits which may be stored on the entire chip is given by 2^(address pins) times the number of data pins

Another Organization/Capacity Example

•We have a chip with 256k capacity with 8 data pins.

•The organization is 256k/8 = 32K x 8 •The number of address lines is 15 since 2^15 = 32K

5、不同ROM类型

Different types such as:

•PROM

•EPROM

•EEPROM

•FLASH EPROM

•MASK PROM

(1)PROM (programmable ROM) and OTP

(2)EPROM (erasable programmable ROM) and UV-EPROM

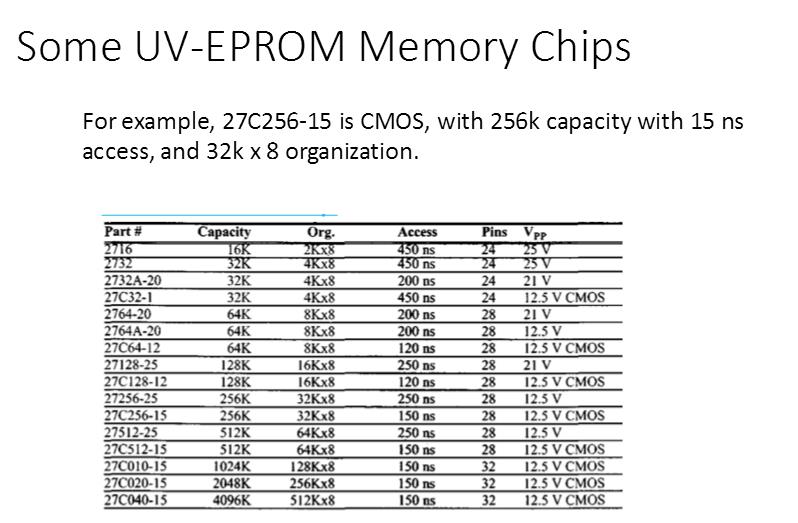

(3)Some UV-EPROM Memory Chips obsolete 已过时

(4)EEPROM (electrically erasable programmable ROM)

(5)Flash Memory EPROM

(6)Mask ROM

6、不同RAM类型

3 types

•Static RAM

•Nonvolatile RAM

•Dynamic Ram

(1)SRAM (static RAM)

(2)NV-RAM (nonvolatile RAM)

(3)DRAM (dynamic RAM)

7、Memory Block Selection

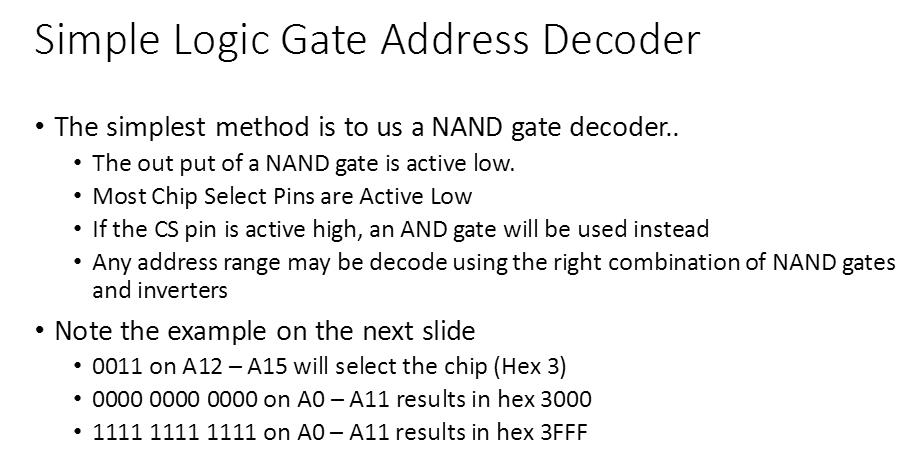

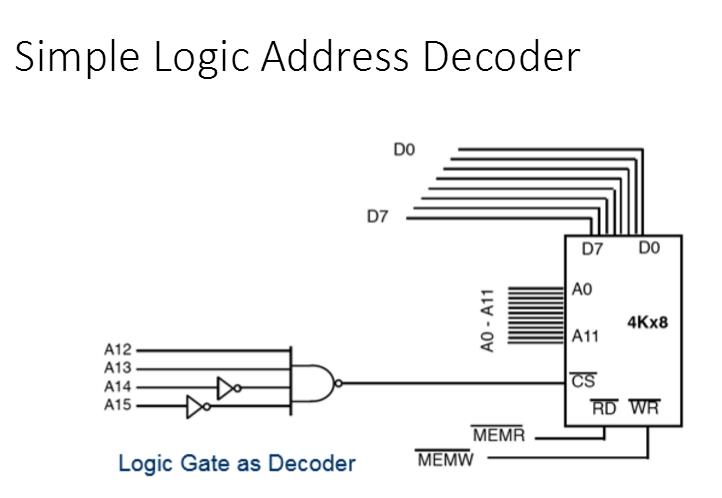

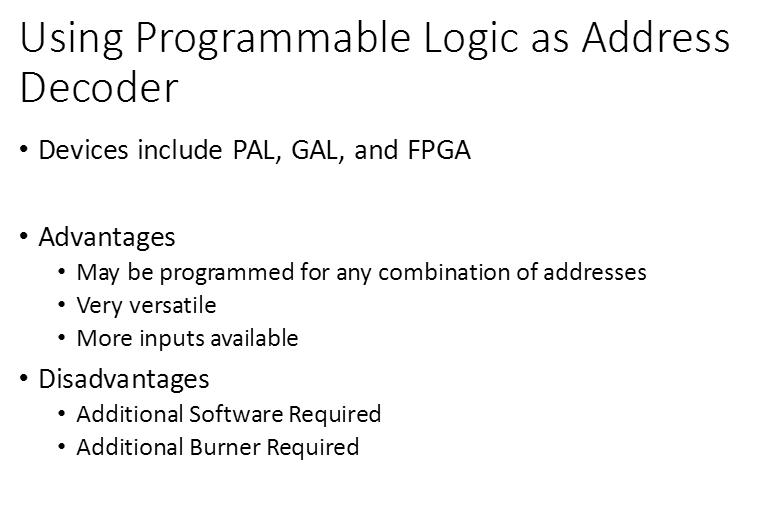

•Simple Logic Gates

•Using 74LS138

•Programmable Logic such as CPLD or FPGA

详见:http://blog.csdn.net/scythe666/article/details/52428243

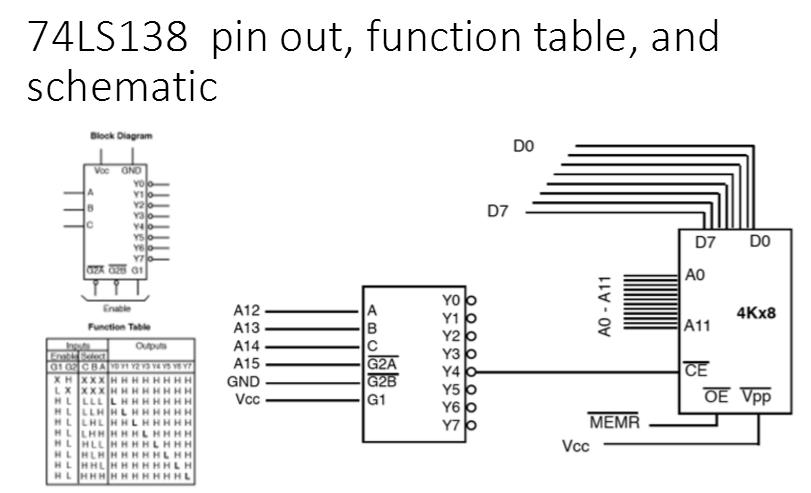

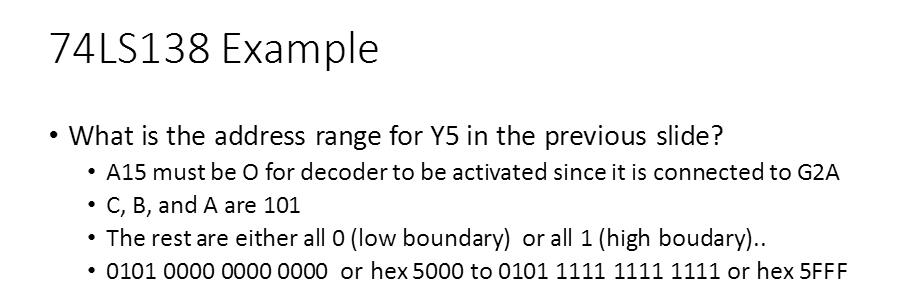

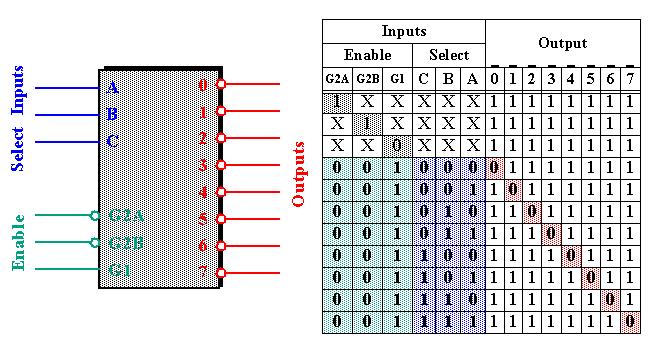

Using the 74LS138 3 – 8 decoder

•One of the most widely used decoders •3 inputs A, B, and C generate 8 active low outputs Y0 to Y7, •Each output is connected to CS of a different memory device allowing

control of 8 memory blocks

•Three additional inputs G1, G2A, and G2B may connected to an Address or Control Signal

•G2A and G2B active low •G1 active high •These inputs must be terminated in way or another •These inputs enable the device

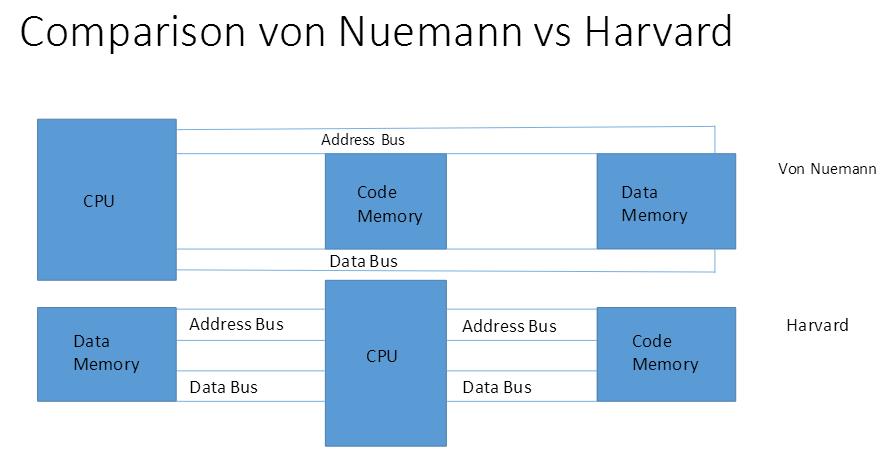

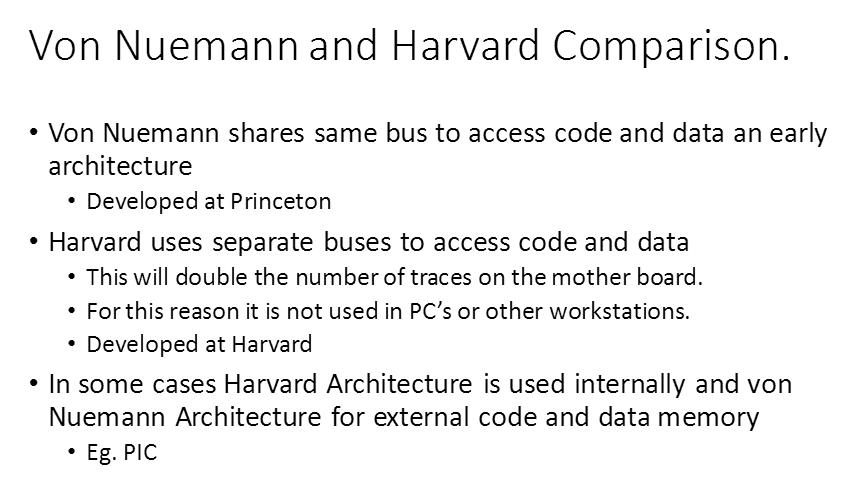

0-4 Harvard and von Neumann CPU Architectures

一、Chapter 1 微处理器简史

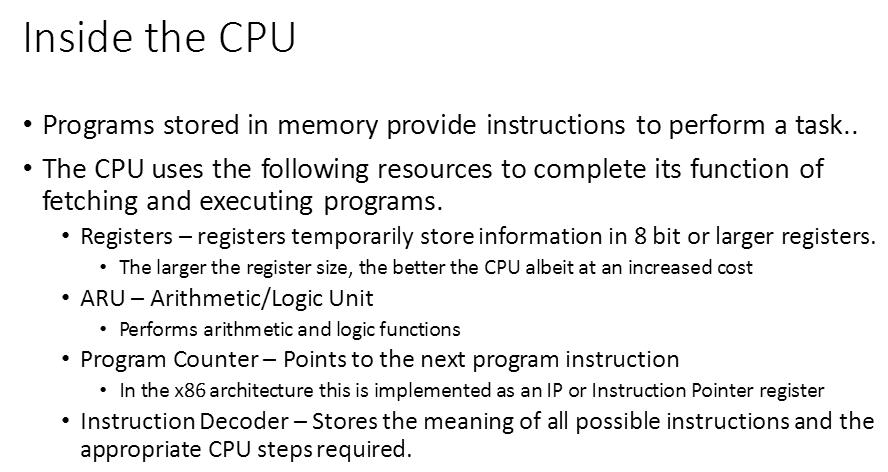

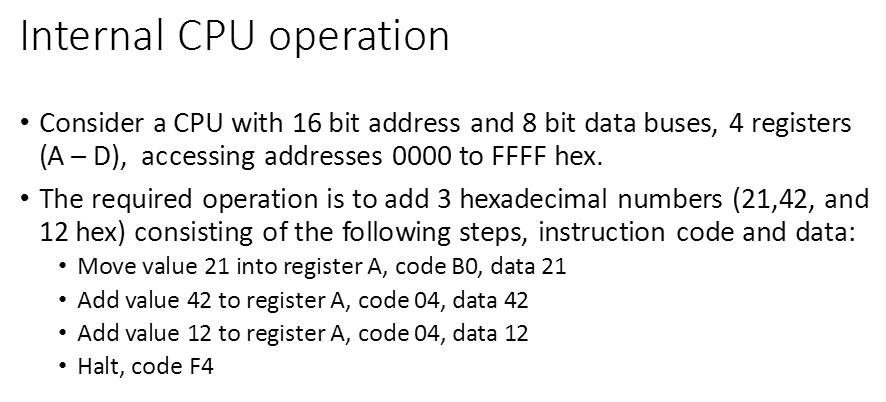

二、Chapter 2 内存 寄存器 简单指令

2-1 Registers of HCS12

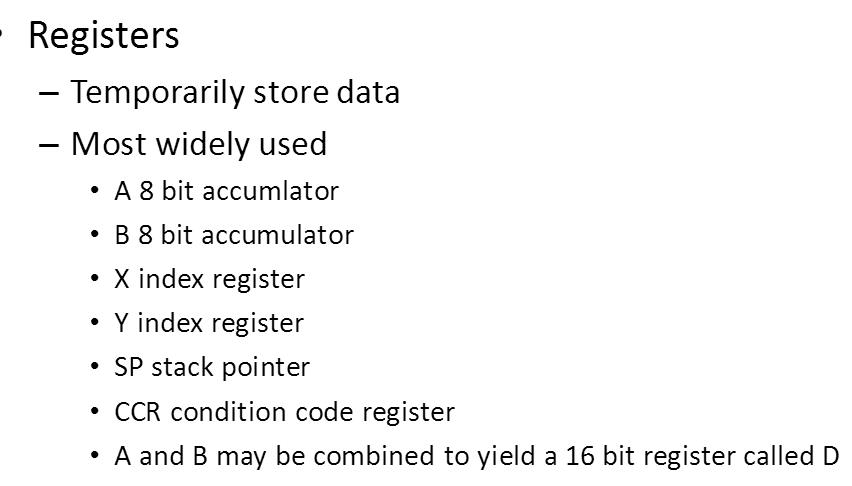

1、Registers overview

LDAA #$35 ; loads 55 hex into Accumulator A

•# signifies an immediate value

•$ signifies that the immediate value is base 16Absence of the # sign indicates that the value should be loaded from a memory location

•Eg LDAA $17 will load the contents of memory location 17 hex

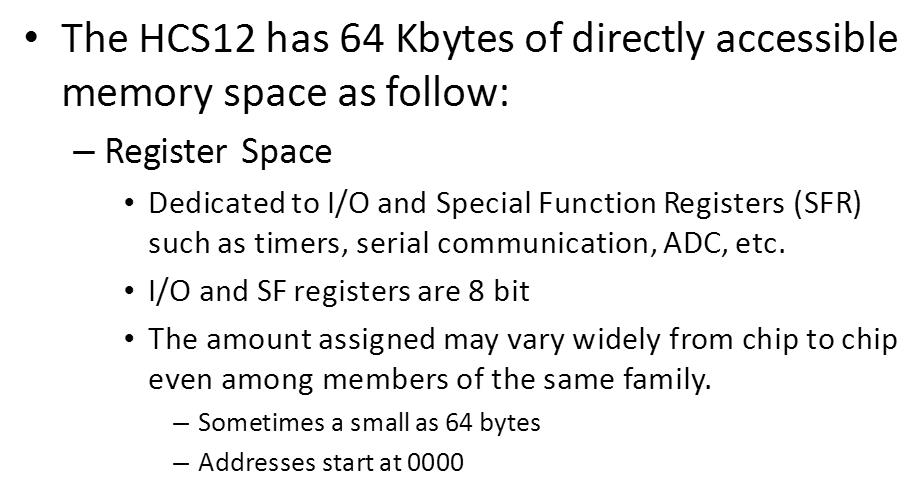

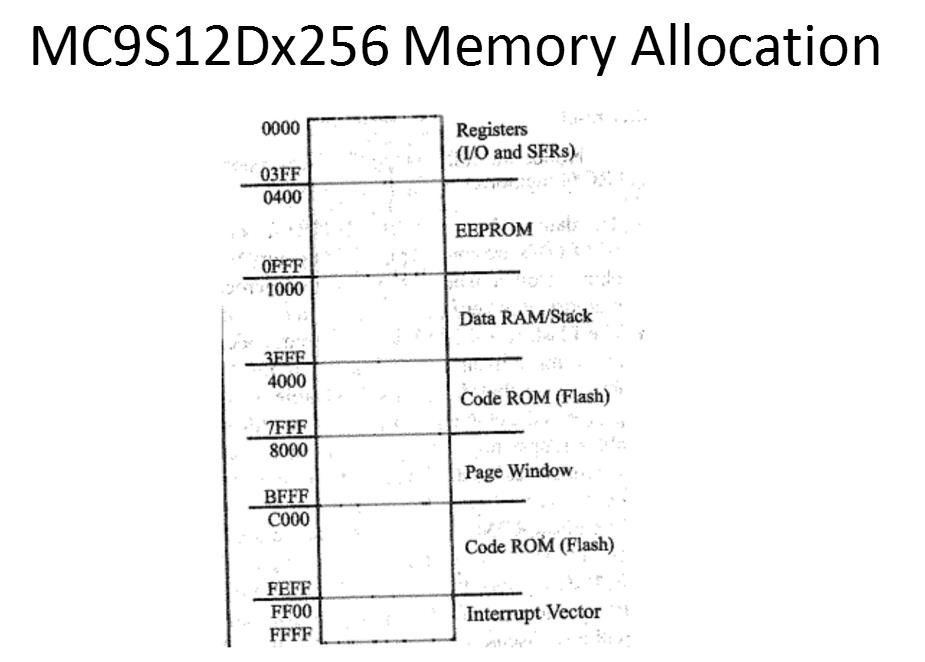

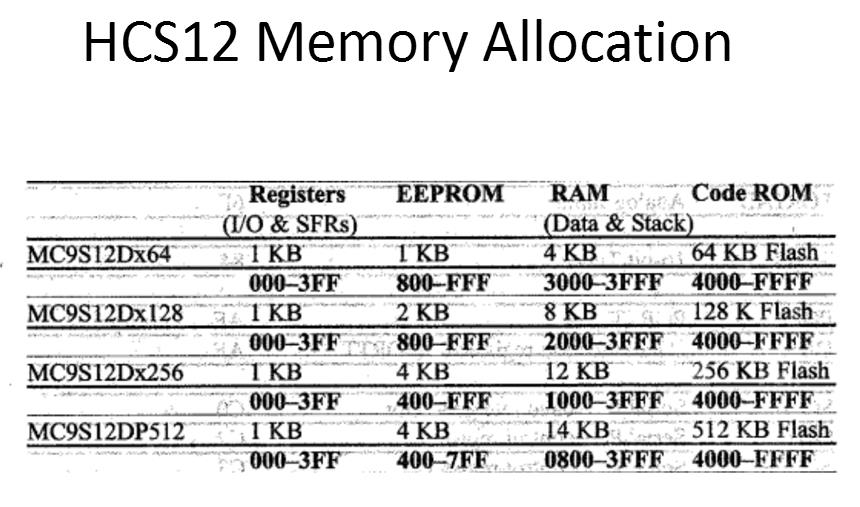

2-2 The HCS12 Memory Map

1、Memory Space Allocation in the HCS12

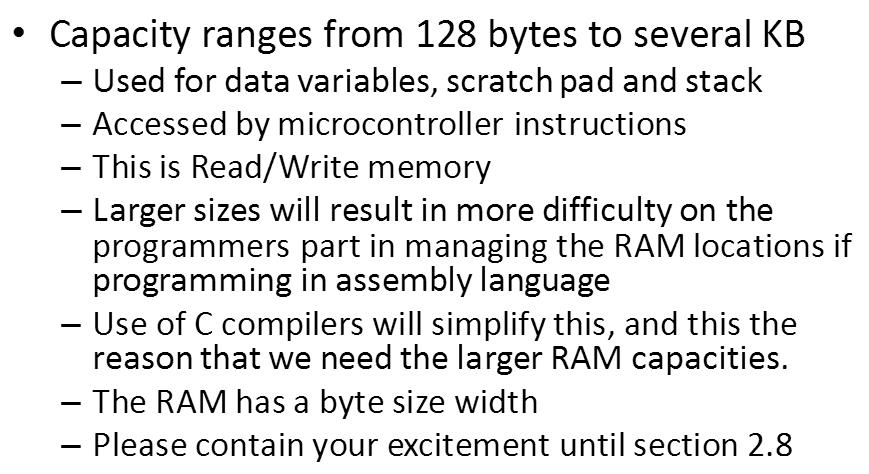

2、Data RAM Space

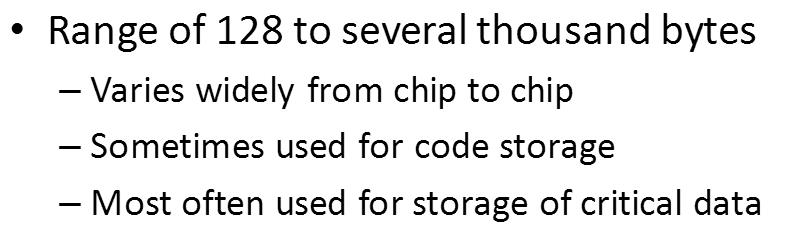

3、EEPROM Space

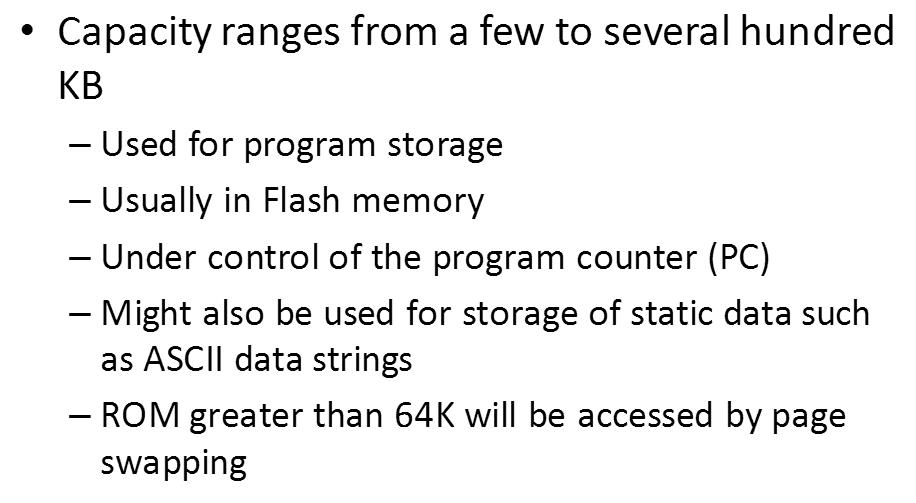

4、Code ROM Space

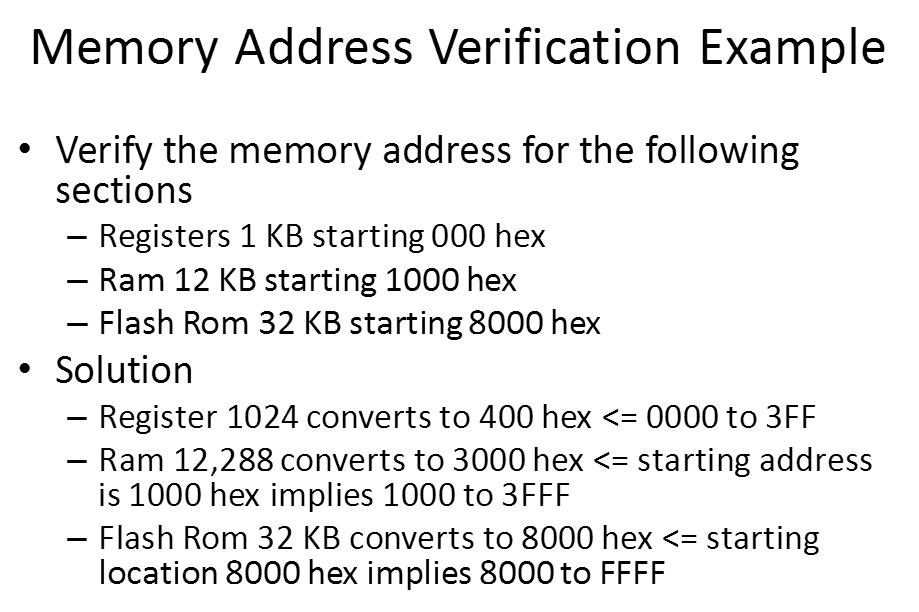

5、Memory Address Verification Example

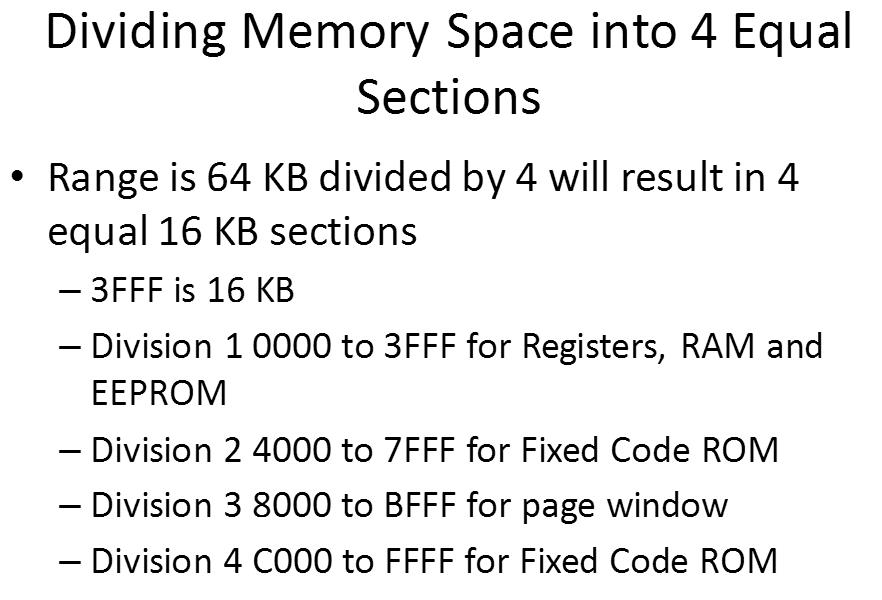

6、Dividing Memory Space into 4 Equal Sections

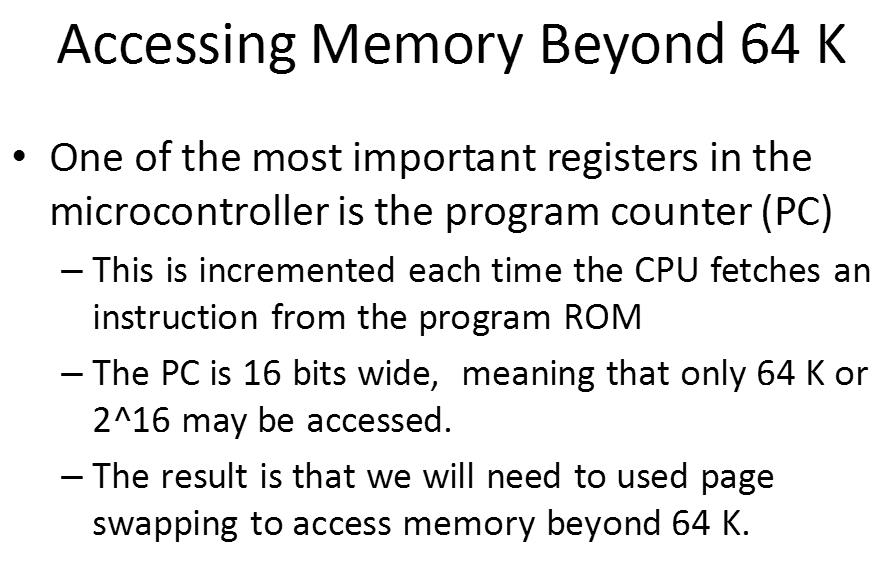

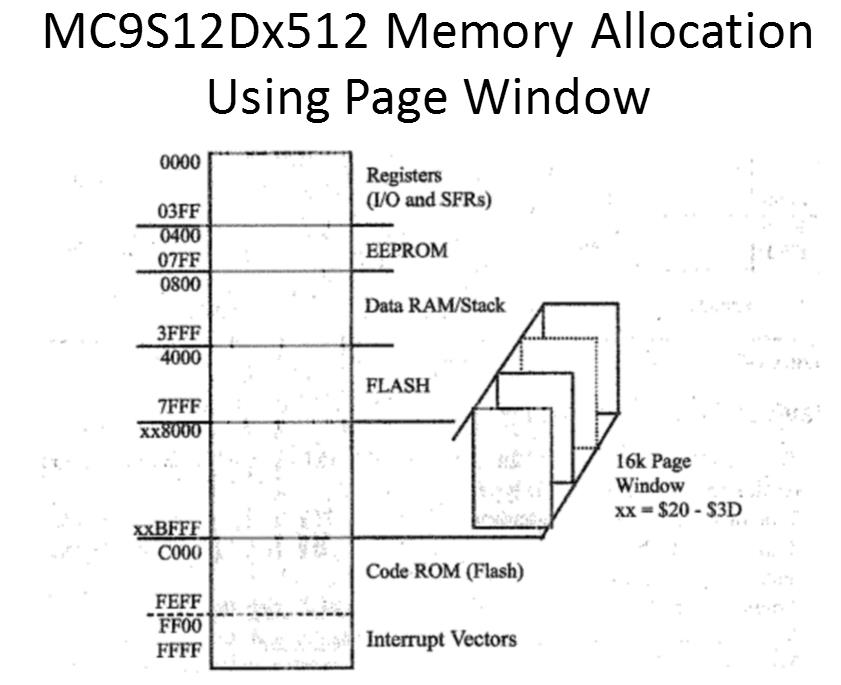

7、Accessing Memory Beyond 64 K

8、Where the HCS12 Wakes up when it is Powered up

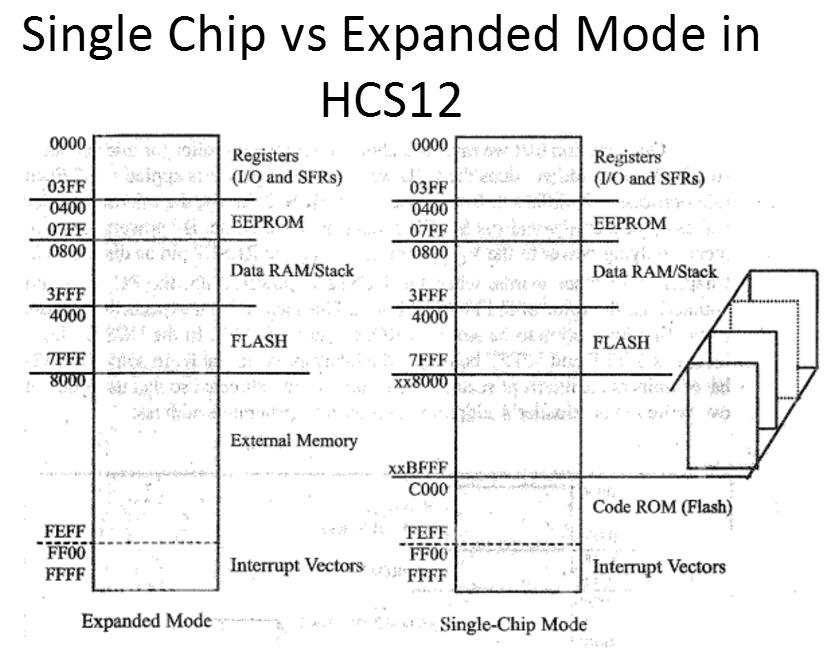

9、Single Chip and Expanded Modes in the HCS12

2-3 HCS12 Addressing Modes

•HCS12 has 6 distinct addressing modes

–Inherent 无操作数

–Immediate 立即数

–Extended 直接访问内存地址

–Direct 直接寻址寄存器

–Relative 间接寻址,多用于跳转

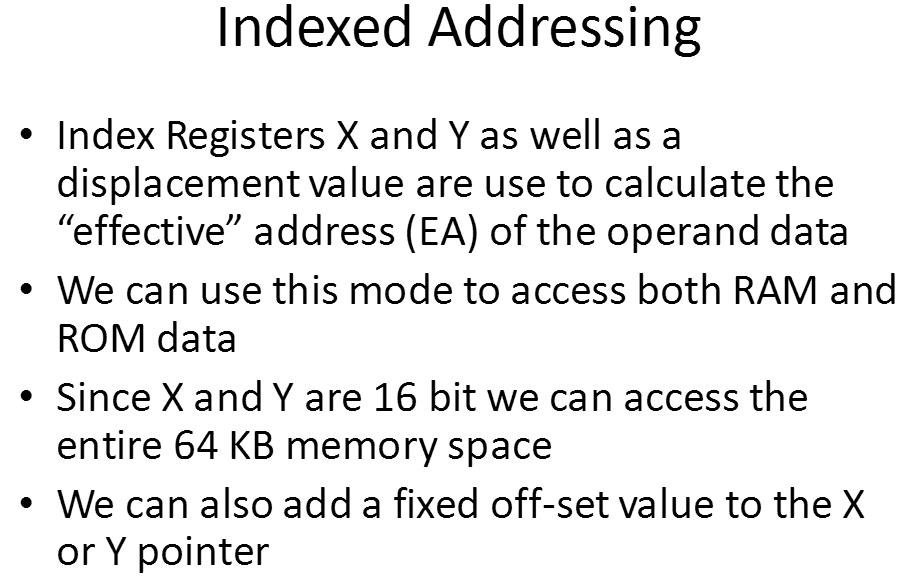

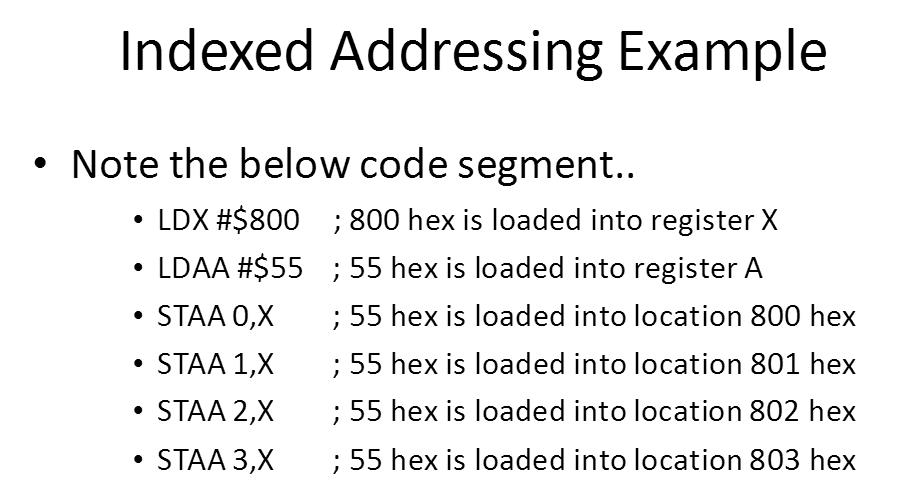

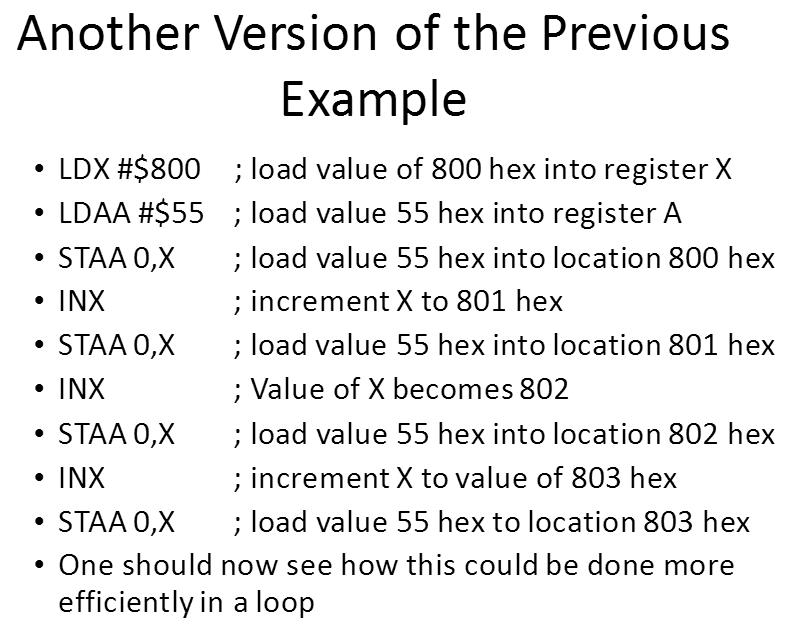

–Indexed 变址寻址,用 X、Y

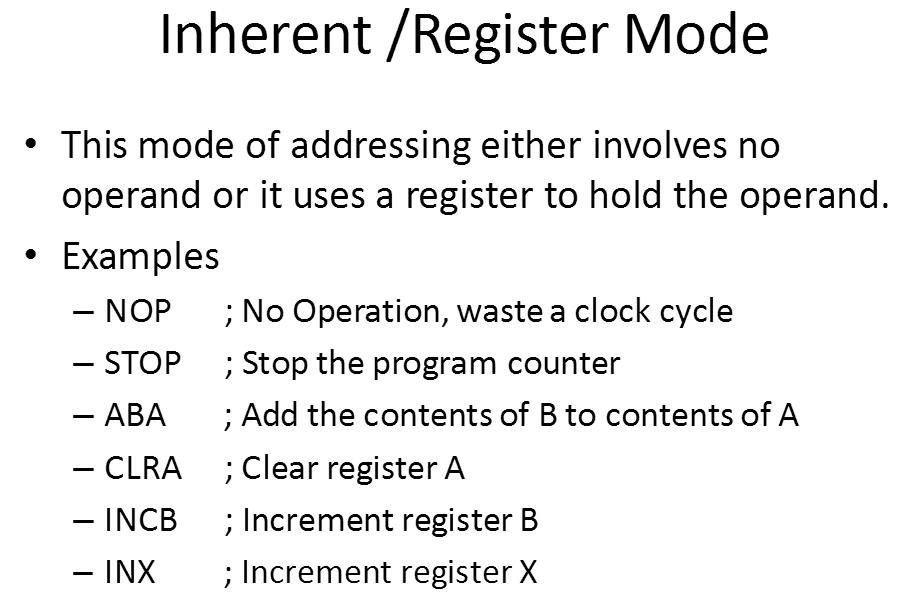

1、Inherent /Register Mode

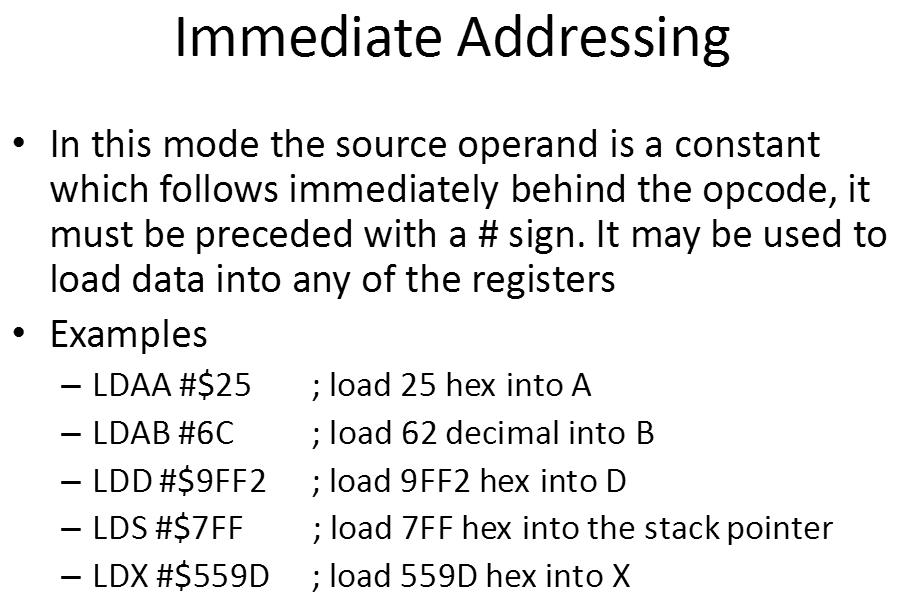

2、Immediate Addressing

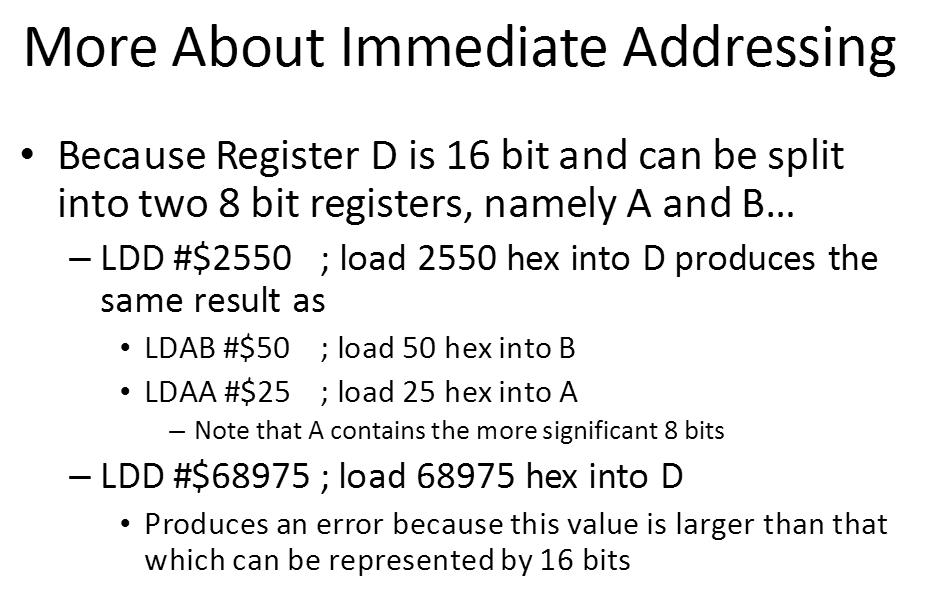

小端是高高低低,这里类似于大端,因为hcs12里面,A地址小于B

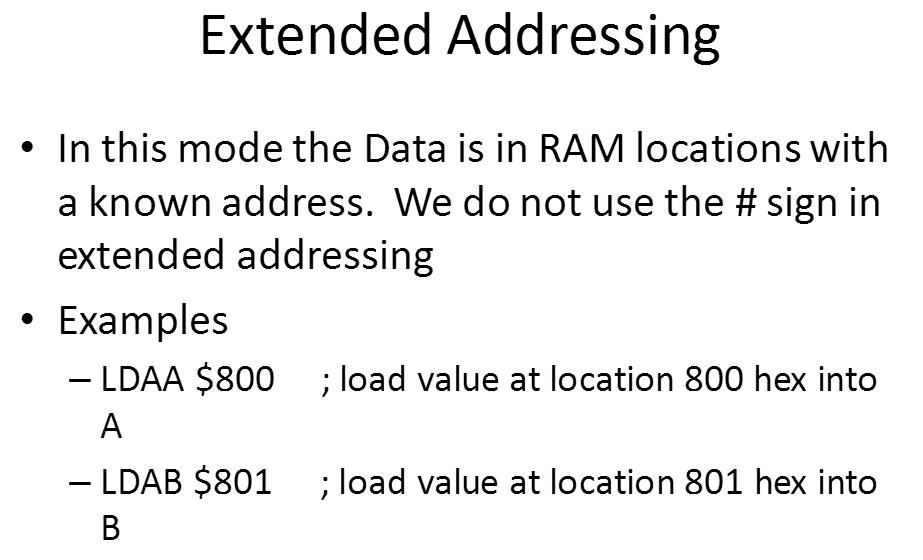

3、Extended Addressing

大小端模式

Freescale 微处理器都是大端模式

4、Direct Addressing

特殊的 Extended Addressing,用地址空间寻址寄存器

Note the below equivalent methods of storing contents of register A into PORTA

•STAA $00 == •STAA PORTA

5、Relative addressing 间接寻址,多用于跳转

6、Indexed Addressing 变址寻址,用 X、Y

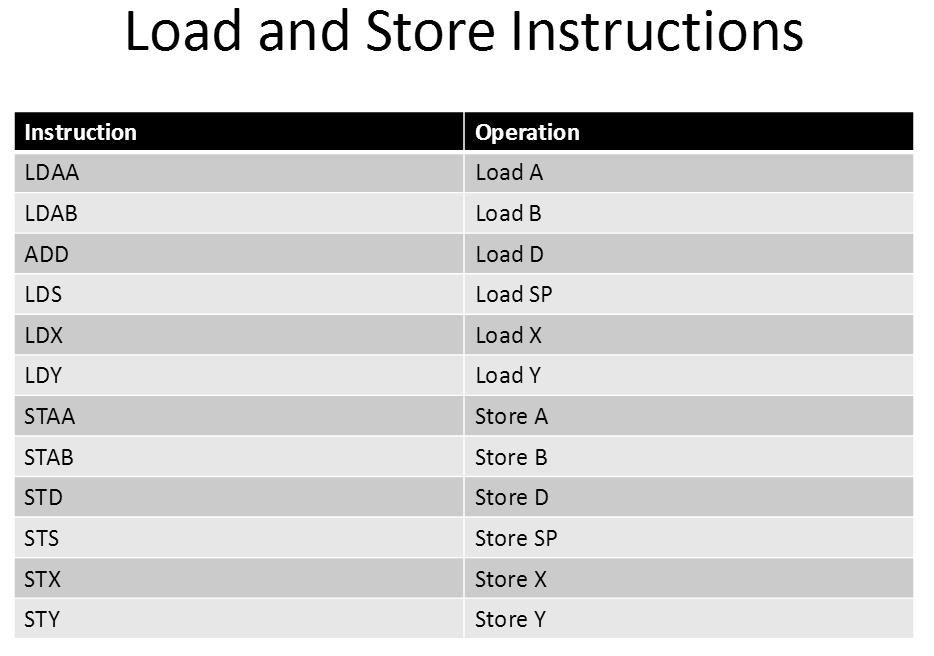

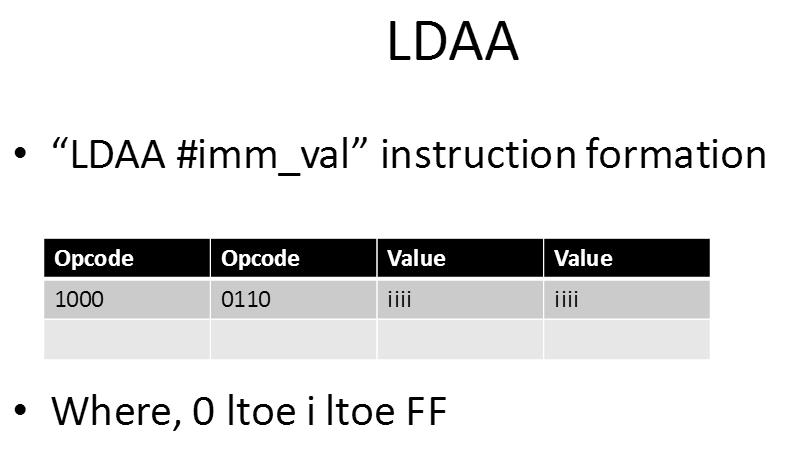

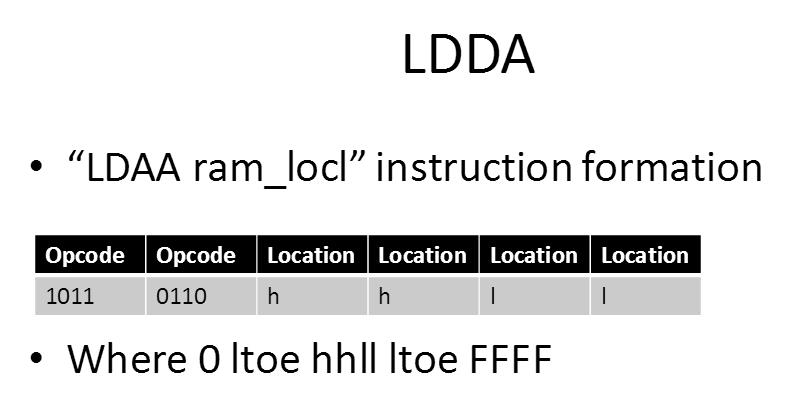

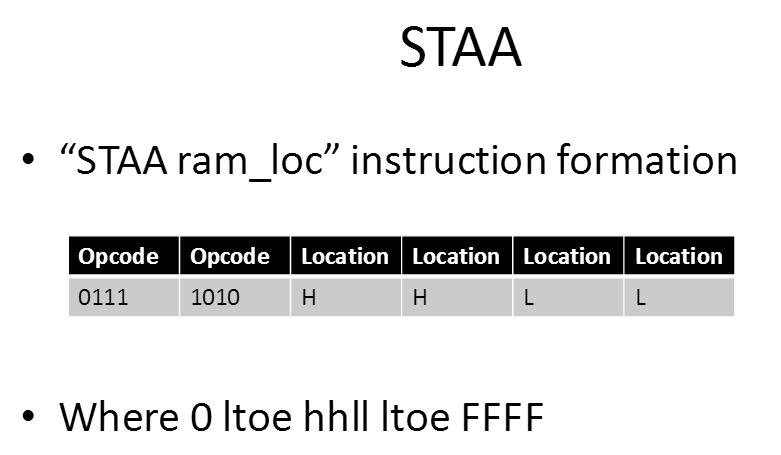

**7、(重要)Load and Store Instructions

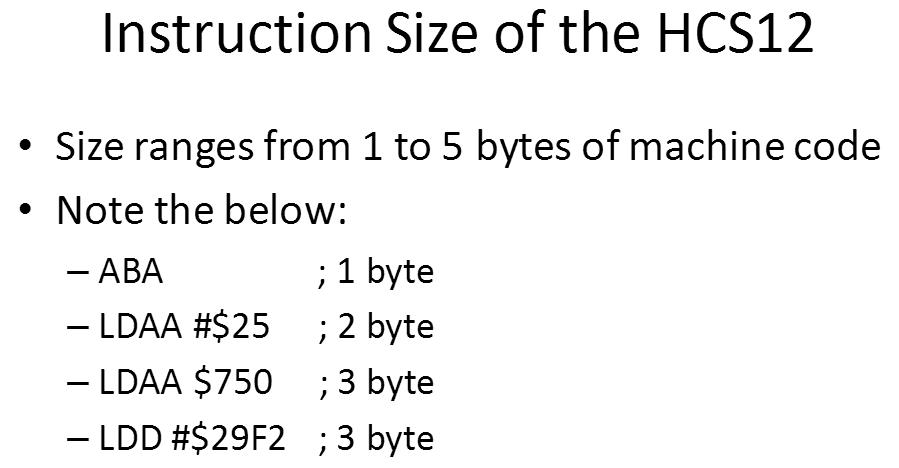

8、Instruction Size of the HCS12

2-4 HCS12 Condition Code Register(CCR)

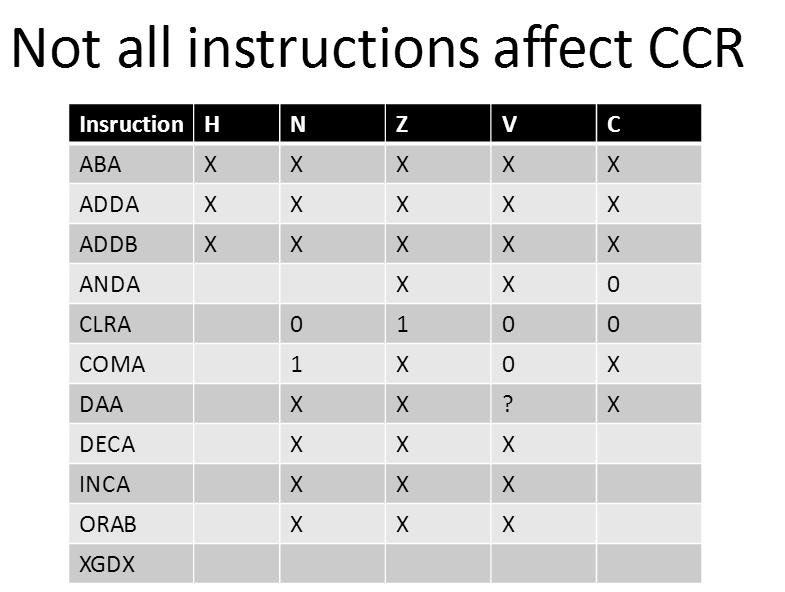

1、C, the carry flag

•Set whenever there is a carry out from the D7 bit

•Affected after 8 or 16 bit addition or subtraction

2、H, the half byte carry flag

•Set when there is carry from D3 bit

•Cleared otherwise

•Used by operations that perform binary coded decimal arithmetic

•Sometimes called the Auxiliary Carry or AC flag

3、Z, the zero flag

•Reflects the result of an arithmetic or logic operation

•Set to 1 for a 0 result

•Set to 0 if result is not zero

•Useful for looping

4、V, the overflow flag

•This flag is set whenever the result of a signed number operation is too large

•The sign bit will therefore be overwritten

5、N, the negative flag

•Bit D7, the MSB in binary representation of 8 bit signed numbers is used to represent sign

–It is 0 for positive numbers and 1 for negative

numbers

•N is 0 when D7 is 0 •N is 1 when D7 is 1

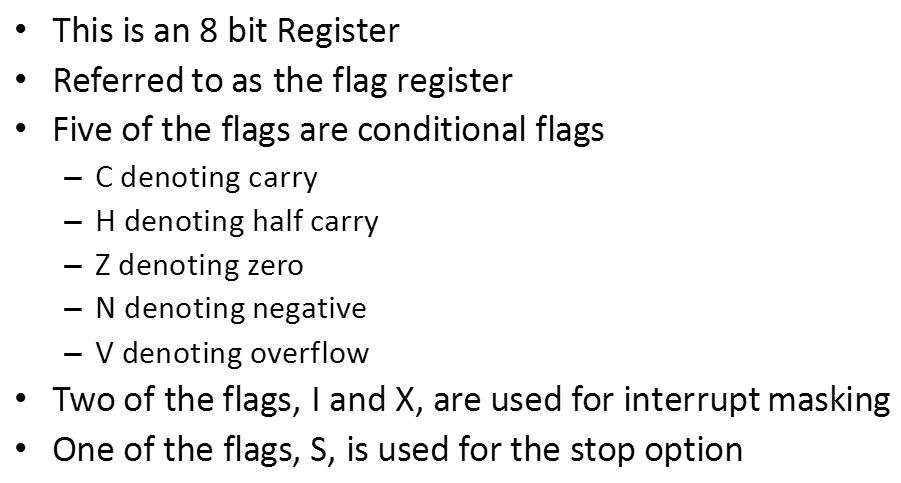

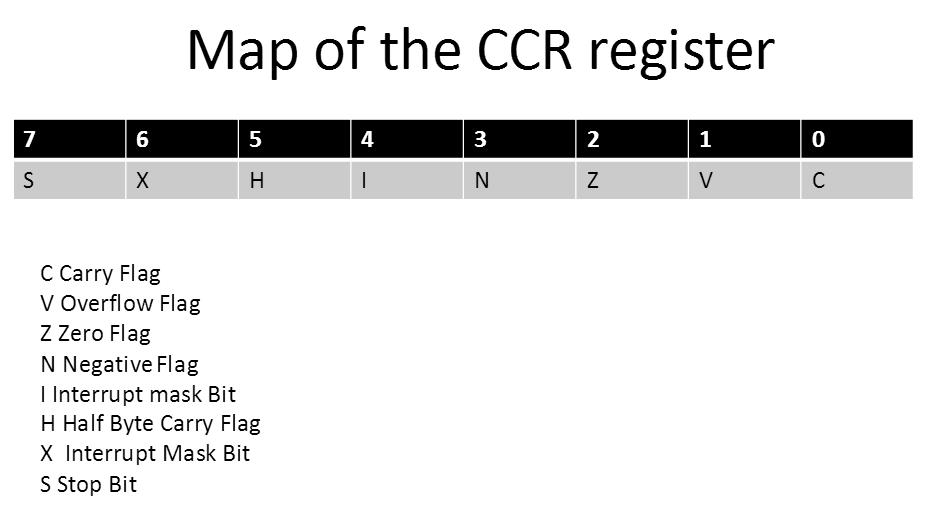

**6、(重要)CCR register

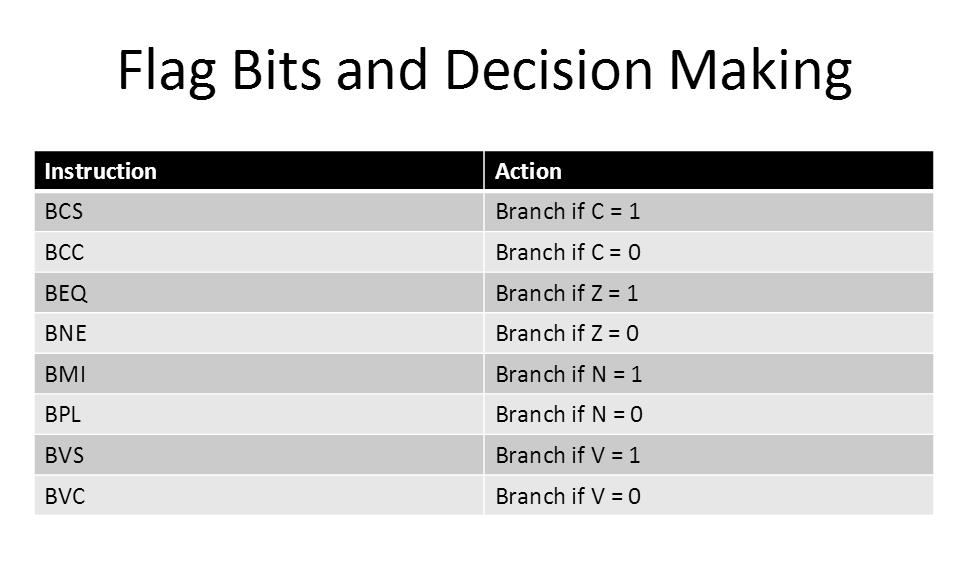

**7、(重要)分支语句(1)CCR基本跳转

2-5 HCS12 Data Format and Directive

4 ways to represent a byte of data in the HCS12 assembler

–Hex

–Binary

–Decimal

–ASCII

1、hex

•Assembly:

–Precede number with $ sign

–Eg. LDDA #$25

•C language

–Precede number with 0x

–Eg. PORTB = 0x99

2、Binary Numbers

•Number is preceded by % sign

–Eg. LDDA #% 00100101 ; 25 hex

3、Decimal Number

•There is no symbol in front of the number

–Eg LDDA #12 ; 0C hex

4、ASCII CHARACTER

•Single quotes around the character are used to denote it as ASCII.

–Eg. LDAA #’9’ loads the value for the character 9

(39 hex)

•Double quotes are used for a string

–Use with the DC (define constant) directive

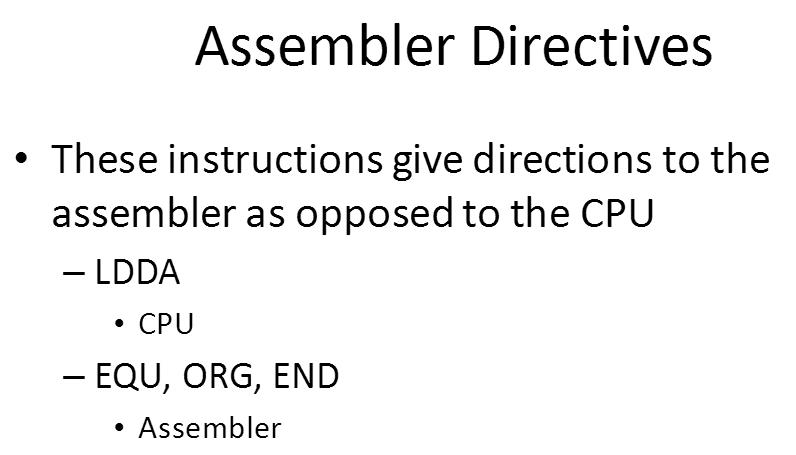

Assembler Directives

6、EQU

•This is used to define a constant value or fixed address

–Eg. COUNT EQU $25 ; Value of Count defined as 25 hex

–LDDA #COUNT ; Value of register A is 25 hex

SET

•Same as EQU except that:

–Value assigned by the SET directive may be reassigned later

USING EQU for RAM address assignment

•MYCOUNT EQU 5

•MYREG EQU $1200

–LDDA #MYCOUNT

–STAA MYREG ; NOW LOCATION 12OO H IS VALUE 5

Another address example

MYVAL EQU $33

MYRAM EQU $1200 ;RAM ADRESS 1200 H

LDAA #MYVAL ;A = 33H

STAA MYRAM ; STORE A CONTENTS TO 1200 H

STAA MYRAM +1 ; A CONTENT TO 1201 H

STAA MYRAM +2 ; ACONTET TO 1202 H

CLR A ; CLEAR CONTENTS 0F A

ADDA MYRAM ; A=33 H

ADDA MYRAM +1 ; A=66H

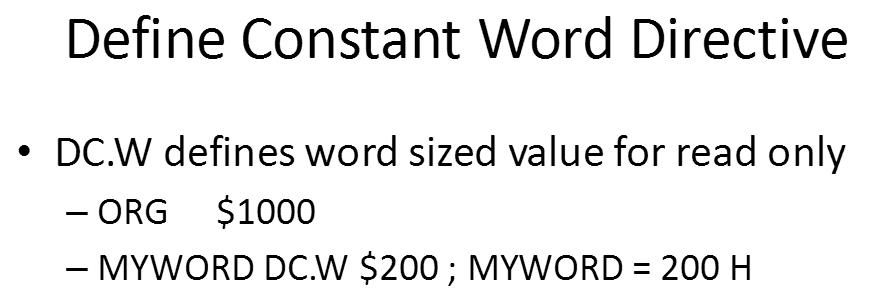

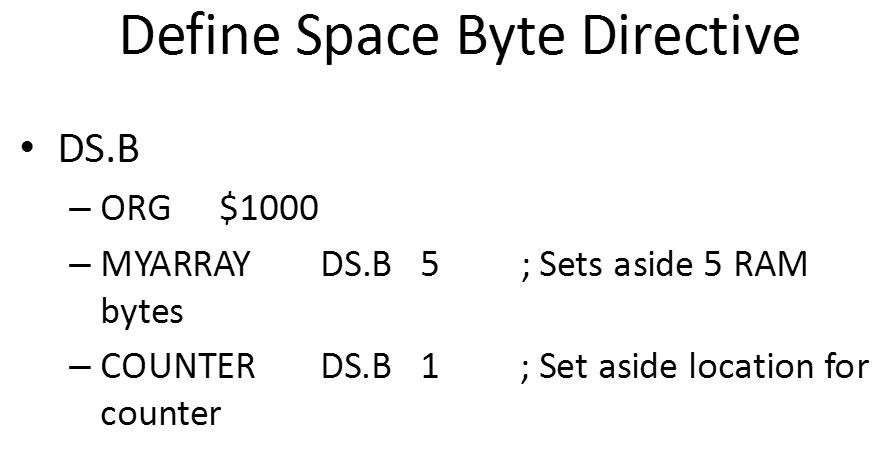

ADDA MYRAM +2 ; A=99 H7、ORIGIN and END DIRECTIVE

•ORG indicates the beginning of the address space

ORG tells the assembler to place the opcode at memory location 0

END DIRECTIVE

•END indicates the end of the source source code.

END indicates the end of the source code to the assembler

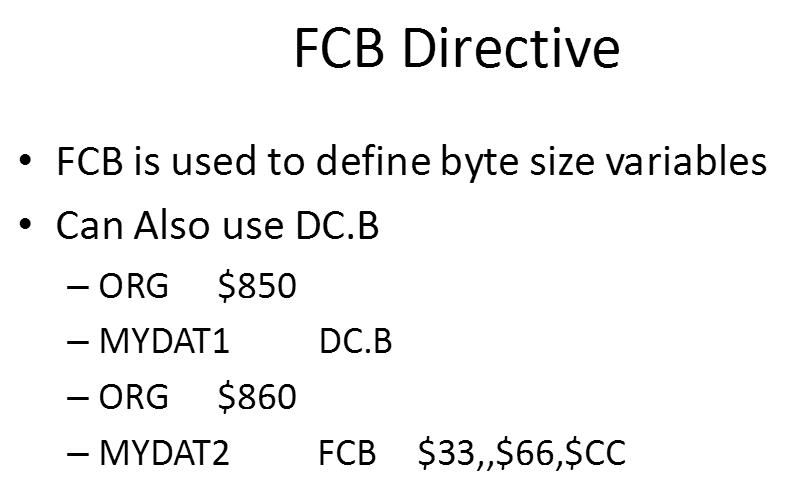

8、FCB Directive 可用来定义字符串

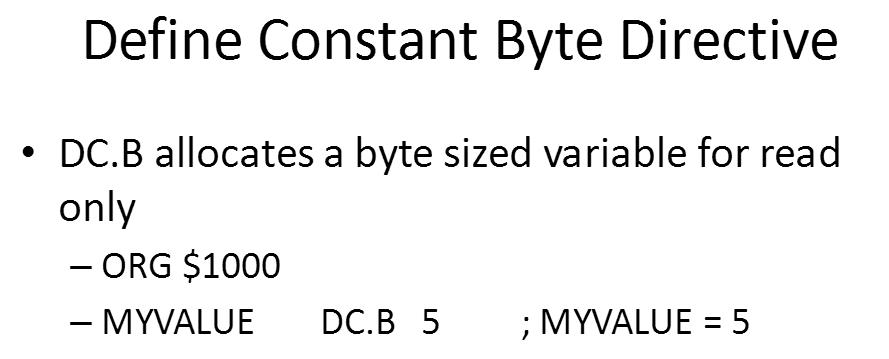

**9、Define Constant Byte Directive 可用来定义字符串

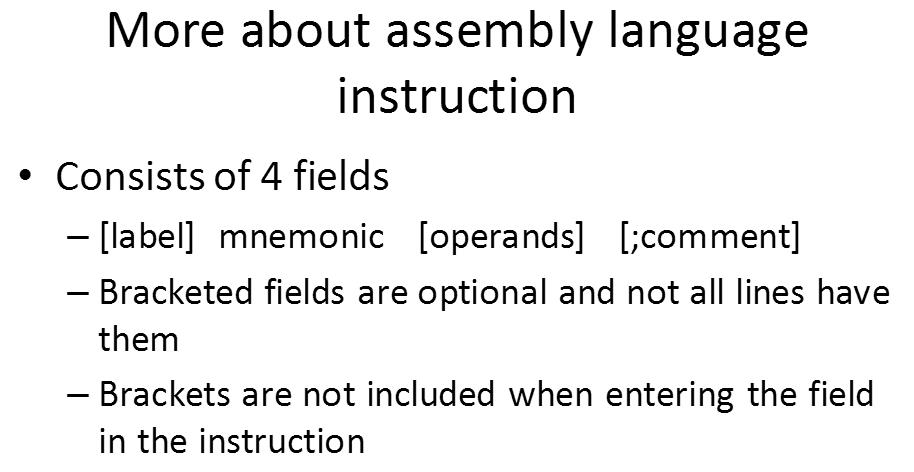

2-6 Introduction to HCS12 Assembly Language

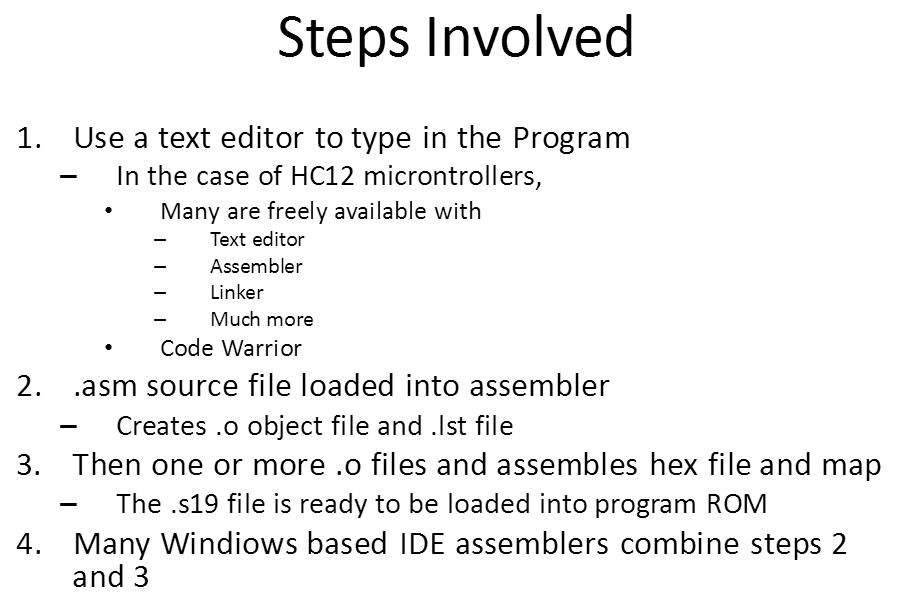

2-7 Assembling and Linking an HCS12 Program

1、链接顺序

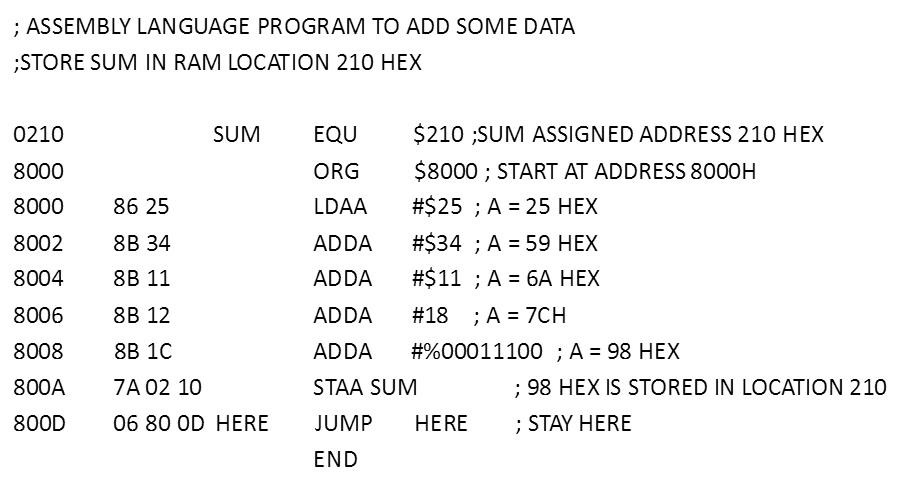

2、例子如下

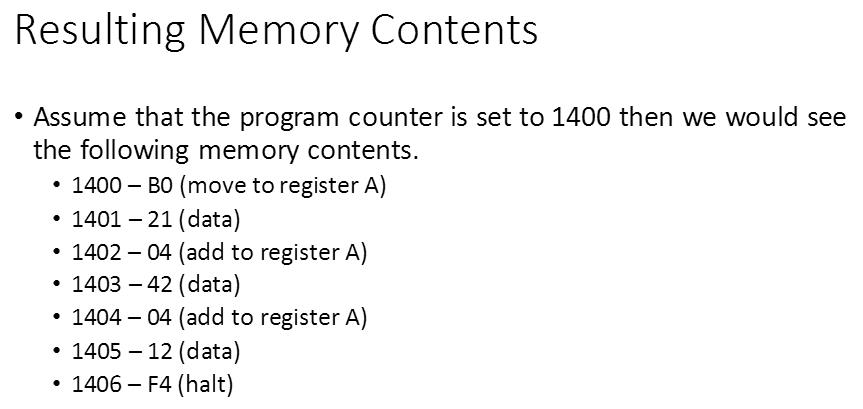

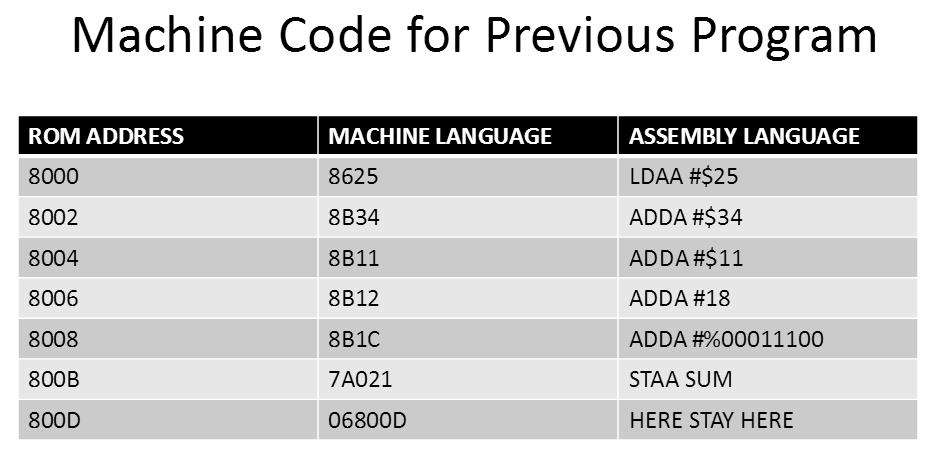

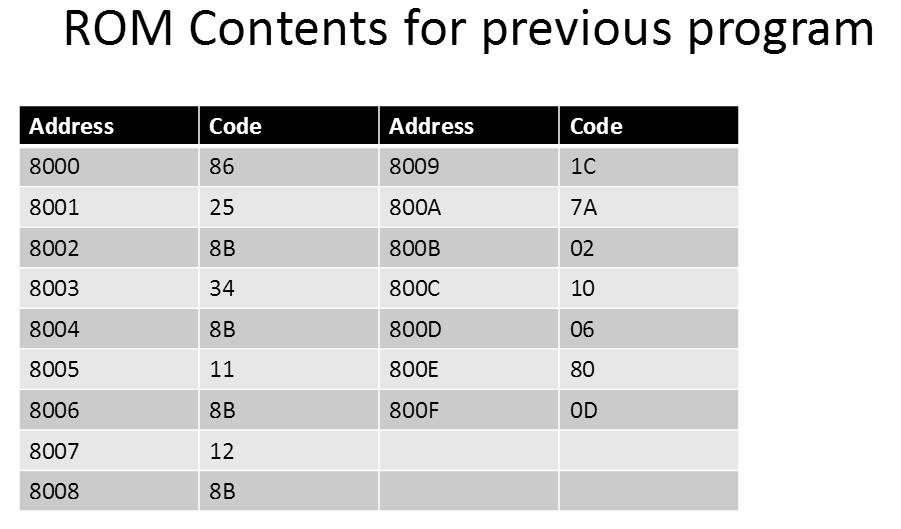

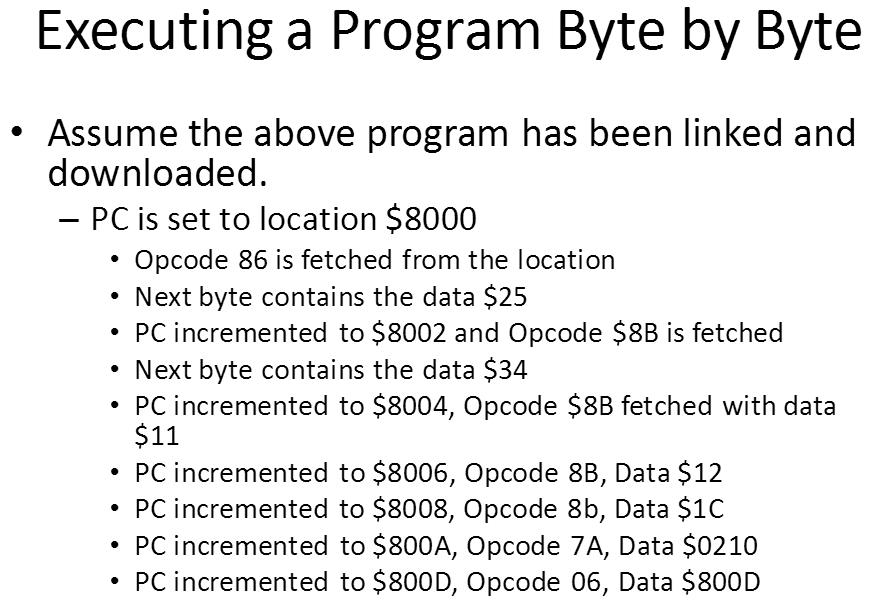

3、Executing a Program Byte by Byte

2-8 Stack and Data Transfer Instructions

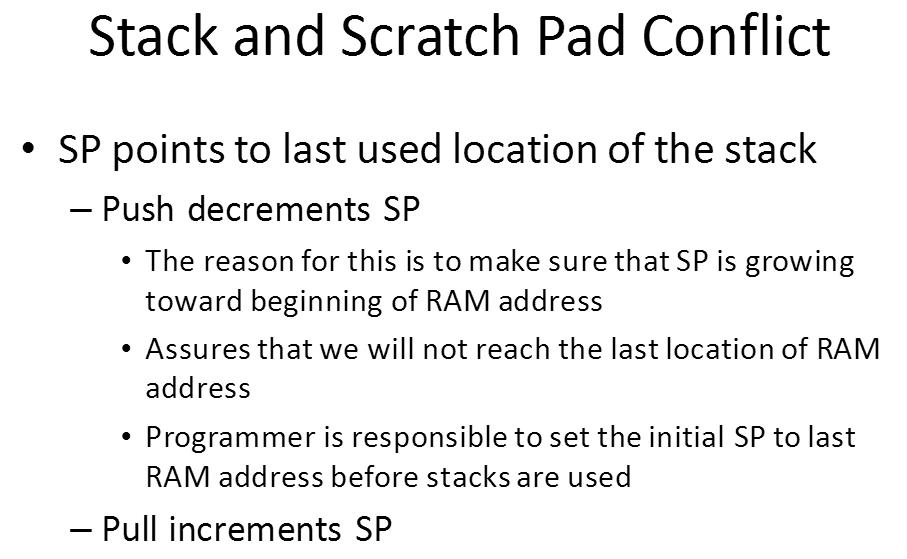

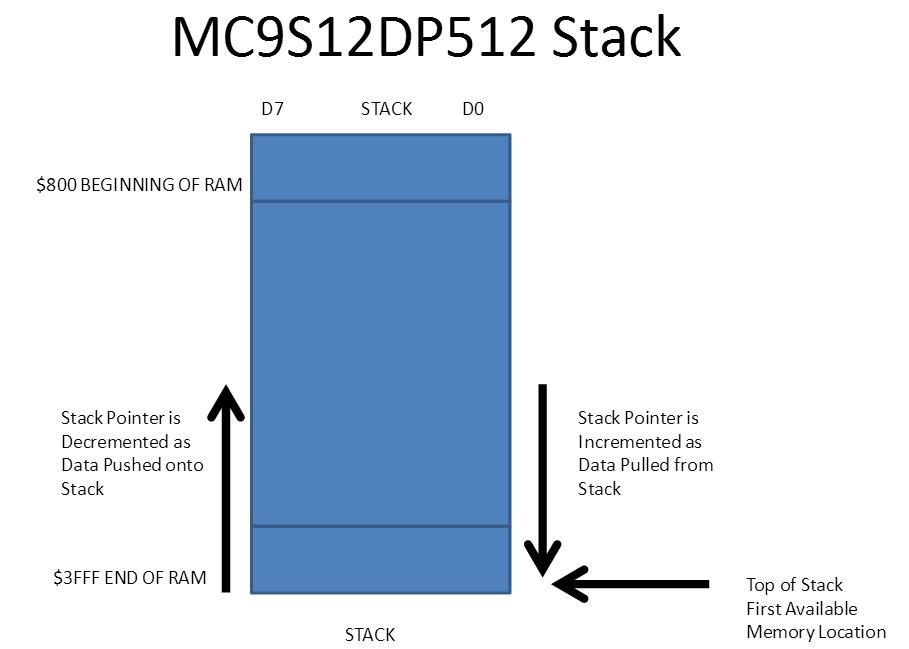

1、How Stacks are Accessed in the HCS12

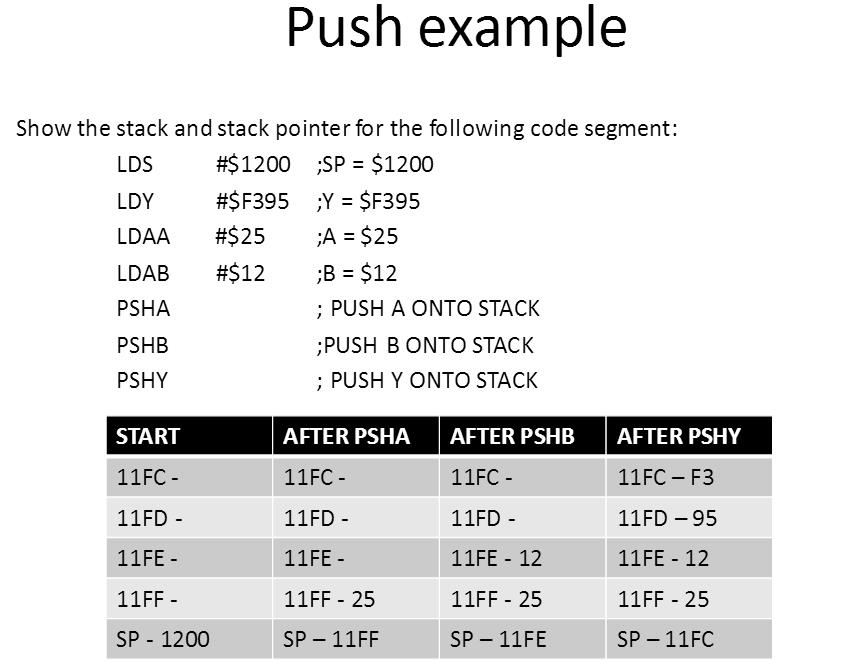

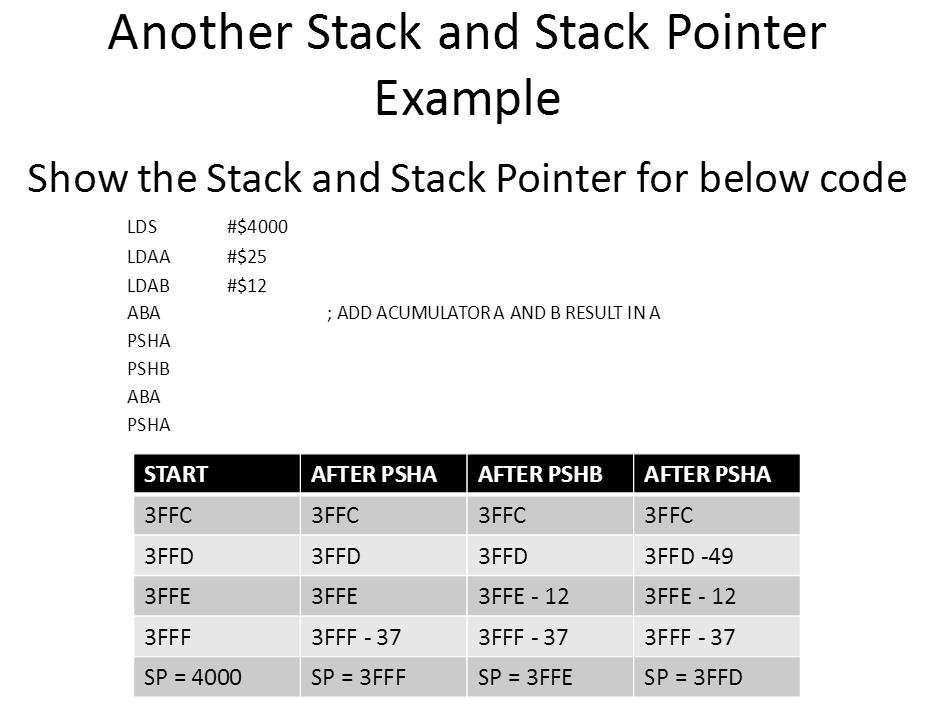

2、Pushing onto the Stack

•Stack Pointer points to last used location of the stack

–SP is decremented each time we push

–This is a common convention

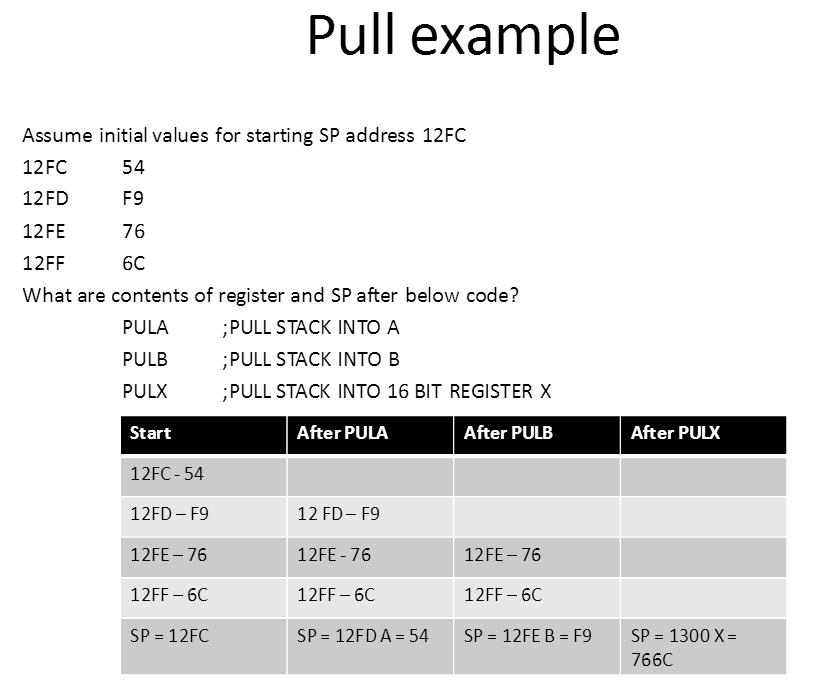

3、Pulling From the Stack

sp在ram最后

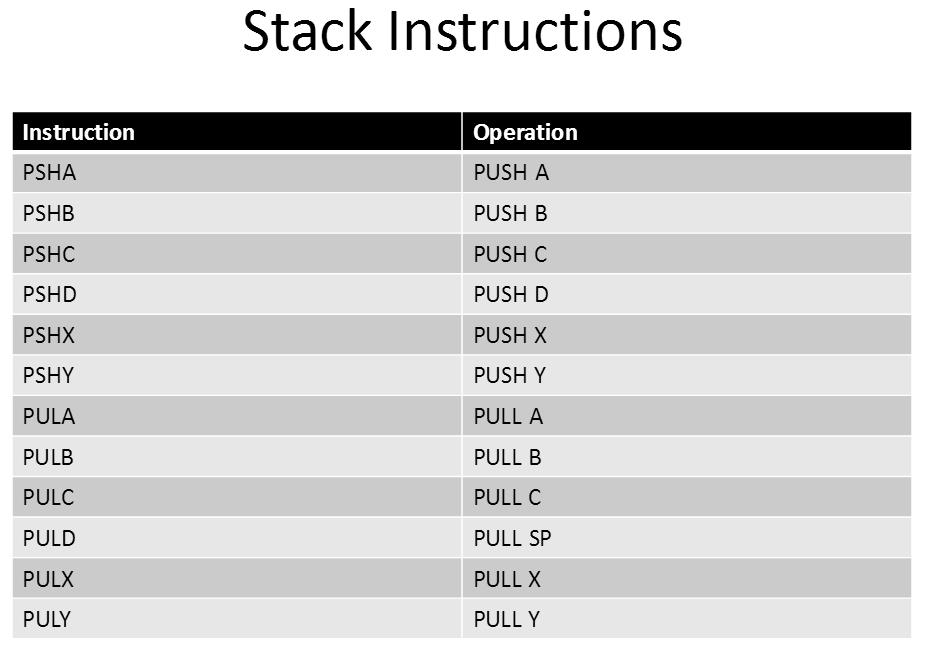

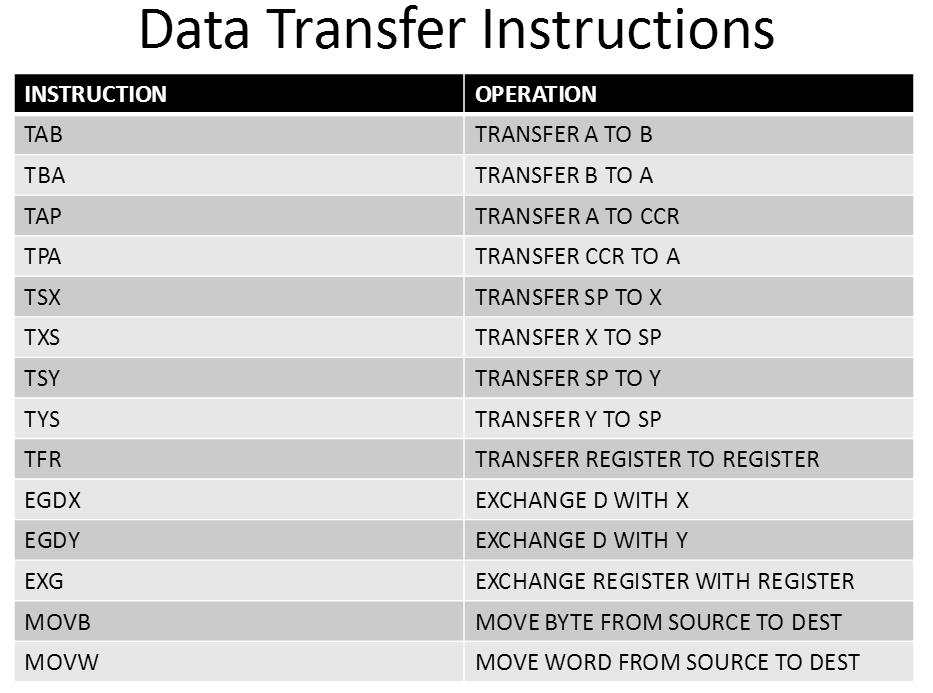

**4、(重要)Stack Instructions & Data Transfer Instructions

Ram area can be thought of as a large number of register

We can rename them as long as we do not use reserved names for SFR’s

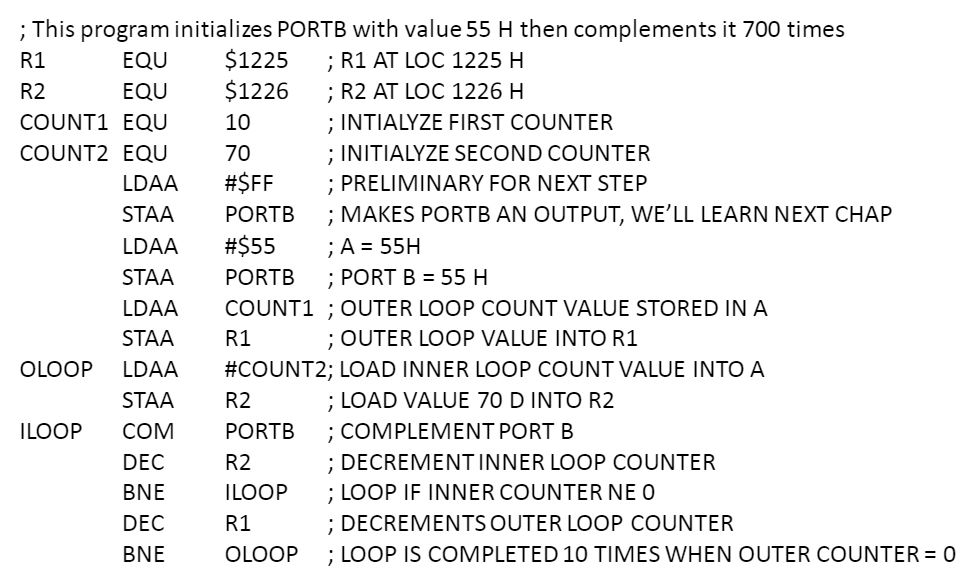

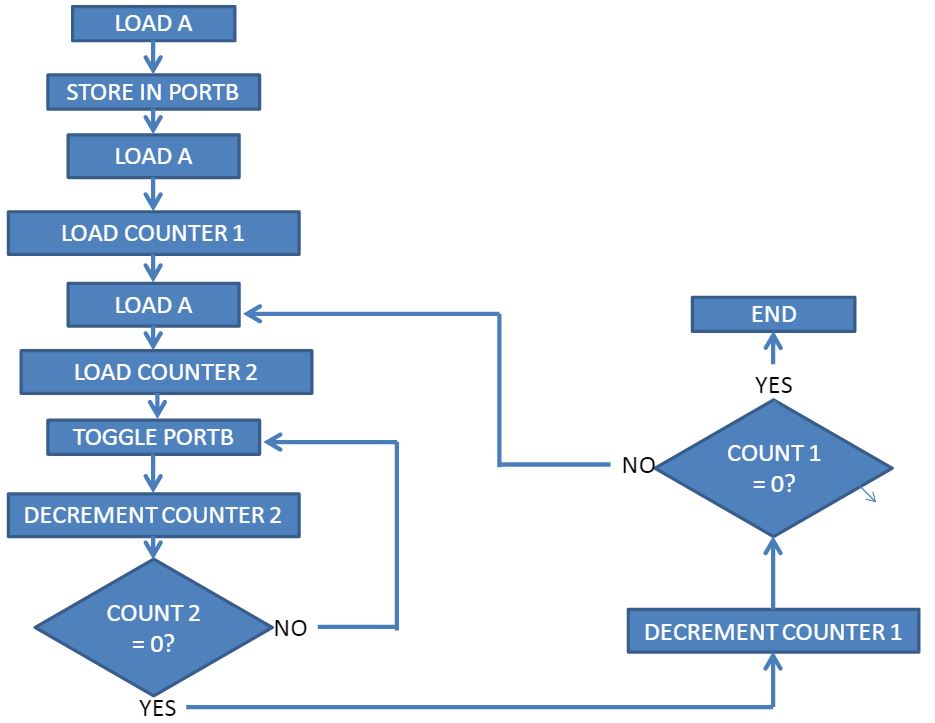

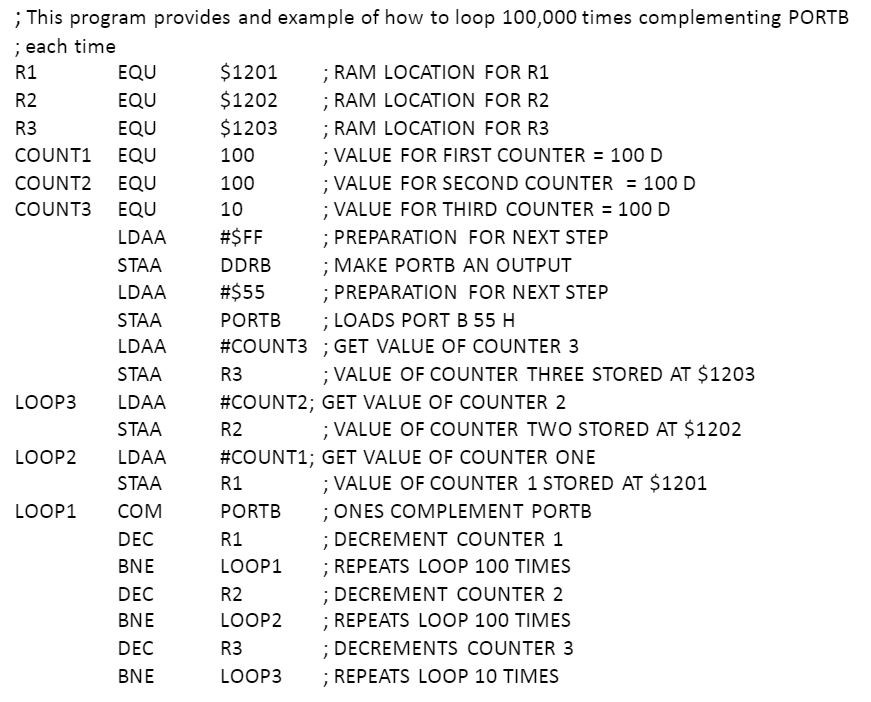

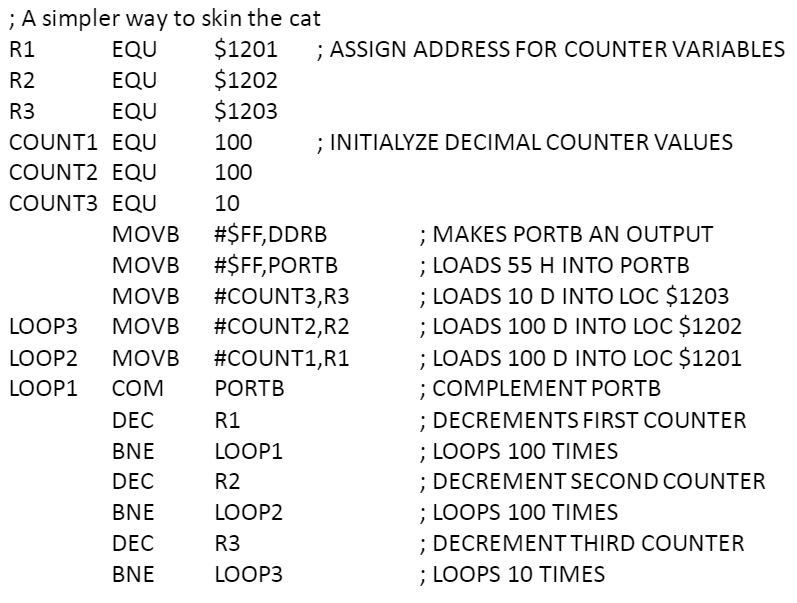

三、Chapter 3 Branch, Call and Time Delay Loop

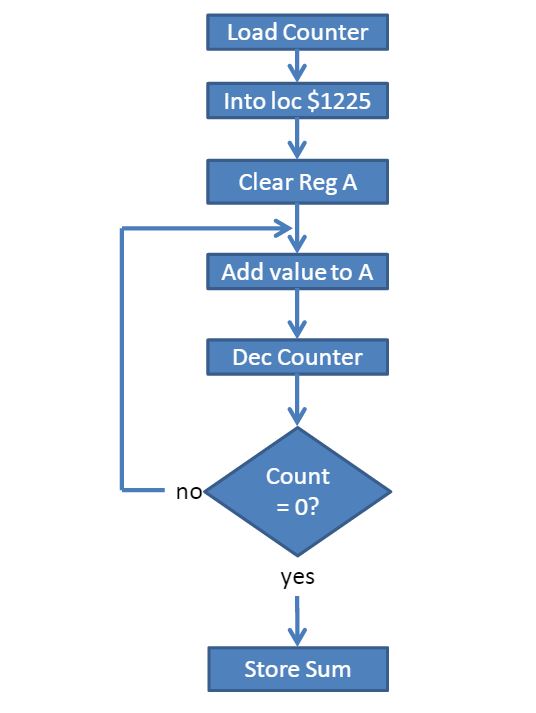

3-1 循环

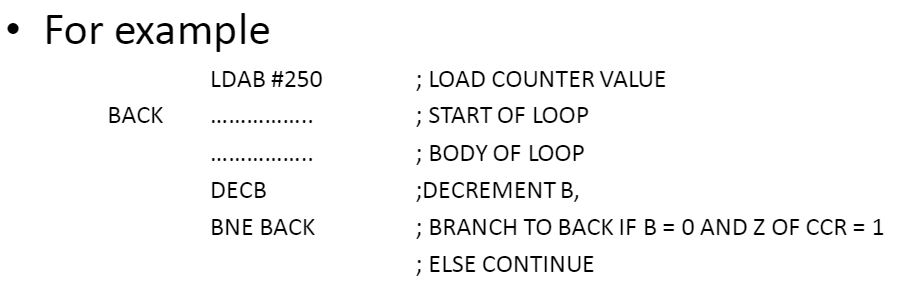

1、Using instruction BNE for Looping

•BNE stands for Branch if Not equal to 0

•For example

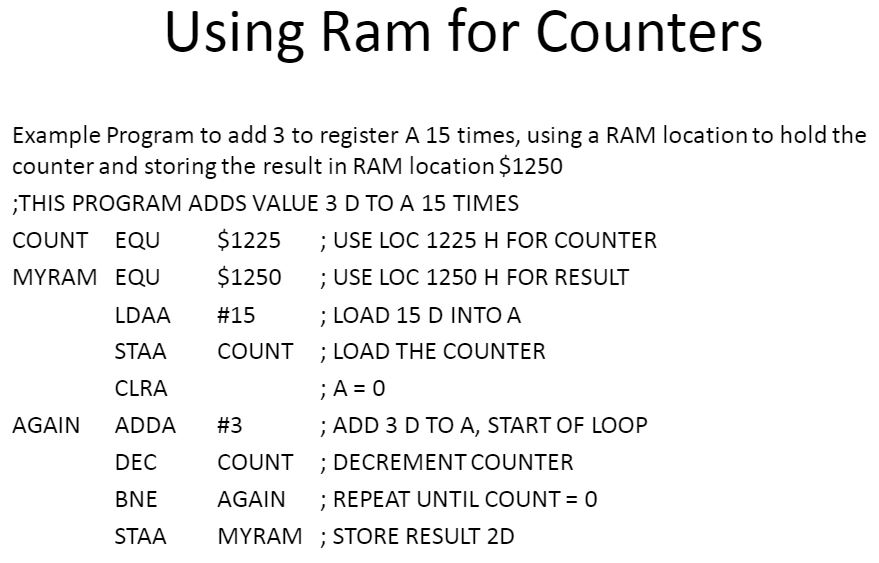

2、Using Ram for Counters

Limitation of previous example

•Because Count is an 8 bit register:

–Maximum of 255 times or FF loops

–One way to overcome this is a nested loop

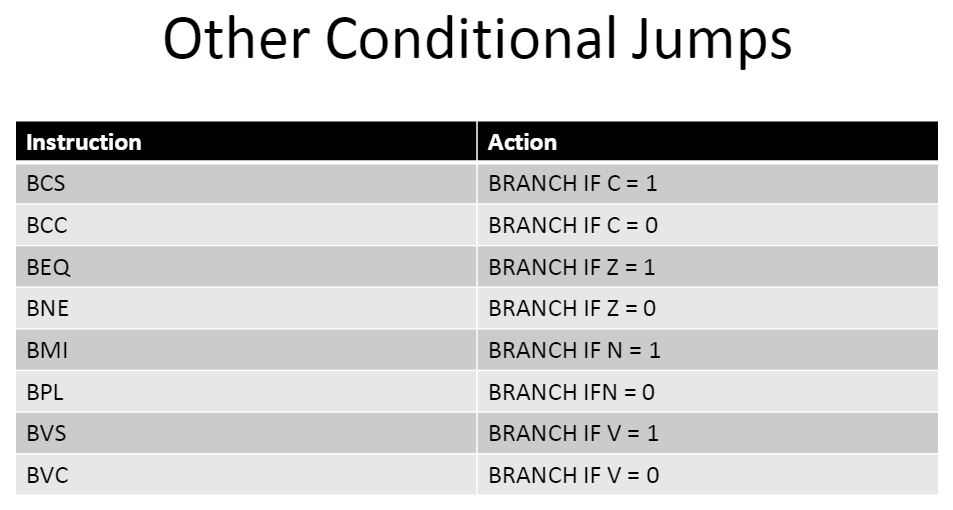

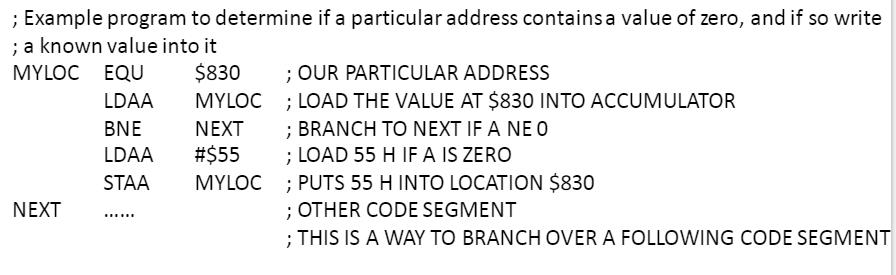

**3、(重要)Other Conditional Jumps

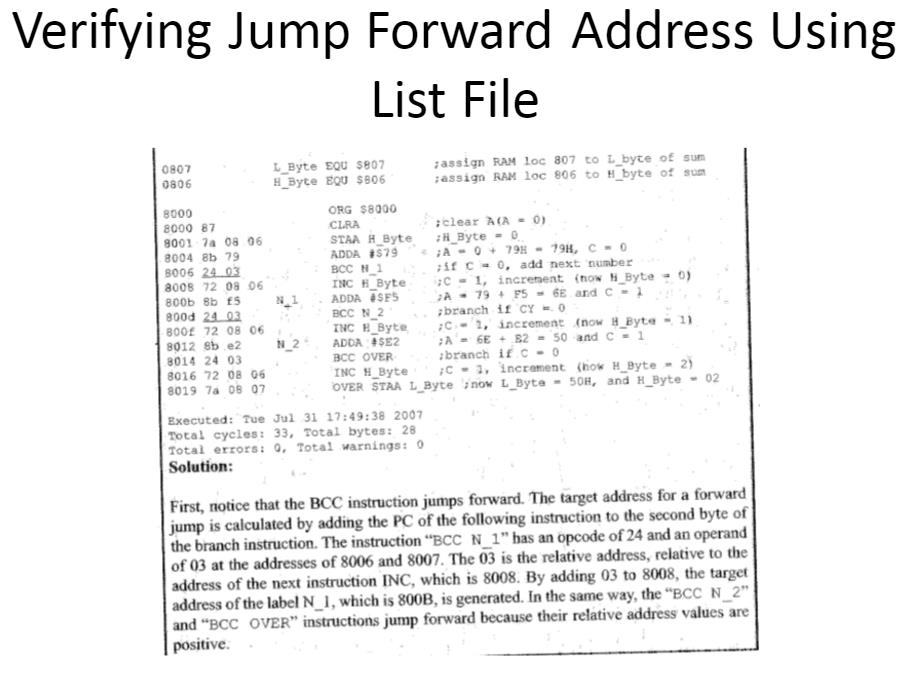

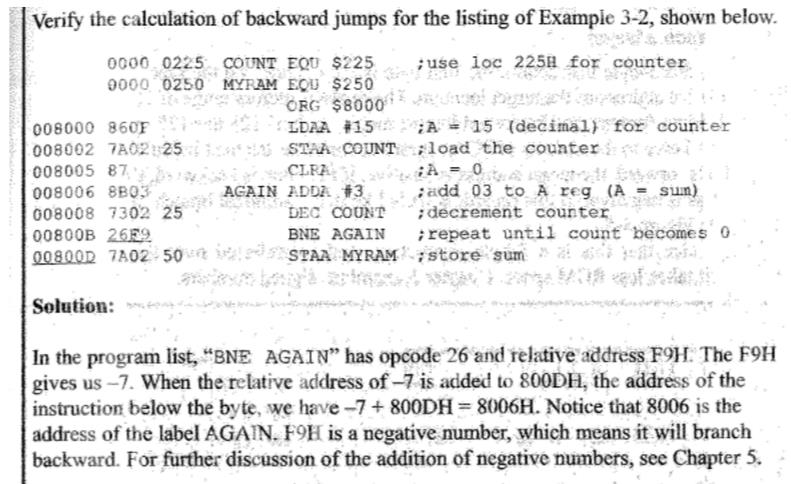

4、Short Conditional Branches

•Target must be within 128 bytes of the contents of PC

•These are 2 bytes instructions

•First byte is opcode

•Second byte is relative address to PC

•Value of second byte may be between -127 and +128

•Jump forward on positive, backwards on negative

•Target address is sum of second byte and PC of next instruction

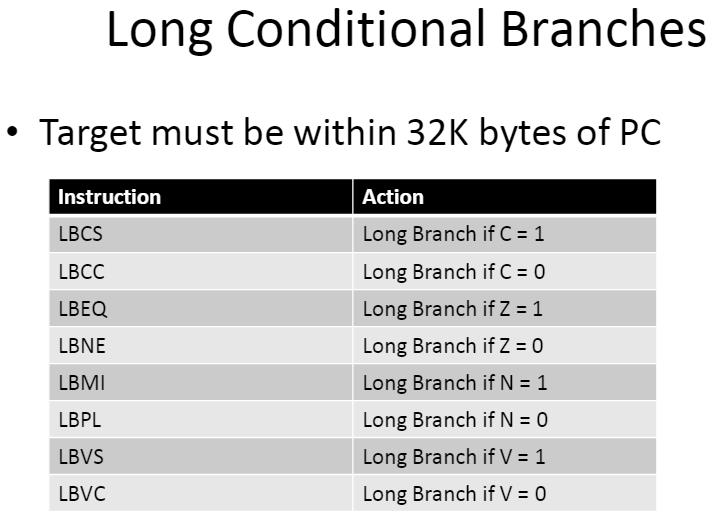

5、Long Conditional Branches

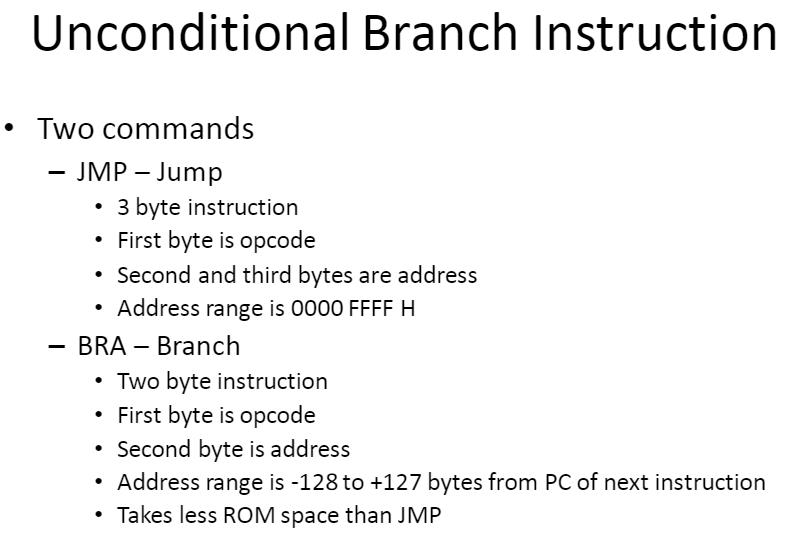

6、Unconditional Branch Instruction

Branching Using the $ Sign

HERE JMP HERE ;EQUIVALENT TO JMP $

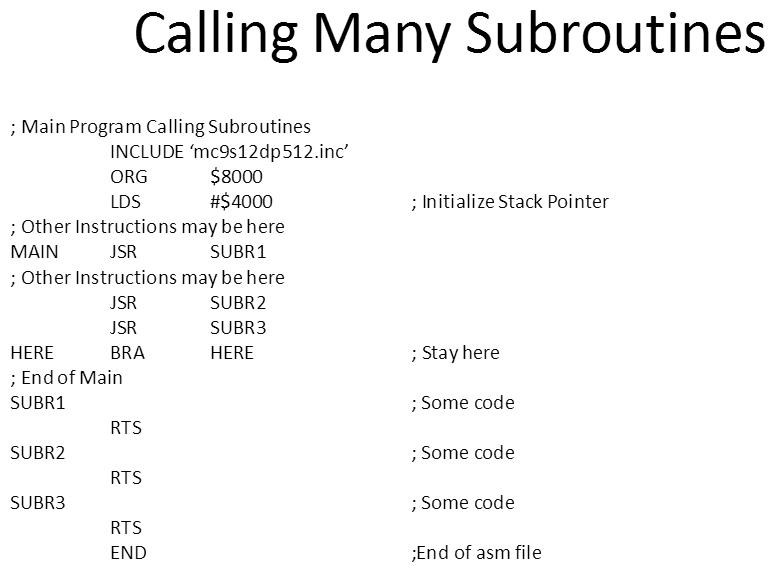

HERE BRA HERE ;EQUIVALENT TO BRA $3-2 JSR and CALL Instructions

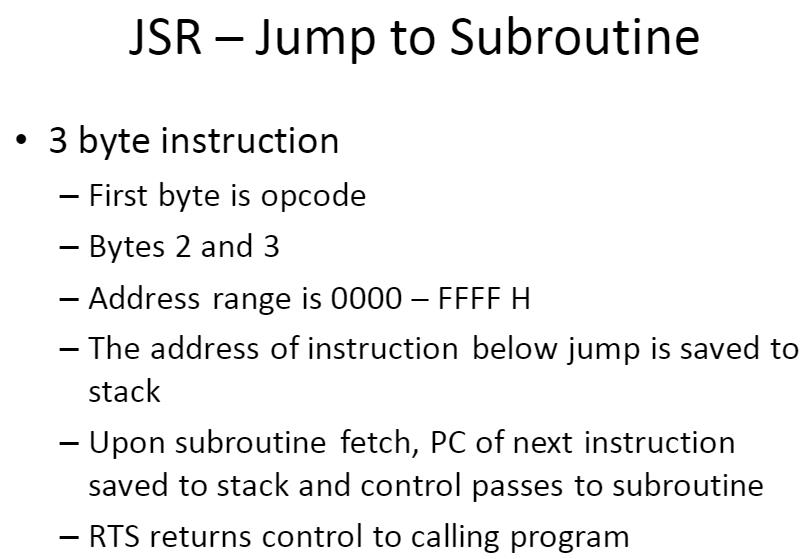

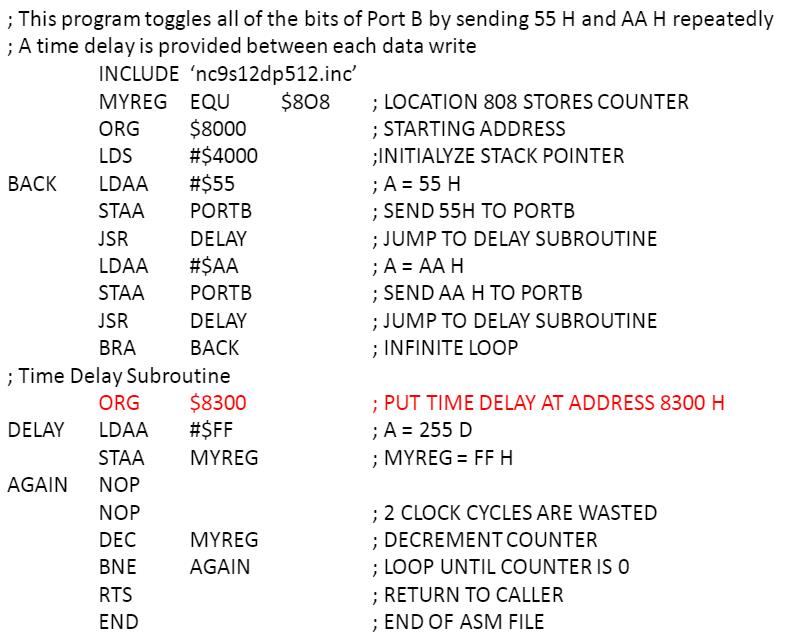

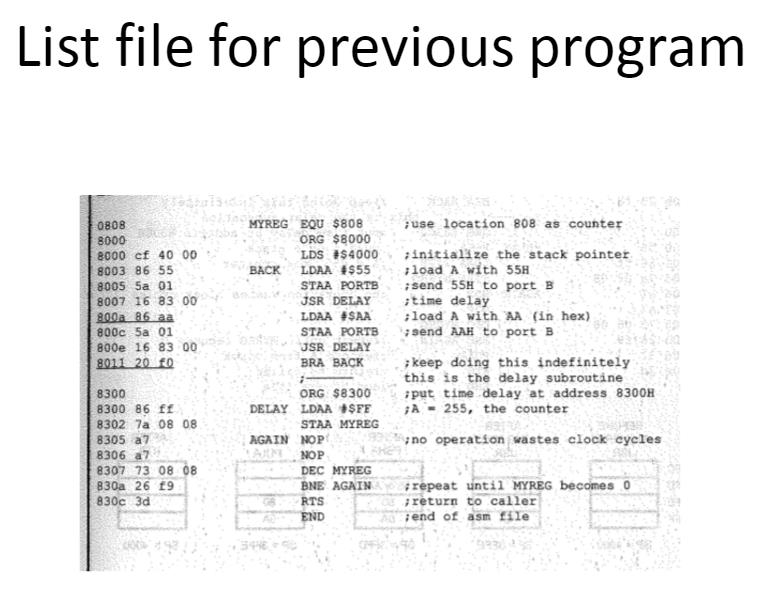

1、JSR – Jump to Subroutine

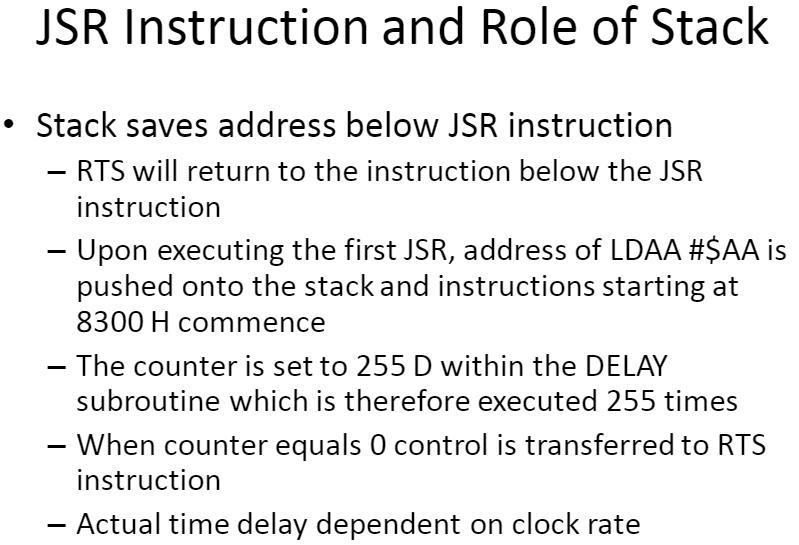

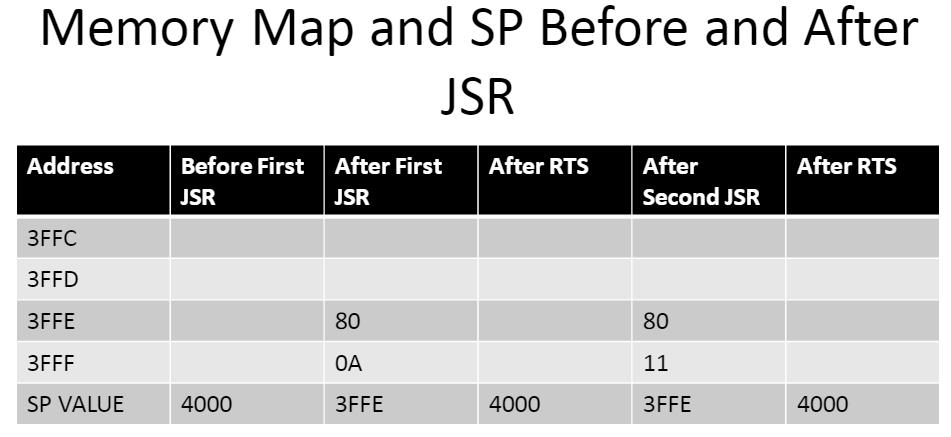

2、JSR Instruction and Role of Stack

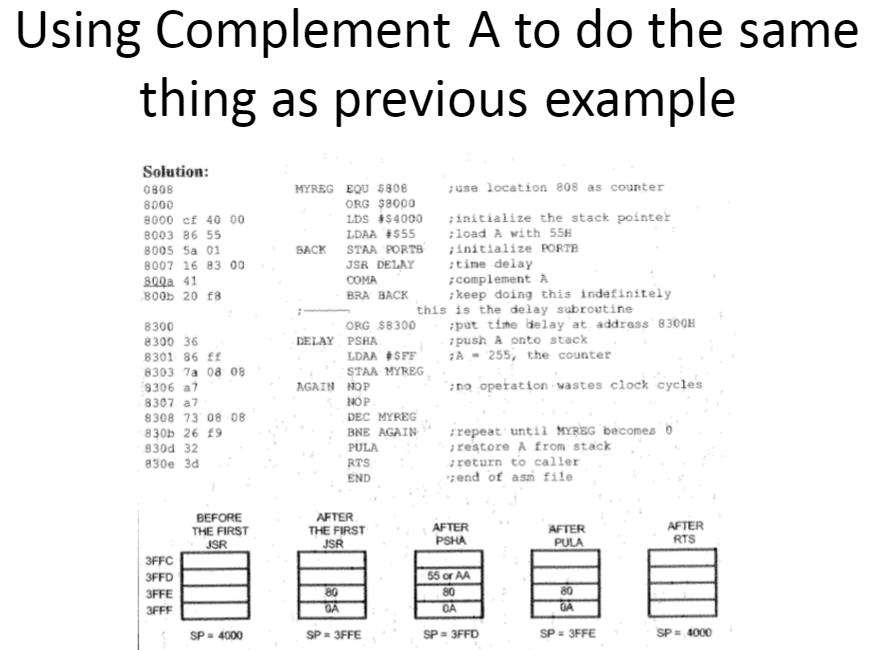

Complement A,即 COMA 指令,A 的反码

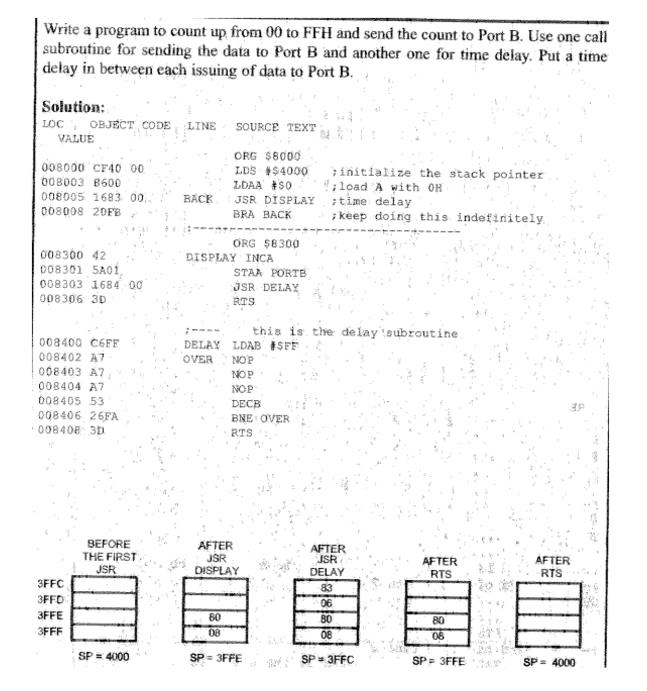

Another List Example

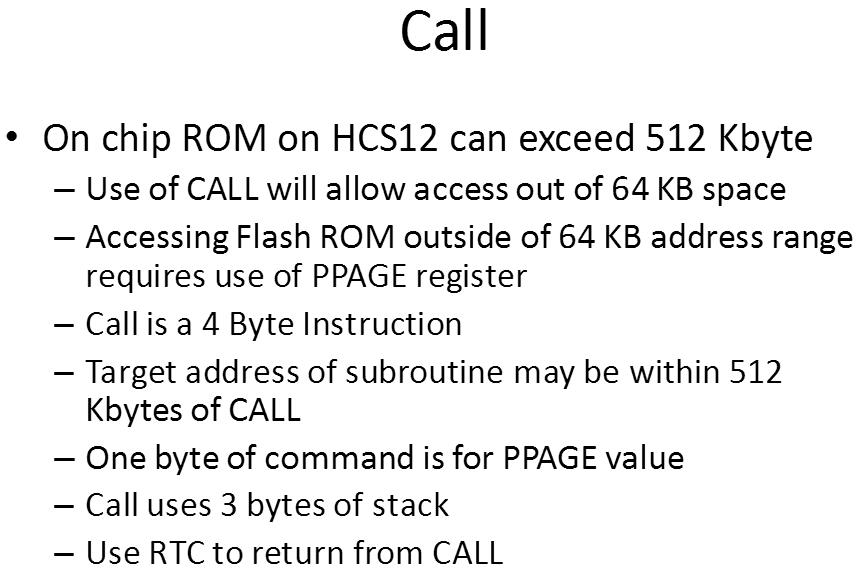

3、Call

4、CALL vs. JSR

•Assume your particular HCS12 is equipped with 32K on chip Flash ROM.

–Which command would you use?

–JSR is 3 byte instruction and saves ROM

–We do not need to use CALL because we will not go out of 64 KB range

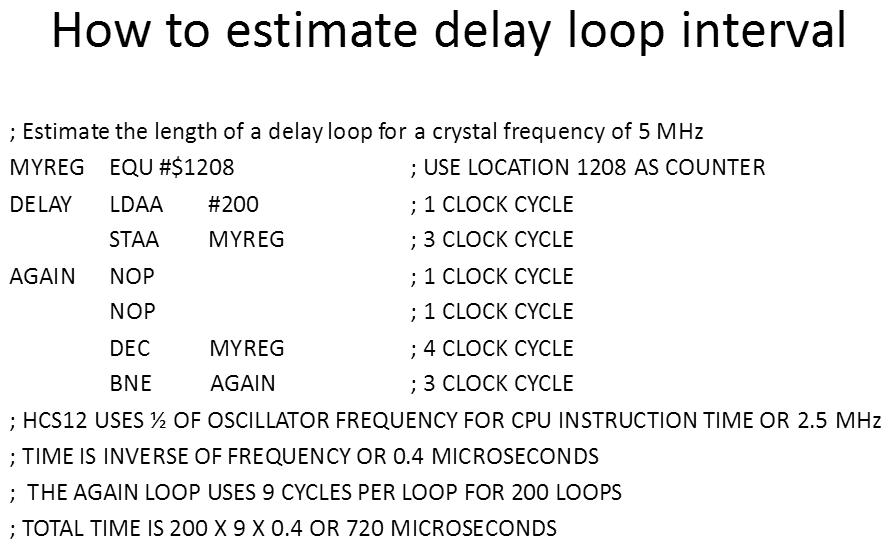

5、Delay Calculation for HCS12

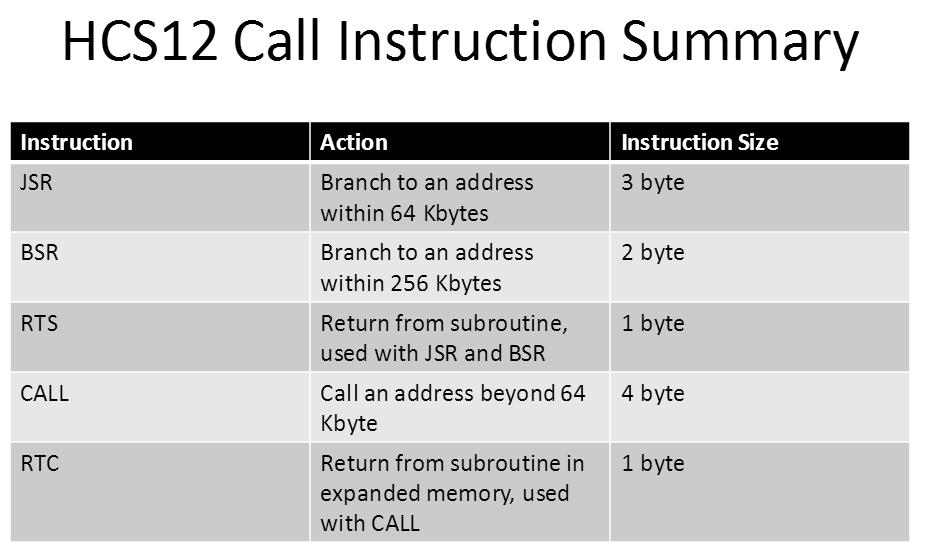

**6、(重要)HCS12 Call Instruction Summary

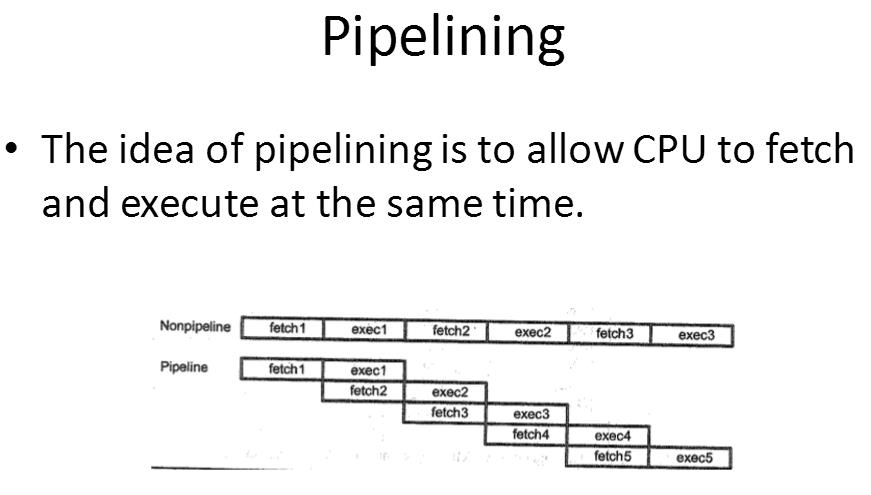

7、Pipelining

8、Instruction Queue and Branch Penalty

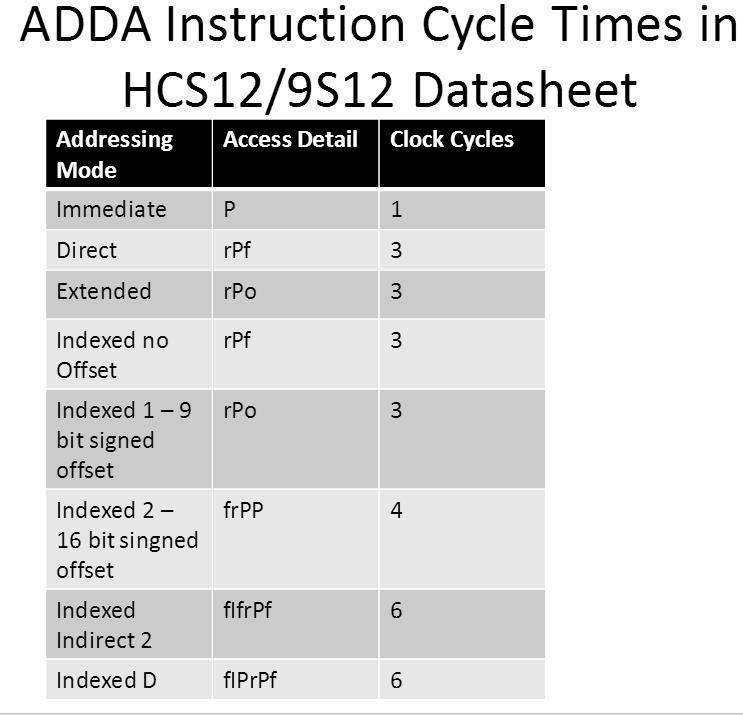

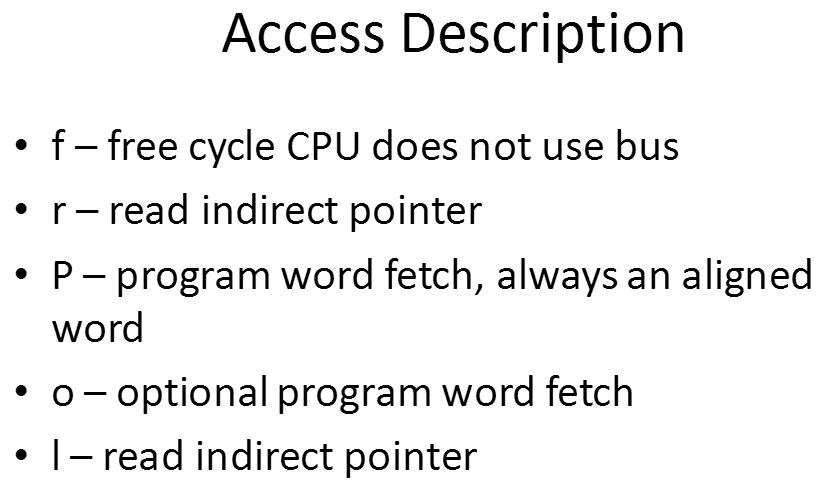

9、Access Description

Bottom Line

•Use timers for more accurate software generated delays

•This is covered in detail in Chapter 9

3-3 Programs Using Indexed Addressing Mode

变址寻址,用X,Y

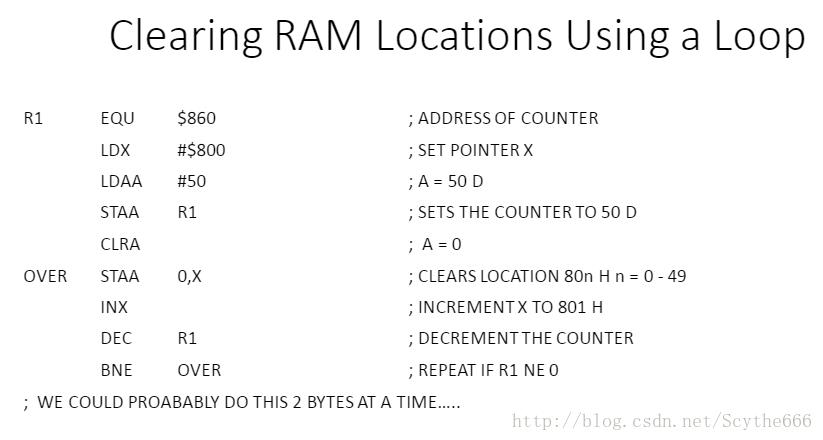

1、Clearing RAM Locations Using a Loop

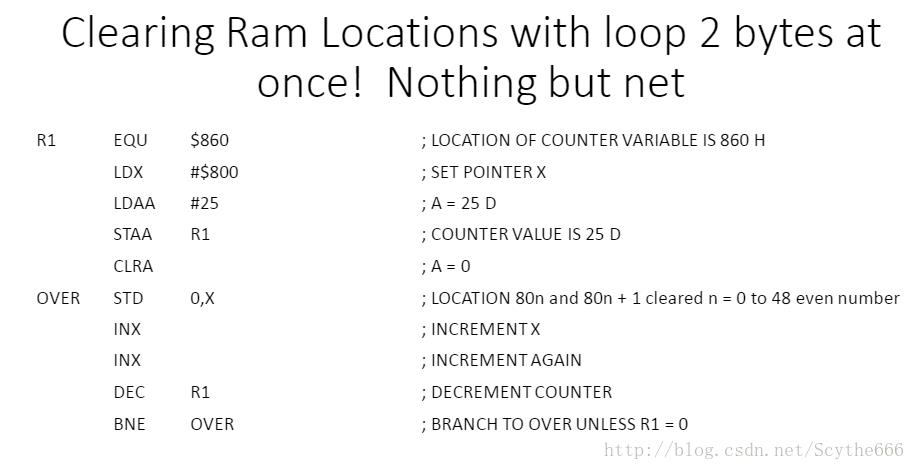

Clearing Ram Locations with loop 2 bytes at once! Nothing but net

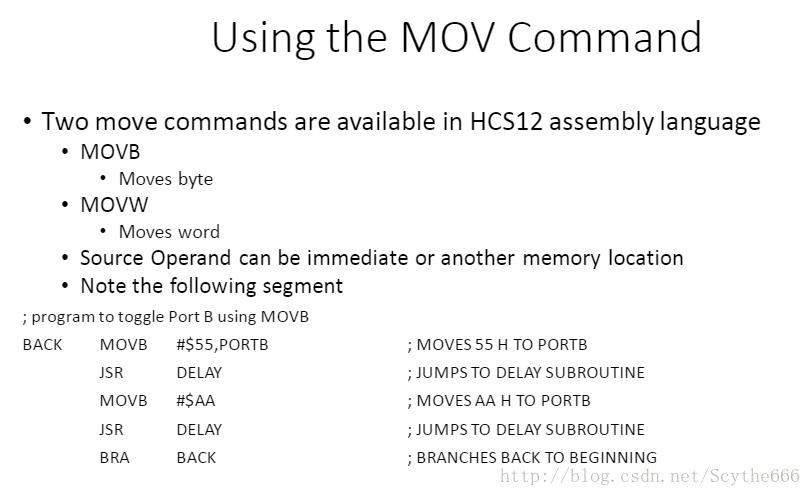

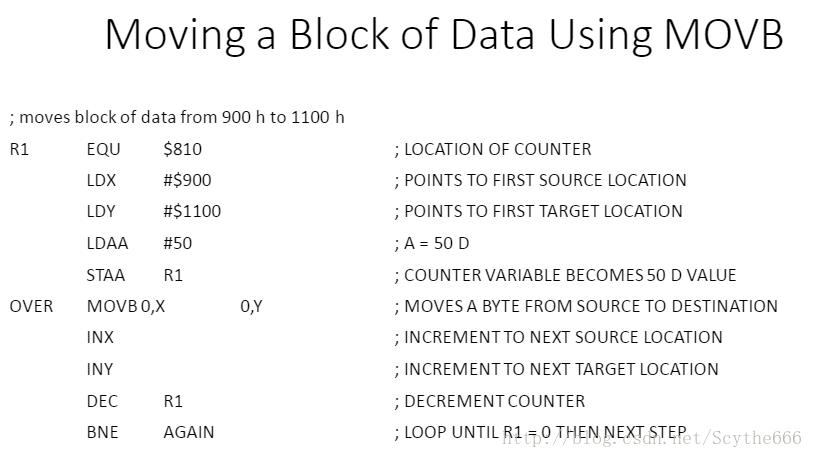

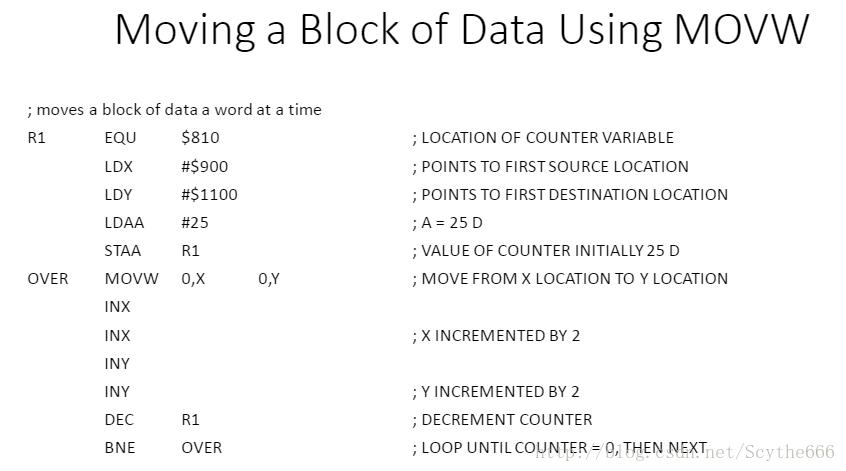

2、Using the MOV Command

MOVB Can Replace Combination of LDAA and STAA

四、Chapter 4 HCS12/9S12 I/O PORT PROGRAMMING

4-1

1、Objectives

2、I/O Ports and their functions

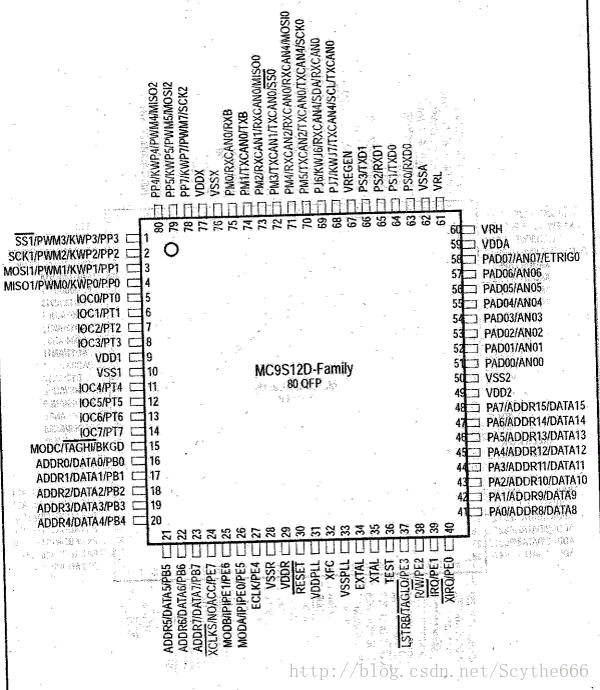

QFP = Quad Flat Package

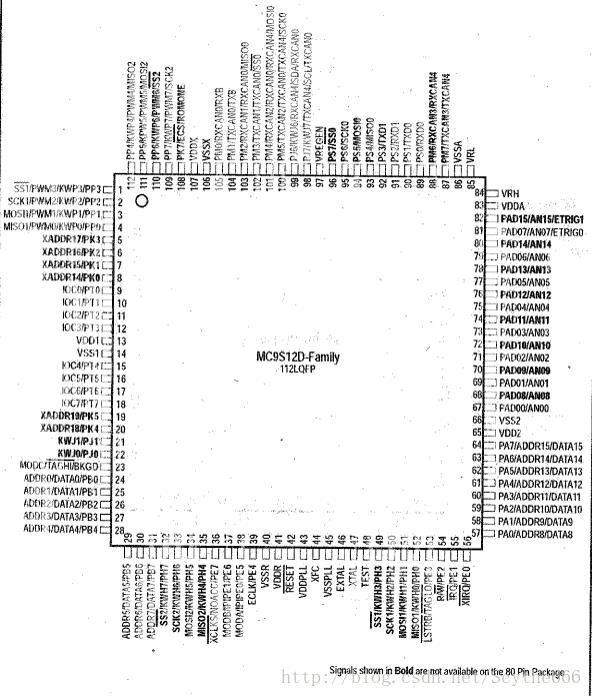

**3、(重要)Ports in the MC9S12D Family

4、DDR Register and its role in outputting and inputting data

Many of the ports in the 9S12 may be used for either input or output

- DDR register contents determine the Port function at a given point in the program

Writing all 1’s to DDRx configures the Port as an output port and we can subsequently write to the Port itsef

Conversely, writing all 0’s to DDRx configures the Port as an input and we may subsequently read from it.

All ports are configured as input after reset

; code segment to toggle PORTB

LDAA #$FF ; A IS ALL ONES

STAA DDRB ; CONFIGURES PORT B AS OUTPUT

L1 LDAA #$55 ; A = 55 H

STAA PORTB ; PORT B IS 0101 0101 B

;NOTE THAT COMPLEMENT OF 0101 0101 IS 1010 1010 B OR AA H

JSR DELAY ; ZZZZ

LDAA #$AA ; A = AA H

STAA PORTB ; PORT B IS TOGGLED

JSR DELAY ; ZZZZ

BRA L1; HERE IS ANOTHER WAY TO SKIN THE TOGGLE PORTB CODE

MOVB #$FF,DDRB ; CONFIGURE AS OUTPUT

L1 MOVB #$55,PORTB ; OUTPUT TO PORTB

JSR DELAY ; ZZZZ

MOVB #$AA,PORTB ; OUTPUT COMPLIMENT OF 55 H TO PORTB

JSR DELAY ; ZZZZ

BRA L1 ; TRY IT AGAIN FROM THE TOP

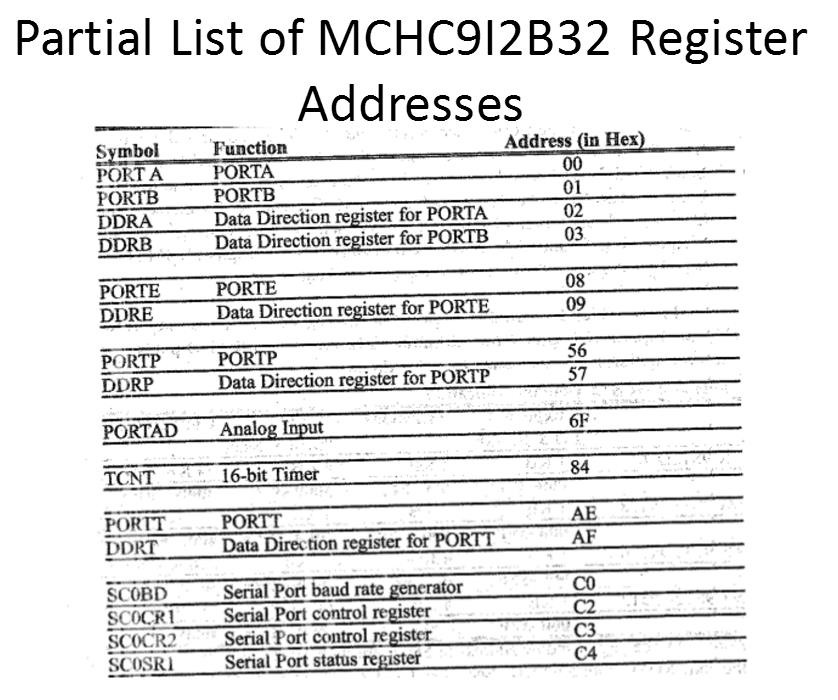

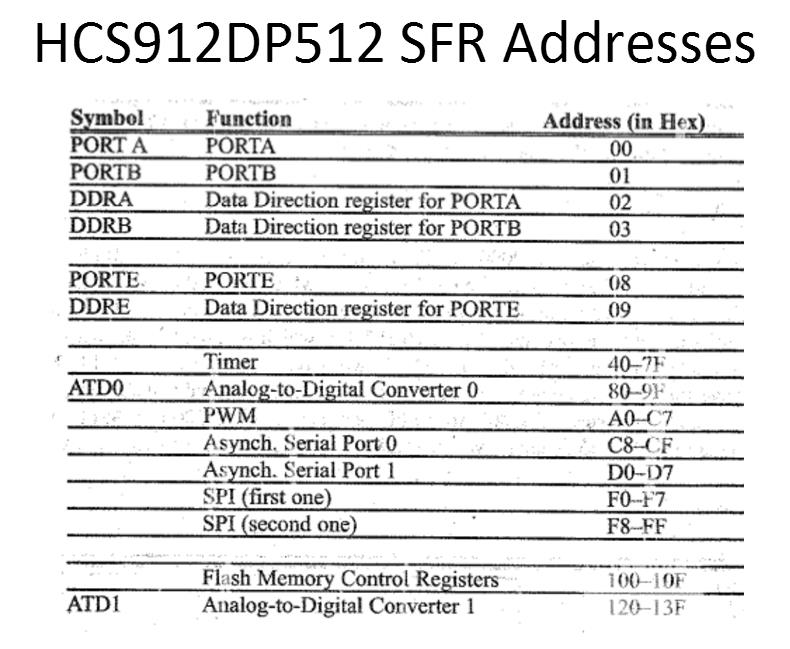

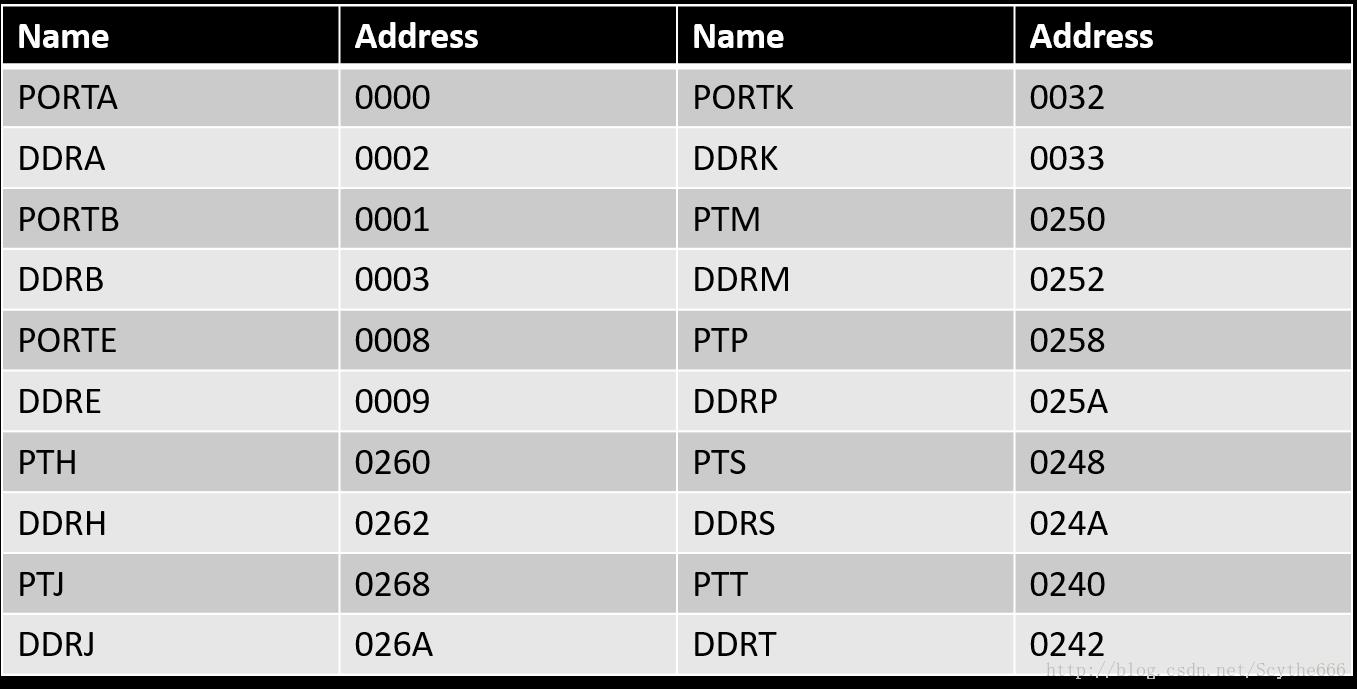

5、Register Addresses for MC9S12DP512 Ports

; PROGRAM TO READ PTH, OPERATE ON IT, THEN STORE RESULT IN PORTB

MOVB #$FF,DDRB ;PORT B IS OUTPUT

MOVB #00,DDRH ;PORT H IS INPUT

L2 LDAA PTH ; READ FROM PORT H

ADDA #5 ; OPERATE ON IT

STAA PORTB ; RESULT IN PORTB

BRA L2 ; INFINITE LOOP

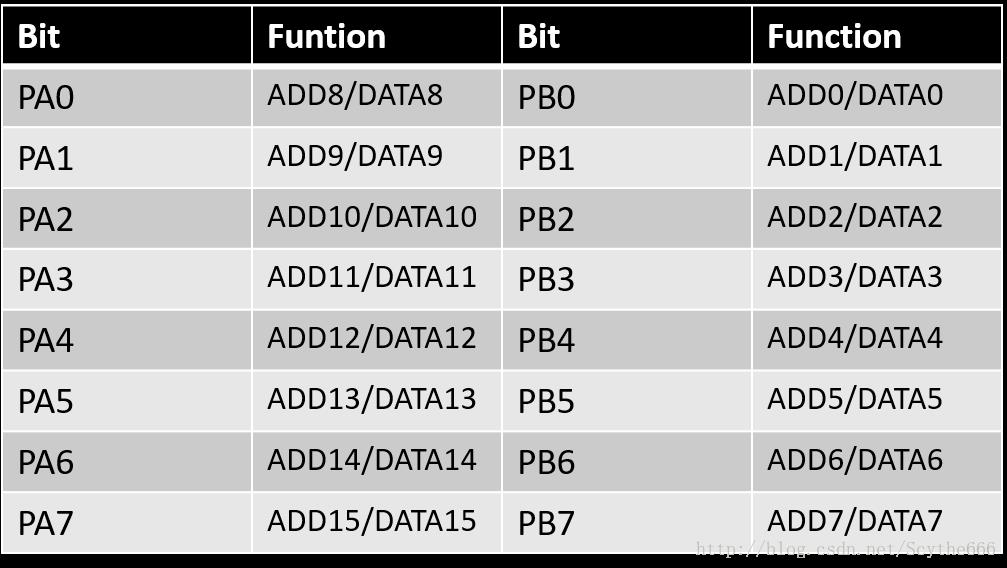

6、Dual Role of Ports A and B

In expanded mode(直接访问内存地址) the HCS12 uses Port A and Port B for address/data multiplexing allowing connection to external RAM and ROM

7、ERRATA

Port E, and Ports H thru T also have alternative functions and uses in expanded mode.

Analog to digital converter Pins

Depending on the package either 1 or 2, 8 channel ADC’s are available, (122 pin LQFP 2 are available)

We can use the ADC pins for I/O if not used by ADC

4-2 I/O BIT MANIPULATION

1、Bit addressability of I/O Ports(单bit寻址)

Some times it is convenient to access individual bits of Ports and RAM addresses

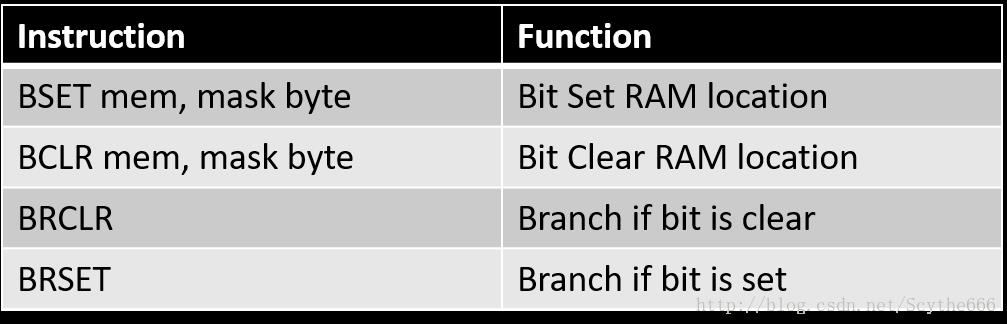

BSET & BCLR

; PROGRAM TO TOGGLE PB2 AND PB0

BSET DDRB,%00000101 ; THIS MAKES PB2 AN PB0 OUTPUT PINS

AGAIN BSET PORTB,%00000101 ; PB2 AND PB0 ARE HIGH

JSR DELAY ; ZZZZ

BCLR PORTB,%00000101 ; PB2 AND PB0 ARE LOW

JSR DELAY ; ZZZZ

BRA AGAIN ; INFINITE LOOP

2、DUTY CYCLE SQUARE WAVE

; PROGRAM TO CREATE A 50% DUTY CYCLE SQUARE WAVE ON PORTA BIT 0

BSET DDRA,%00000001 ; BIT ZERO IS OUTPUT

HERE BSET PORTA,%00000001 ; PA0 IS HIGH

JSR DELAY ; ZZZZ

BCLR PORTA,%00000001 ; PA0 IS LOW

JSR DELAY ; ZZZZ

BRA HERE ; INFINITE LOOP

; PROGRAM TO CREATE A 66% DUTY CYCLE SQUARE WAVE ON BIT 4 OF PORT A

BSET DDRA,$04 ; DDRA BIT 4 IS OUTPUT

BACK BSET PORTA,$04 ; BIT 4 IS HIGH

JSR DELAY ; ONE RINGY DINGY

JSR DELAY ; TWO RINGY DINGIES

BCLR PORTA,$04 ; BIT 4 IS LOW

JSR DELAY ; ONE DELAY

BRA BACK ; INFINITE LOOP

3、

; PROGRAM TO MONITOR PB2 BIT UNTIL IS BECOMES HIGH THEN WRITE A VALUE TO

; PORT A THEN SEND A HIGH TO LOW PULSE TO PE3

BCLR DDRB,%0000100 ; PB2 IS INTPUT

LDAA #$FF ; VALUE OF A IS FF H

STAA DDRA ; A IS OUTPUT

LDAA #$45 ; VALUE OF A IS 45 H

AGAIN BRSET PORTB,%00000100,OVER ; BRANCH TO OVER IF PB2 IS HIGH

BRA AGAIN ; LOOP UNTIL, MYSTERIOUSLY, PB2

; IS LOW

OVER STAA PORTA ; WRITING 45 H TO PORT A

BSET PORTE,%00001000 ; PE3 IS HIGH

BCLR PORTE,%00001000 ; PE3 IS LOW; ANOTHER WAY TO ACCOMPLISH THE PREVIOUS EXAMPLE USING BRCLR

; INSTRUCTION

BCLR DDRB,%00000100 ; PB2 IS INPUT

LDAA #$FF ; A = FF H

STAA DDRA ; PORT A IS OUTPUT

BSET DDRE,%00001000 ; PE3 IS OUTPUT

LDAA #$45 ; A = 45 H

AGAIN BRCLR PORTB,%00000100,AGAIN ; CHECK IF PB2 IS LOW, IF SO BRANCH

; TO AGAIN

STAA PORTA ; ELSE WRITE PORT A

BSET PORTE,%00001000 ; PE3 IS HIGH

BCLR PORTE,%00001000 ; PE3 IS LOW3、monitor

; THINK ABOUT THE APPLICATION OF ALARM MONITORING. WE COULD USE PB3 AS

; THE BIT THAT MONITORS THIS CONDITION, AND FURTHER ASSUME THAT IT IS

; PULLED LOW WHEN THE DOOR IS OPEN, IT IS A REQUIREMENT TO SEND A HIGH TO

; LOW PULSE TO PE5 TO TURN ON A BUZZER

BCLR DDRB,%00001000 ; PB3 IS INPUT

BSET DDRE,%00100000 ; PE5 IS OUTPUT

HERE BRSET PORTB,%00001000,HERE ; BRANCH IF PB3 IS HIGH TO HERE

BSET PORTE,%00100000 ; PE5 IS HIGH

BCLR PORTE,%00100000 ; PE5 IS LOW

附加:

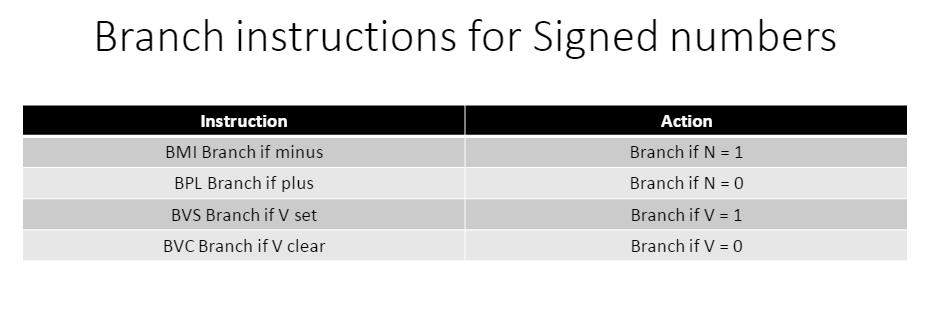

1、Branch instructions for Signed numbers

2、Show how the cpu would subtract $05 from $43.

这个时候需要考虑到补码,43H-05H=3EH,也就是0100 0011 - 0000 0101,这个时候减去这个数相当于加上这个数的反码,0100 0011 + 1111 1011 = 0011 1110

五、Chapter 5 Arithmetic, Logic Instructions and Programs

5-1

1、Learning Objectives

Upon completion, Students will be able to:

Define the range of numbers in HCS12 for unsigned data

Code addition and subtraction of numbers for unsigned numbers

Perform addition of BCD data

Code HCS12 multiplication a division of unsigned numbers

Code HCS12 logic instructions: AND, OR, and EX-OR

Code HCS12 assembly instructions for bit shift and rotate

Use HCS12 logic instructions for bit manipulation

Use Compare for program control

Code HCS12 rotate instructions and data serialization

Explain BCD system of data representation

Contrast and compare packed and unpacked BCD data

Code HCS12 programs for ASCII and BCD data conversion

Define the range of numbers possible in HCS12 for signed data

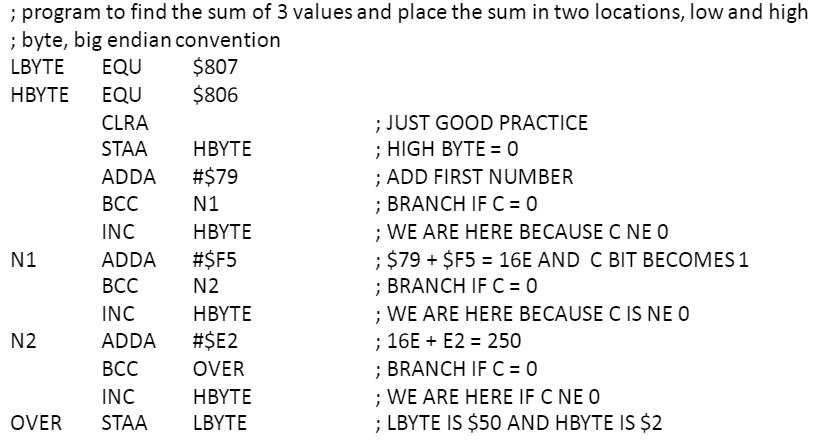

2、Example using ADCA(带carry的加)

; Program to add two 16 bit numbers using ADCA instruction. The numbers are 3CE7

; H and 3B8D H. Assume big endian convention, and 3B8D are stored in locations 807

; and 806. The result is stored in locations 808 and 809

LDAA #$E7 ; A = VALUE OF FIRST NUMBER LOW BYTE

ADDA $807 ; LOCATION OF NEXT LOW BYTE

; E7 + 8D = 174 AND C = 1

STAA $809 ; STORE ACCORDING TO CONVENTION

LDAA #$3C ; A = VALUE OF FIRST NUMBER HIGH BYTE

ADCA $806 ; A = A + VALUE OF NEXT HIGH BYTE + 1

STAA $808 ; STORE RESULTANT HIGH BYTE BIG ENDIAN

3、Adding Multi-Byte Numbers

; Program to add two multi-byte numbers

MYCOUNT EQU $800 ; ADDRESS OF COUNTER VARIABLE

LDAA #4 ; A = 4 D

STAA MYCOUNT ; VALUE OF MYCOUNT IS 4 D

CLRA ; A = 0

LDX #$813 ; X POINTER

LDY #$853 ; Y POINTER

CLC ; CLEAR CARRY FLAG

BACK LDAA 0,X ; LOAD BYTE AT POINTED ADDRESS

ADCA 0,Y ; ADD BYTE AT POINTED ADDRESS

STAA 0,Y ; STORE WITH CARRY

DEX ; DECREMENT POINTER X

DEY ; DECREMENT POINTER Y

DEC MYCOUNT ; DECREMENT LOOP COUNTER

BNE BACK ; BRANCH IF COUNTER NE 0

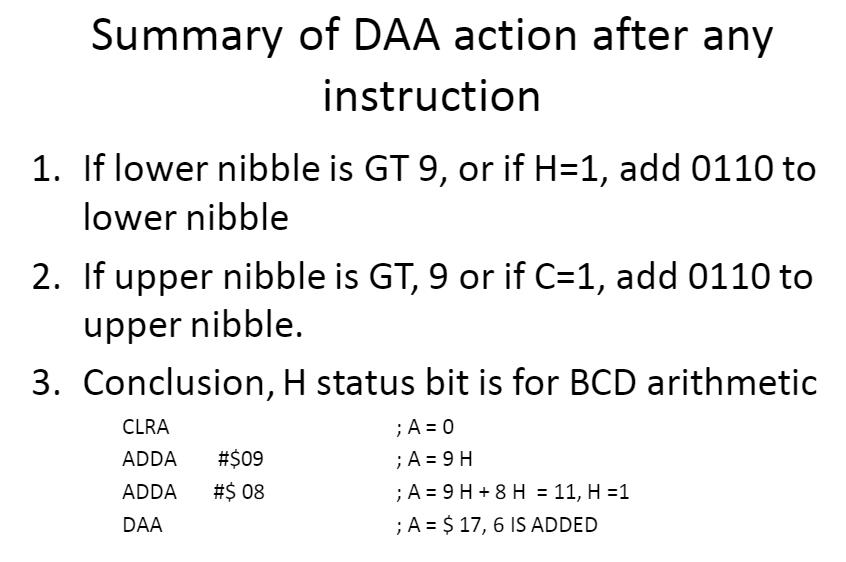

4、DAA Instruction

DAA stands for Decimal Adjust Accuumulator

- Only works with A register

- Adds 6 to lower nibble and higher nibble if necessary, otherwise no effect

Consider the following

LDAA #$47 ; A = $47

ADDA #$25 ; A = A + 25 H RESULT IS 6C H

DAA ; ADUST FOR BCD ADDITION, RESULT IS 72 H

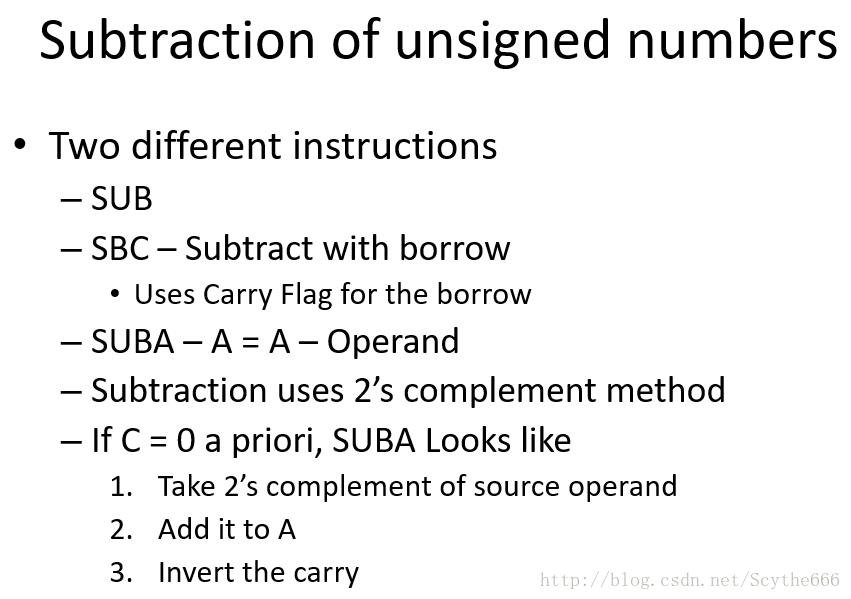

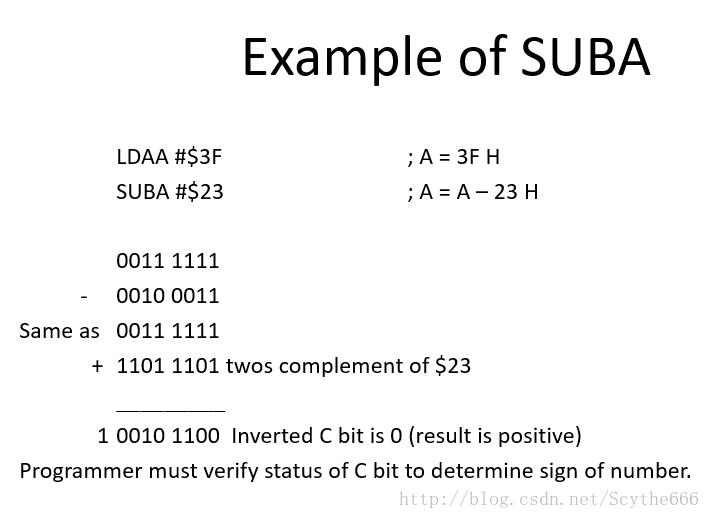

5、Subtraction of unsigned numbers

6、Neg Instruction

- After execution of SUBA, if C = 0 the result is positive

If C = 1, the result is negative - Destination has 2’s complement of result

- NEG (negate) may be used to change this

- NEG performs 2’s complement

; Program to subtract 6E H from 4C H

MYREG EQU $820 ; LOCATION OF NUMBER TO BE SUBTRACTED

LDAA #$6E ; A = 6E H

STAA MYREG ; STORE 6E H AT LOCATION 820 H

LDDA #$4C ; A = 4C H

SUBA MYREG ; A = (4C-6E) = DE, INVERTED C = 1

BCC NEXT ; IF C = 0 BRANCH TO NEXT TARGET

NEGA ; TAKE 2’S COMPLEMENT OF A

NEXT STAA MYREG ; RESULT IS STORED IN MYREG

; 6E = 01101110 2’S COMPLIMENT OF THIS IS 1001 0010

; AFTER THE SUBA COMMAND C =1 AND THE RESULT IS NEGATIVE WE DO NOT

; BRANCH AND 2’S COMPLEMENT IS TAKEN AND MYREG = 22 H MAGNITUDE OF

; NEGATIVE RESULT

7、SBCA SUBTRACT WITH BORROW

- Used for multi-byte numbers

- Handles borrow of lower byte

- C flag holds borrow

- If C = 1 prior to execution, 1 is subtracted from result

; Program to subtract 2 16 bit numbers eg $2762 - $1296 assuming location 806 H

; stores 12 H and location 807 H stores 96 H, store result in same locations with big

; endian convention. We are looking for the result of 14CC

LDAA #$62 ; LOAD LOW BYTE

SUBA $807 ; A = 62 H – 96 H = CC H, C = BORROW = 1

STAA $807 ; STORE LOW BYTE

LDAA #$27 ; LOAD HIGH BYTE

SBCA $806 ; A = 27 – 12 – 1 = 14 H

STAA $806 ; STORE HIGH BYTE

; Since these are 16 bit or 2 byte numbers, we could us the instruction SUBD

LDD #2762 ; LOAD D REGISTER

SUBD $806 ; SUBTRACT THE VALUES AT $806 AND $807

STDD $806 ; STORE RESULT

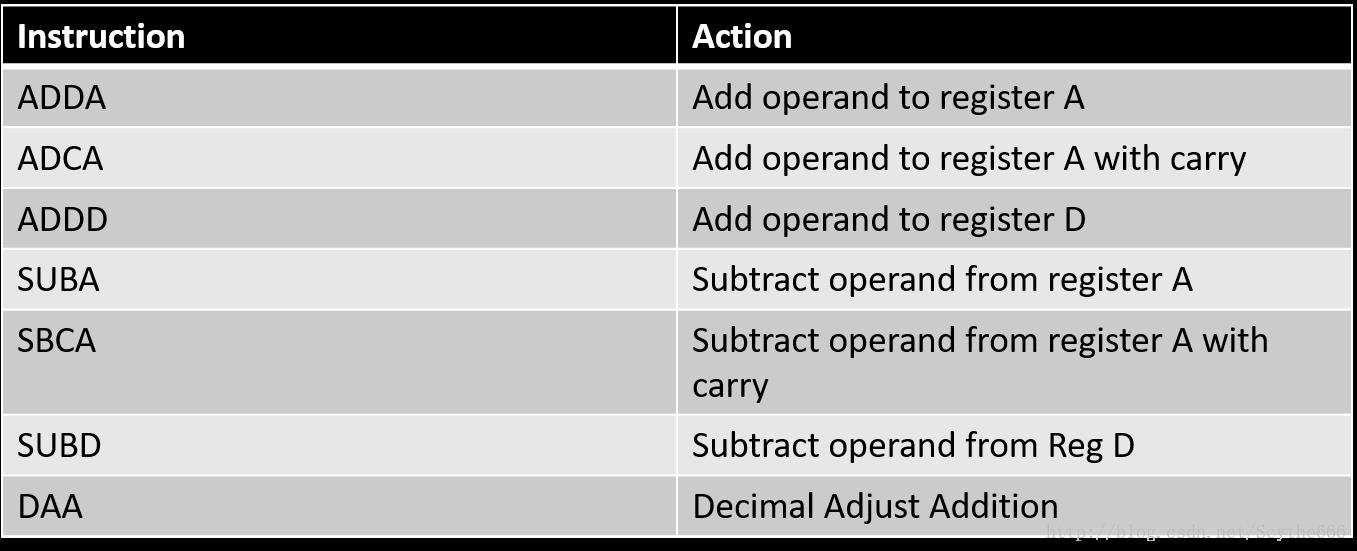

**8、(重要)Some Widely Used Arithmetic Instructions

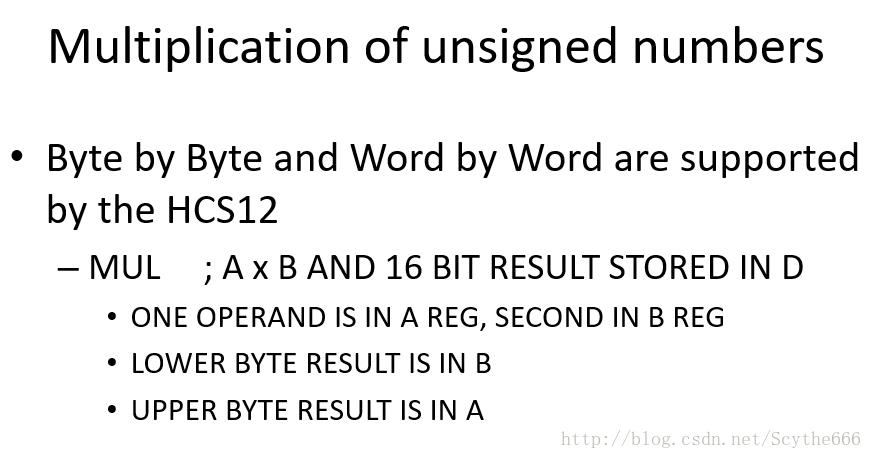

9、Multiplication of unsigned numbers

; Multiply 25 H by 65 H

LDAA #$25 ; FIRST OPERAND IN A

LDAB #$65 ; SECOND OPERAND IN B

MUL ; 25 H x 65 H = E99 H IN REG D

; A = 0E H, B = 99 H

;

; 16 bit multiplication

LDD #500 ; D = 500 DECIMAL

LDY #700 ; Y = 700 DECIMAL

EMUL ; 500 x 700 = 350000 = 55730 H

; Y = 0005 H, D = 5730 H

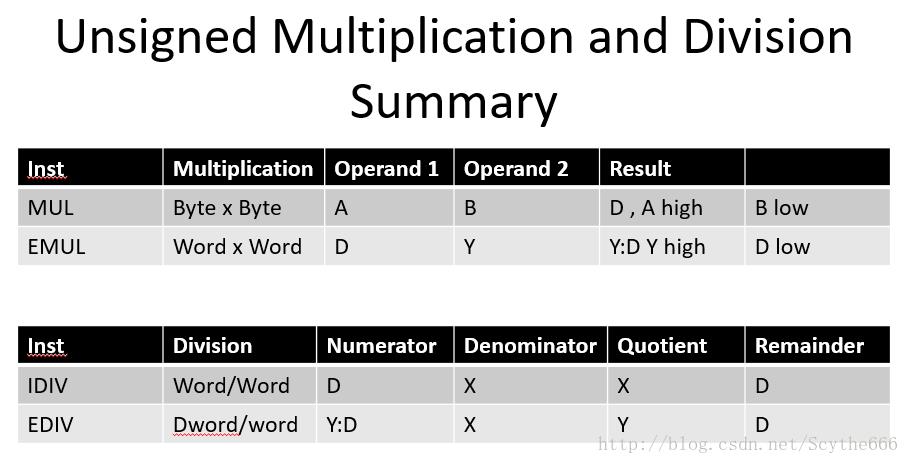

10、Unsigned Multiplication and Division Summary

11、Unsigned Division

; divide 255 decimal by 10 decimal

LDD #255 ; D = 255 DECIMAL

LDX #10 ; X = 10 DECIMAL

IDIV ; 255/10 = 25 REMAINDER 5

` ; X = 25 DECIMAL AND D = 5

;

; divide 90FF24 H by 1000 decimal

;

LDD #$FF24 ; LOWER WORD

LDY #$90 ; UPPER WORD

; 90FF24 H = 9502500 DECIMAL

LDX #1000 ; X = 1000 DECIMAL

EDIV ; Y:D/X = 9502 (251E H) REMAINDER 500 (1F4)

Division Application Example ADC

; ADC provides Hex data between 00 and FF H. Conversion to decimal is accomplished

; by dividing by 10 repetitively and saving remainder. This program converts FD H to

; decimal with byte by byte division using locations 822 – 824 H to store results where 824