Verilog学习笔记简单功能实现...............计数分频电路

Posted SYoong

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog学习笔记简单功能实现...............计数分频电路相关的知识,希望对你有一定的参考价值。

在分频器电路中最重要的概念有两个;1)奇分频/偶分频;2)占空比。

A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为

1 module half_clk(clr,clk_in,clk_out,out2); 2 input clr,clk_in; 3 output clk_out,out2; 4 reg clk_out,out2; 5 6 always @(posedge clk_in) 7 begin 8 if (clr==0) begin clk_out=0; out2=1;end 9 else begin clk_out<=~clk_out; out2=~out2;end 10 end 11 endmodule

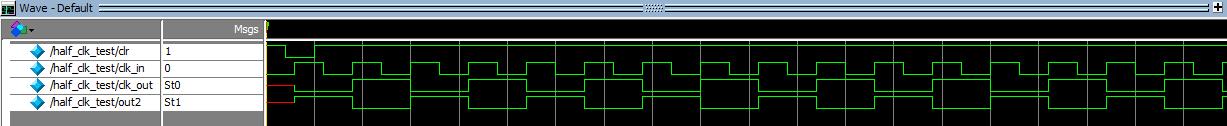

波形图如下所示:

B)采用计数器实现计数分频(偶数)占空比为50%,如实现40分频,程序如下:

1 module fdivision(rst,clkin,clkout); 2 input rst,clkin; 3 output clkout; 4 reg clkout; 5 reg [4:0]i; 6 always @(posedge clkin) 7 begin 8 if(!rst) begin clkout<=0; i<=0;end 9 else begin 10 if(i==19) 11 begin clkout<=~clkout;i<=0;end 12 else 13 i<=i+1; 14 end 15 end 16 endmodule

波形图:

C)采用相与/相或的方式实现奇分频,以及占空比可调分频器;如5分频,占空比分别为50%,40%

1 module fdivision5(clkin,clkout); 2 input clkin; 3 output clkout; 4 wire clkout; 5 reg [2:0]step,step1; 6 always @(posedge clkin) 7 begin 8 case(step) 9 3\'b000:step<=3\'b010; 10 3\'b010:step<=3\'b100; 11 3\'b100:step<=3\'b001; 12 3\'b001:step<=3\'b011; 13 3\'b011:step<=3\'b000; 14 default step<=3\'b000; 15 endcase 16 end 17 always @(negedge clkin) 18 begin 19 case(step1) 20 3\'b000:step1<=3\'b010; 21 3\'b010:step1<=3\'b100; 22 3\'b100:step1<=3\'b001; 23 3\'b001:step1<=3\'b011; 24 3\'b011:step1<=3\'b000; 25 default step1<=3\'b000; 26 endcase 27 end 28 assign clkout=(step[0]|step1[0]); 29 endmodule

顶层文件(testbench):

1 `timescale 1ns/1ns 2 `define half_period 20 3 module fdivision5_test; 4 reg clkin; 5 wire clkout; 6 wire step,step1; 7 initial 8 begin 9 clkin=0; 10 end 11 always #`half_period clkin=~clkin; 12 fdivision5 m(clkin,clkout); 13 assign step=m.step; 14 assign step1=m.step1; 15 endmodule

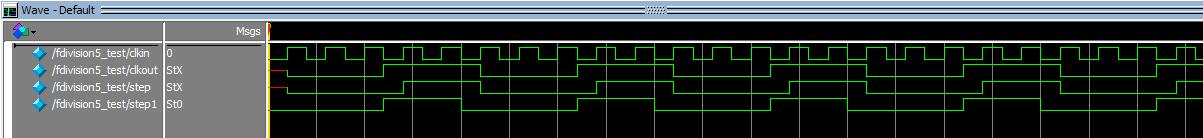

波形图:

也可以采用两个计数器分别对上升沿和下降沿进行计数来实现奇分频:

module div5(clkin,clkout,rst); input clkin,rst; output clkout; parameter N=5; wire clk1,clk2; reg [2:0]cnt1,cnt2; always @(posedge clkin or negedge rst) if (!rst) cnt1<=0; else if(cnt1<(N-1)) cnt1<=cnt1+1; else cnt1<=0; always @(negedge clkin or negedge rst) if (!rst) cnt2<=0; else if(cnt2<(N-1)) cnt2<=cnt2+1; else cnt2<=0; assign clk1=(cnt1<=((N-1)/2))?1\'b1:1\'b0; assign clk2=(cnt2<=((N-1)/2))?1\'b1:1\'b0; assign clkout=clk1&clk2; endmodule

其testbench为:

`timescale 10ns/1ns `define period 2 module div5_test; reg clkin,rst; wire clkout; wire clk1,clk2; initial begin clkin=0; rst=1; #5 rst=0; #55 rst=1; end always #`period clkin=~clkin; assign clk1=m.clk1; assign clk2=m.clk2; div5 m(clkin,clkout,rst); endmodule

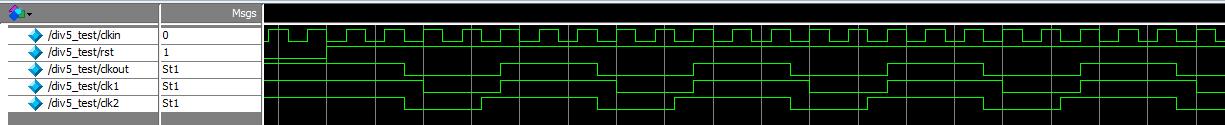

波形图为:

以上是关于Verilog学习笔记简单功能实现...............计数分频电路的主要内容,如果未能解决你的问题,请参考以下文章