Verilog 测试文件怎么写

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog 测试文件怎么写相关的知识,希望对你有一定的参考价值。

不太懂,比如四位全加器,代码如下

module add4bit(a,b,ci,y,co);

input [3:0]a,b;

input ci;

output [3:0]y;

output co;

assign co,y=a+b+ci;

endmodule

那么测试文件我该如何写?最好能标上每一部分的代表什么

// Inputs

reg [3:0] a,b;

reg ci;

// Outputs

wire [3:0] y;

wire co;

// Instantiate the Unit Under Test (UUT)

add4bit uut (

.a(a),

.b(b),

.ci(ci),

.co(co),

.y(y)

);

initial begin

// Initialize Inputs

a= 0;

b= 0;

ci= 0;

// Wait 100 ns for global reset to finish

#100;

a = 3;

b=4;

ci =0;

end

endmodule

如上就是测试3+4,进位为0时的输出。测试的步骤网上看看吧,各个软件不一样。追问

我用的是ise14.7,- -能说下每部分是什么意思嘛- -我看不懂

verilog怎么编写可调PWM波形?

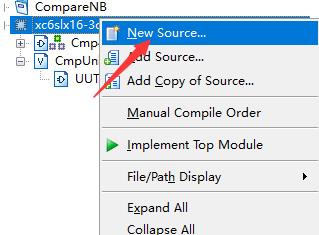

参考技术A首先,在项目上右键,点击New Source创建新的代码文件。

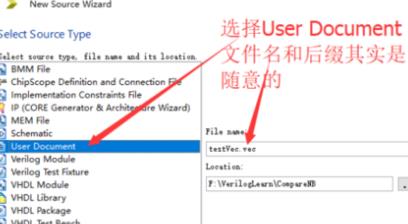

选择User Document创建自定义的文本文件。文件名和后缀都随意了。该文件用来存放仿真需要的数据,与项目本身并无关联。

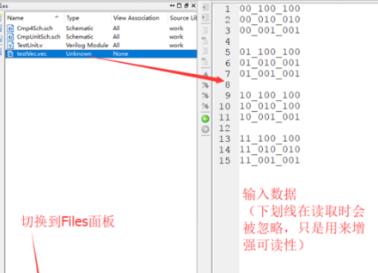

创建好后,在下方切换到Files面板,双击打开该文件

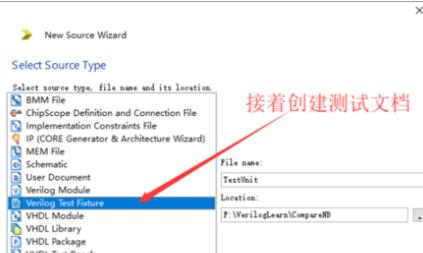

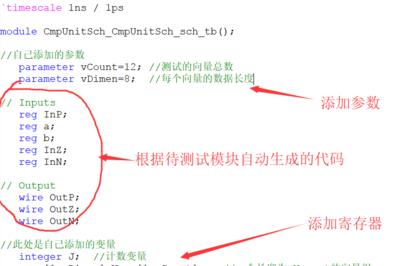

数据文件写好后,就要编写Verilog测试模块读取该文件并对模块进行测试了。在项目上右键,点击New Source,接着选择Verilog Test Fixture,输入文件名并继续,选择待测模块,接着创建文件。

双击打开该文件,看到待测试模块输入对应了一些reg寄存器类型,输出部分对应了一些wire类型。添加两个parameter常量,接着添加计数变量J用于for循环,添加一个向量数组用于存放文件读取的数据。

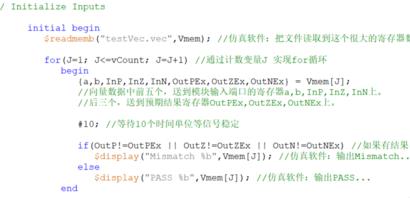

其中$readmemb函数从文件读取数据到Vmem数组。$display可以在仿真软件中输出文字。#10表示等待10个时间单位,等"信号稳定"

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。

语言要素:Verilog的设计初衷是成为一种基本语法与C语言相近的硬件描述语言。这是因为C语言在Verilog设计之初,已经在许多领域得到广泛应用,C语言的许多语言要素已经被许多人习惯。一种与C语言相似的硬件描述语言,可以让电路设计人员更容易学习和接受。不过,Verilog与C语言还是存在许多差别。

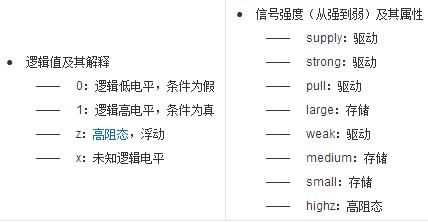

数据类型:四值逻辑

以上是关于Verilog 测试文件怎么写的主要内容,如果未能解决你的问题,请参考以下文章