[FPGA] DP83848網路晶片開發心得

Posted 程式設計天地

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了[FPGA] DP83848網路晶片開發心得相关的知识,希望对你有一定的参考价值。

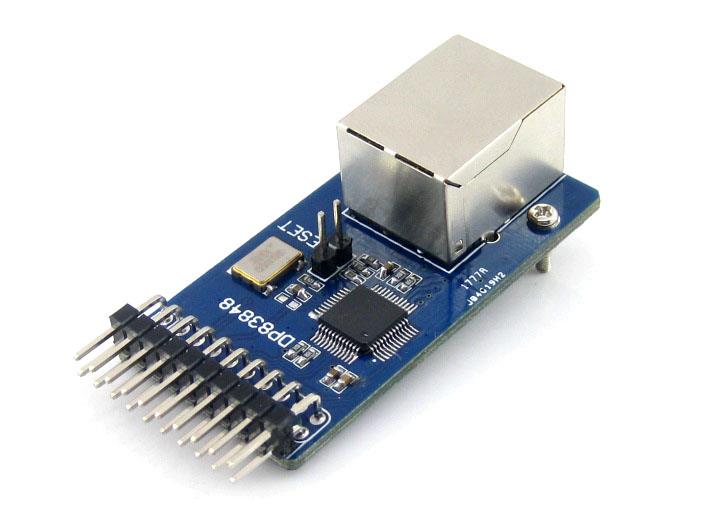

最近想要用FPGA來存取網路,於是想到之前買的一個DP88848晶片的網路版子,剛好拿出來研究研究。

查了一下規格它是使用RMII的傳輸介面可以達到10M/100M的速度,應該很夠用了吧。

那第一步就是先研究一下這電路要怎麼接?剛好有在網路找到其電路圖?

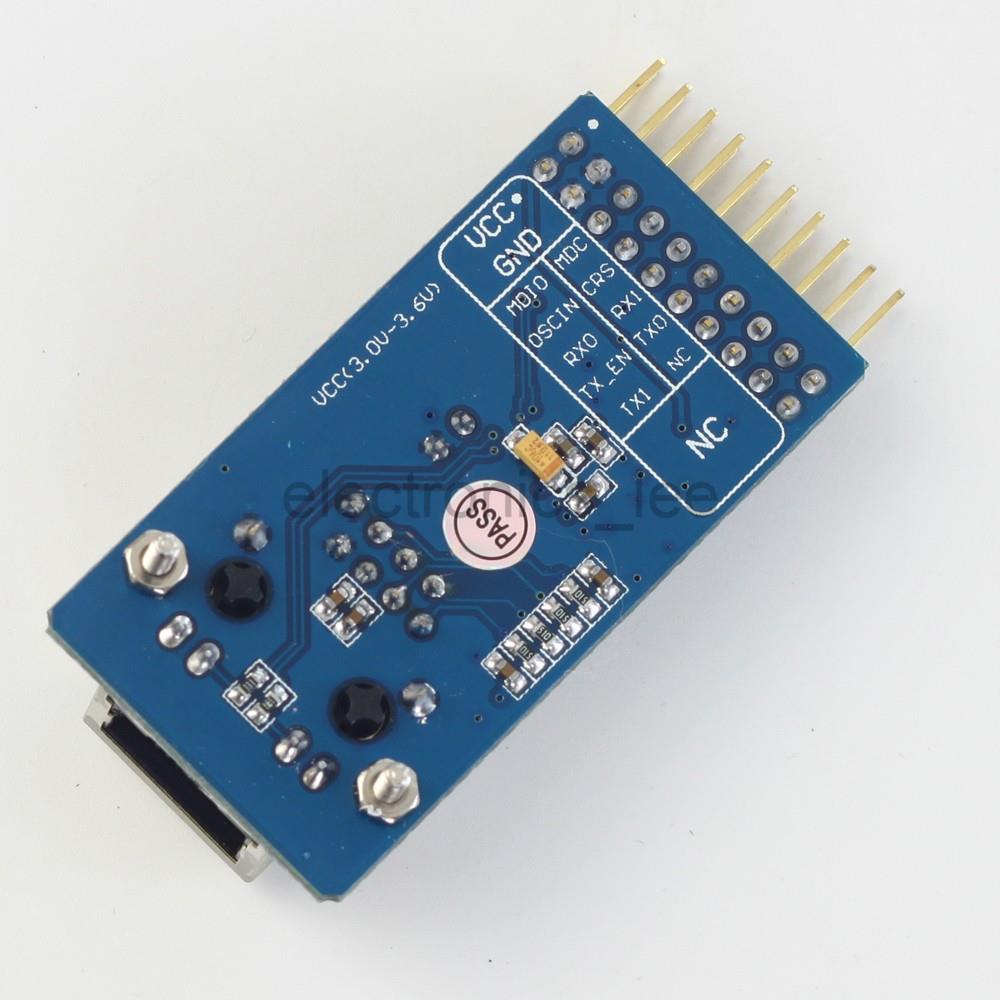

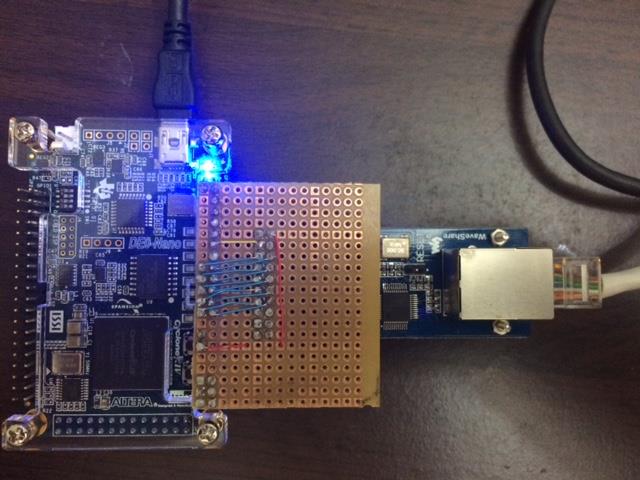

買了 一個洞洞板,接到DE0-Nano的GPIO_0,腳位如下:

pin discrption

GPIO_0[10]: MDC GPIO_0[11]: MDIO

GPIO_0[12]: CRS GPIO_0[13]: OSCIN

GPIO_0[14]: RX1 GPIO_0[15]: RX0

GPIO_0[16]: TX0 GPIO_0[17]: TX_EN

GPIO_0[18]: NC GPIO_0[19]: TX1

腳位連接焊完後,外部電路就差不多就大功告成。

=============================================

接下來就要開始寫verilog程式了,要先從哪裡開始呢?

我想還是要加一顆Nio處理器來處理封包,訊號傳輸還是用verilog來控制會比較快,那就先從MAC(Media Access Controller)開始吧。

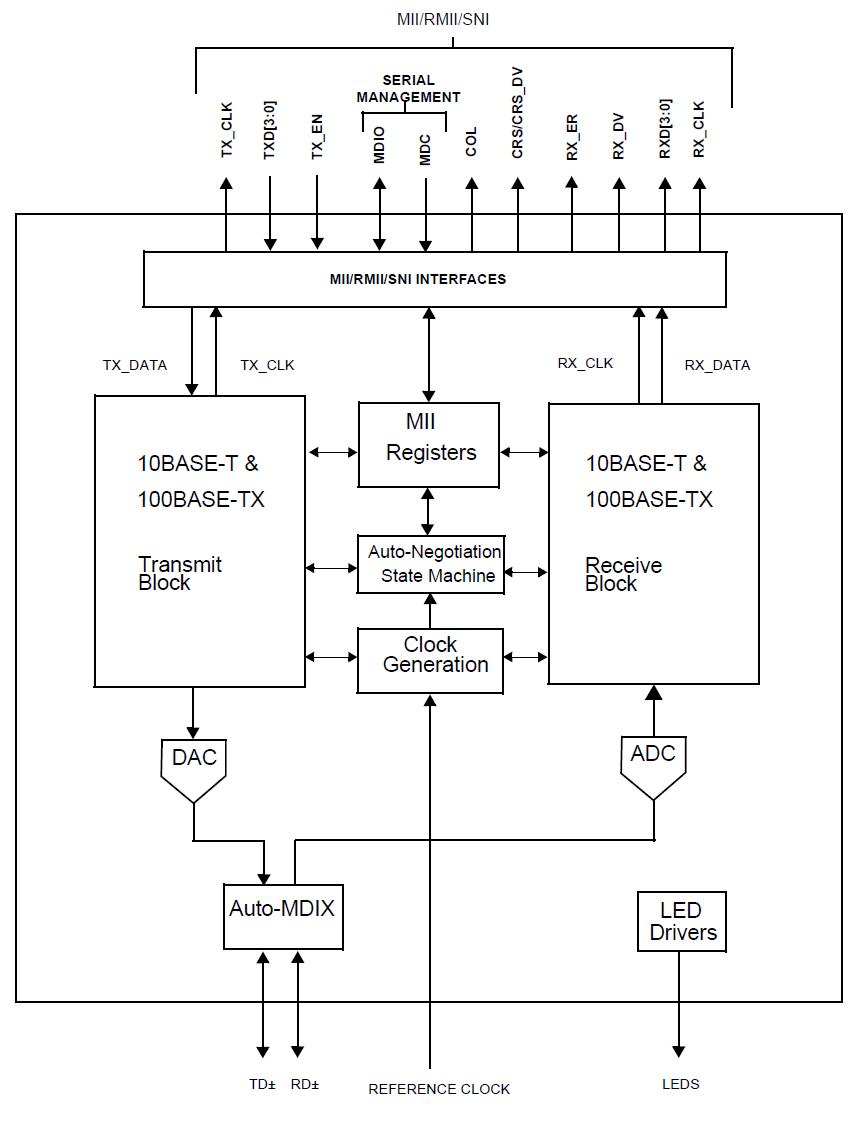

由下面的系統圖可以得知要控制這顆dp83848網路晶片,需先設定MII register。

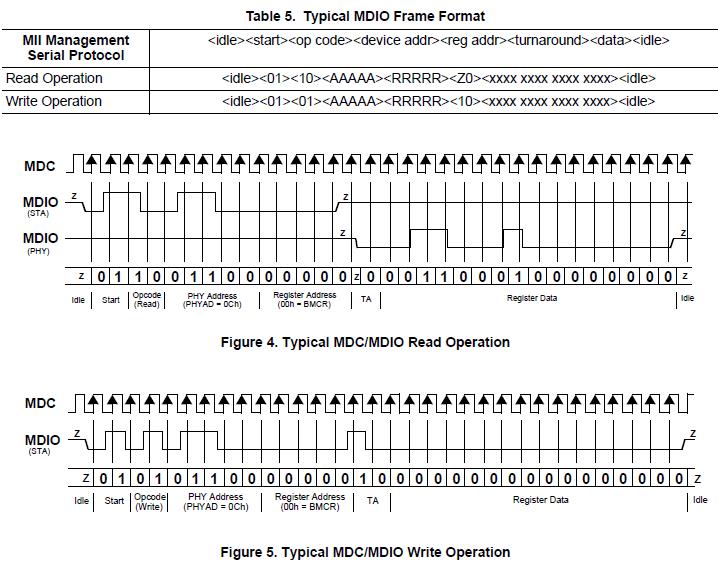

要設定MII register必須要先寫一個串列傳輸程式來讀寫MDIO及MDC,其中MDIO是雙向資料線,而MDC是時脈訊號,最大時脈可以到25Mhz。

查了一下MDC與MDIO的傳輸協定,如下圖所示,此時就開始來寫一個傳輸程式來控制。

以下這是我的程式IO介面。

1 // SMI Test 2 SMI_top SMI_top( 3 // clock reset interface 4 .iClk_50M(CLOCK_50), // 50Mhz clock 5 .iRst_n(1), // reset negativite 6 7 // SDI interface 8 .iReg_Addr(5\'h00), // register address 9 .iTXData(16\'ha), // transmit data 10 .iCMD_Trig(rCnt[9]), // command trigger valid 11 .oRXData(GPIO_1[15:0]), // receive data 12 .iRWn(1), 13 .oFinish(GPIO_1[16]), // trigger, when send or receive a rxdata finish 14 .oBusy(GPIO_1[17]), // busy to MD operation 15 16 // dp83848 rmii signal 17 .oMDC(oMDC), // management data clock 18 .MDIO(MDIO) // management data I/O 19 );

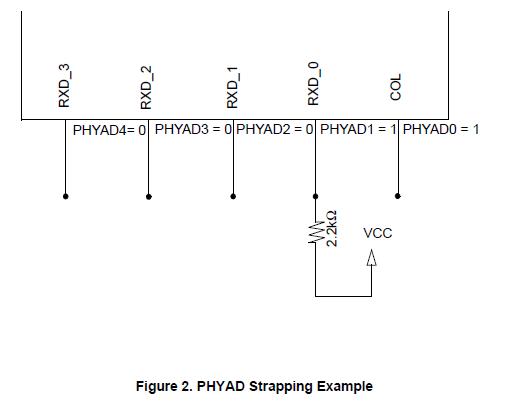

這裡面設計重點在於PHY_ADDRESS,一開始照著spec波形圖設計PHY_ADDRESS設0x0C,送訊號結果MAC連動都不動。

後來查了一下規格書說可以用外部電路來設定PHY_ADDRESS的位址,就看了一下電路發現PHY_ADDRESS要設成0x07才會動。

終於可以讓程式順利動起來了,可以讀到暫存器0的資料了。

今天就先寫到這邊吧。下篇再繼續介紹如何擷取RXD資料。

======================================================================================

reference

1. DP83848-Ethernet-Board-Schematic.pdf

2. DP83848C PHYTER® - Commercial Temperature Single Port 10/100 Mb/s Ethernet Physical Layer Transceiver

以上是关于[FPGA] DP83848網路晶片開發心得的主要内容,如果未能解决你的问题,请参考以下文章