静态时序分析(static timing analysis) --- 时序路径

Posted 我被忘了

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了静态时序分析(static timing analysis) --- 时序路径相关的知识,希望对你有一定的参考价值。

时序分析工具会找到且分析设计中的所有路径。每一个路径有一个起点(startpoint)和一个终点(endpoint)。起点是设计中数据被时钟沿载入的那个时间点,而终点则是数据通过了组合逻辑被另一个时间沿载入的时间点。

路径中的起点是一个时序元件的时钟pin或者设计的input port。input port可以作为起点是因为数据可以由外部源(external source)进入设计。

终点则是时序元件的数据输入pin或者设计的output port。同理output port可以作为终点是因为数据可以被外部源捕捉到。

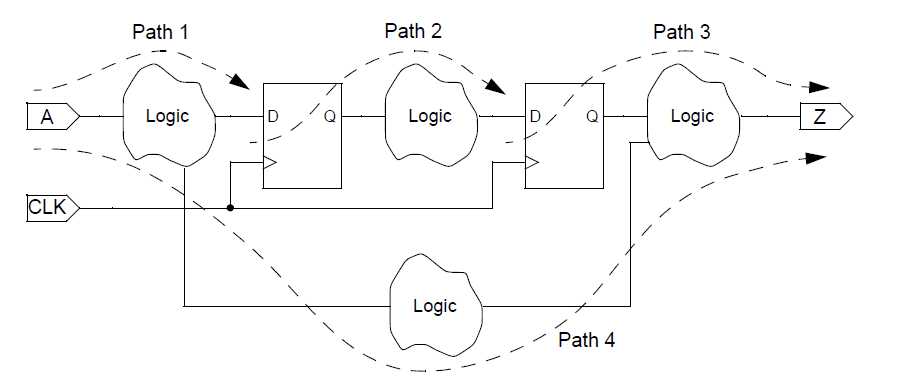

上图显示一个时序路径的例子。

path1 开始于一个input port 且结束于时序元件的数据输入端

path2 开始于时序元件的时钟pin且结束于时序元件的数据输入端

path3 开始于时序元件的时钟pin且结束在一个output port

path4 开始于input port 且结束于 output port

每一个path都有专属的slack,slack值可以是正,0或者负。某一个path拥有最坏的slack的话则称之为 critical path

critical path拥有最大的负slack值。若是所有的path都没有时序违规,则slack都是正数,此时最小的那个slack则是critical path。

复数critical paths意味着某一组的path都是critical path。

路径可以被分组(group)来得到各自的时序分析,时序报告和优化。

在IC compliler中输入report_timimg可以得到时序报告,如下所示。

Startpoint: I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_ (rising edge-triggered flip-flop clocked by SYS_2x_CLK) Endpoint: I_RISC_CORE/I_ALU/Zro_Flag_reg (rising edge-triggered flip-flop clocked by SYS_2x_CLK) Path Group: SYS_2x_CLK Path Type: max

Point Incr Path ---------------------------------------------------------------------------------- clock SYS_2x_CLK (rise edge) 0.00 0.00 clock network delay (propagated) 0.51 0.51 I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_/CP (senrq1) 0.00 0.51 r I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_/Q (senrq1) 0.62 1.13 f I_RISC_CORE/I_INSTRN_LAT/Instrn_1[27] (INSTRN_LAT) 0.00 1.13 f I_RISC_CORE/I_ALU/ALU_OP[3] (ALU) 0.00 1.13 f I_RISC_CORE/I_ALU/U288/ZN (nr03d0) 0.36 * 1.49 r I_RISC_CORE/I_ALU/U261/ZN (nd03d0) 0.94 * 2.43 f I_RISC_CORE/I_ALU/U307/ZN (invbd2) 0.35 * 2.78 r I_RISC_CORE/I_ALU/U343/Z (an02d1) 0.16 * 2.93 r I_RISC_CORE/I_ALU/U344/ZN (nr02d0) 0.11 * 3.04 f I_RISC_CORE/I_ALU/U348/ZN (nd03d0) 0.28 * 3.32 r I_RISC_CORE/I_ALU/U355/ZN (nr03d0) 0.29 * 3.60 f I_RISC_CORE/I_ALU/U38/Z (an02d1) 0.15 * 3.75 f I_RISC_CORE/I_ALU/U40/Z (an02d1) 0.12 * 3.87 f I_RISC_CORE/I_ALU/U48/ZN (nd02d1) 0.06 * 3.93 r I_RISC_CORE/I_ALU/U27/ZN (nd02d1) 0.06 * 3.99 f I_RISC_CORE/I_ALU/Zro_Flag_reg/D (secrq4) 0.00 * 3.99 f data arrival time 3.99

clock SYS_2x_CLK (rise edge) 4.00 4.00 clock network delay (propagated) 0.47 4.47 clock uncertainty -0.10 4.37 I_RISC_CORE/I_ALU/Zro_Flag_reg/CP (secrq4) 0.00 4.37 r library setup time -0.37 4.00 data required time 4.00 -------------------------------------------------------------------------------- data required time 4.00 data arrival time -3.99 ------------------------------------------------------------------------------- slack (MET) 0.01

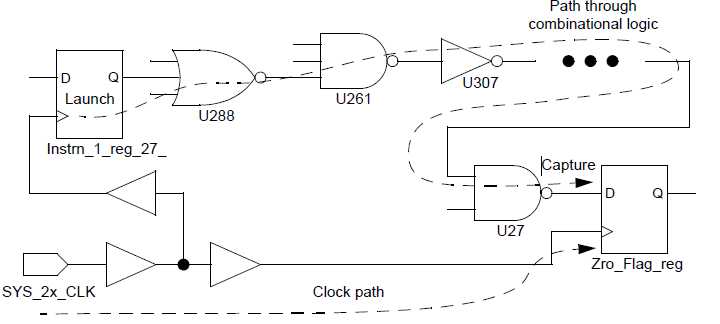

此例子的图如下:

报告开始显示了路径的起点,路径终点,路径组名和路径检测的类型。此例中,路径检测类型为max,意味着最大的延时或者setup check,若是min则是最小的延时或者hold check

下面一个大表显示了从起点到终点之间的一个个点的延时值。纵列有三个标识, Point, Incr和 Path,分别表示了路径中的各个点,此点所需要的延时和从起点一直累积到此点的延时值。

星号(*)表示了使用了SDF文件中的延时值,r和f表示 上升或者下降沿。

之前说过路径由数据载入的时钟沿开始,到device的数据输入端结束。表中的data arrival time表示了从载入时钟沿到终点数据到达所经历的时间。

再用required time减去arrival time 则得到了slack值。

例子中显示的slack非常小,意味着时序约束很勉强的达到要求。若是负数则需要改变设计来修复此violation,例如使用更大的drive strenth的driver来减少net delay。

反过来说,若是slack值相当大,则说明了此路径还有很多优化的机会。例如换成更小更慢的driver来减少面积,或者更高阈值的driver来减少leakage power。

以上是关于静态时序分析(static timing analysis) --- 时序路径的主要内容,如果未能解决你的问题,请参考以下文章