understanding of Pipe line & Timing Logic

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了understanding of Pipe line & Timing Logic相关的知识,希望对你有一定的参考价值。

/////////////////////////////////////////////////////////////////////////////////

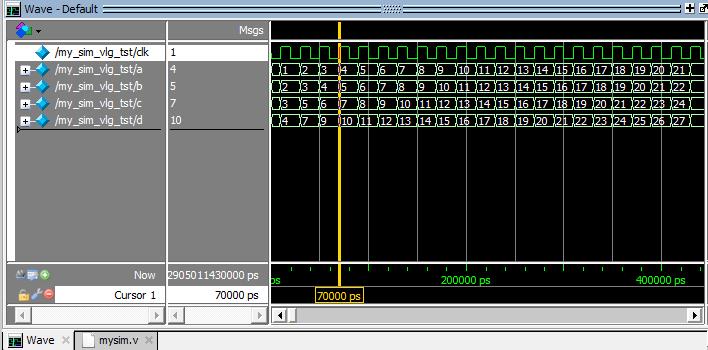

module vlg_add(

input clk,

output [7:0]a,

output [7:0]b,

output [7:0]c,

output [7:0]d

);

reg [7:0]reg_a = 0;

[email protected](posedge clk)

begin

reg_a <= reg_a + 8‘d1;

end

reg [7:0]reg_b = 0;

[email protected](posedge clk)

begin

reg_b <= reg_a + 8‘d2;

end

reg [7:0]reg_c = 0;

[email protected](posedge clk)

begin

reg_c <= reg_b + 8‘d3;

end

reg [7:0]reg_d = 0;

[email protected](posedge clk)

begin

reg_d <= reg_c + 8‘d4;

end

assign a = reg_a;

assign b = reg_b;

assign c = reg_c;

assign d = reg_d;

endmodule

//////////////////////////////////////////////////////////////////////////////////////////////

////////////////// TestBench//////////////////////////////////////////////////////////////

`timescale 1 ns / 1 ps

module my_sim_vlg_tst();

reg clk;

wire [7:0]a;

wire [7:0]b;

wire [7:0]c;

wire [7:0]d;

vlg_add vlg_add_inst(

.clk(clk),

.a(a),

.b(b),

.c(c),

.d(d)

);

initial

begin

clk = 0;

forever #10 clk = ~clk;

end

endmodule

/////////////////////////////////////////////////////////////

以上是关于understanding of Pipe line & Timing Logic的主要内容,如果未能解决你的问题,请参考以下文章