第一个FPGA程序——100MHz时钟分频

Posted Risun_Lee

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了第一个FPGA程序——100MHz时钟分频相关的知识,希望对你有一定的参考价值。

1.源文件

`timescale 1ns / 1ps module first_verilog( input clk, input rst, output reg cycle_20ms ); reg [23:0] cnt_reg ; always @(posedge clk) begin if(rst) begin cnt_reg <= 24\'d1; cycle_20ms <= 1\'b0; end else begin cnt_reg <= cnt_reg + 24\'d1; if(cnt_reg == 24\'d1000000) begin cnt_reg <= 24\'d1; cycle_20ms <= ~cycle_20ms; end end end endmodule

2.激励文件

`timescale 1ns / 1ps module tb_first_verilog(); reg clk; reg rst; reg cycle_20ms; first_verilog first_verilog_ins( .clk(clk), .rst(rst), .cycle_20ms()); parameter PERIOD = 10; always begin clk = 1\'b0; #(PERIOD/2); clk = 1\'b1; #(PERIOD/2); end initial begin clk = 1\'b0; rst = 1\'b0; #(10 * PERIOD); rst = 1\'b1; #(10 * PERIOD); rst = 1\'b0; end endmodule

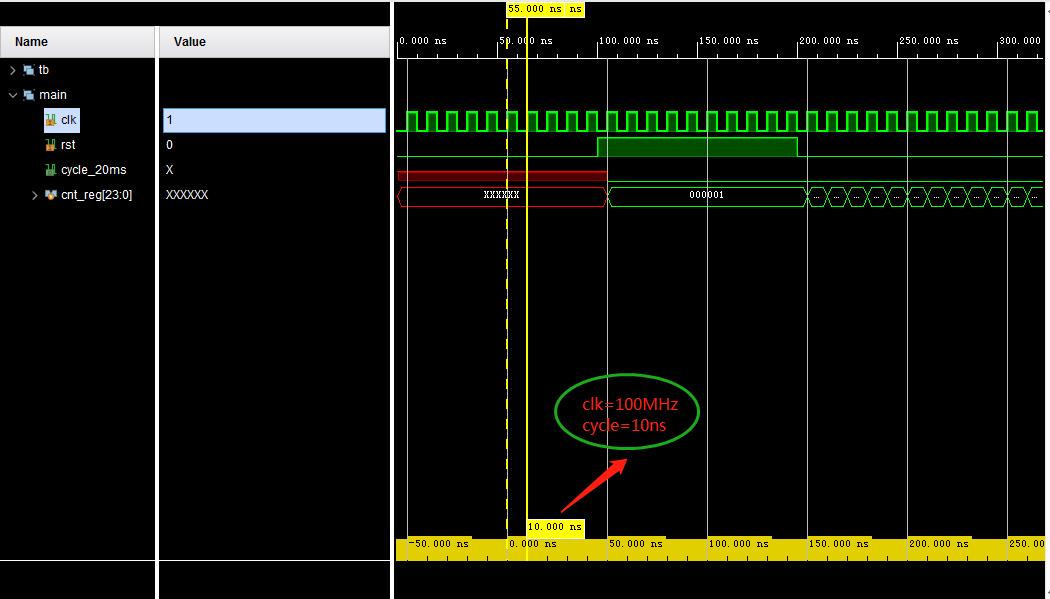

3.仿真结果

100MHz时钟

分频周期20ms的时钟

以上是关于第一个FPGA程序——100MHz时钟分频的主要内容,如果未能解决你的问题,请参考以下文章