调用altera IP核的仿真流程—上

Posted 大西瓜FPGA --logic3

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了调用altera IP核的仿真流程—上相关的知识,希望对你有一定的参考价值。

调用altera IP核的仿真流程—上

在学习本节内容之后,请详细阅读《基于modelsim-SE的简单仿真流程》,因为本节是基于《基于modelsim-SE的简单仿真流程》的基础上进行设计的,关于设计仿真流程的过程所涉及到的重复内容将不再详述,将会一笔带过,如果深入学习了《基于modelsim-SE的简单仿真流程》这一小节,则下面的内容将会非常的简单。

编写RTL功能代码

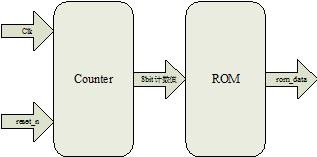

本小节通过调用altera的ROM宏功能模块,FPGA的ROM模块主要用于存储数据,可以在上电的时候进行写入(下载),ROM模块主要包含三个信号:时钟、地址、数据,在时钟的驱动下,往ROM写入地址,则ROM的数据端就会输出对应地址所存储的数据。采用《基于modelsim-SE的简单仿真流程》所设计的8bit计数器产生的8bit计数值作为ROM模块的地址信号,对ROM进行寻址,输出ROM中存储的数据。

在8bit计数器模块和ROM模块的基础上,新建一个RTL文件,对这两个模块进行信号映射并将ROM输出的数据信号进行输出。设计的结构如下所示:

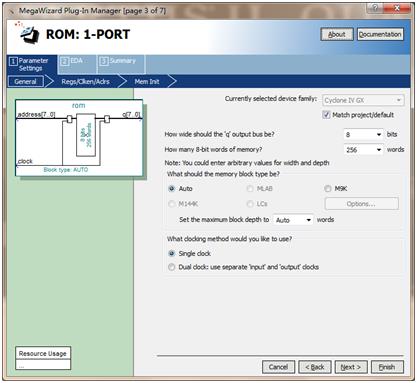

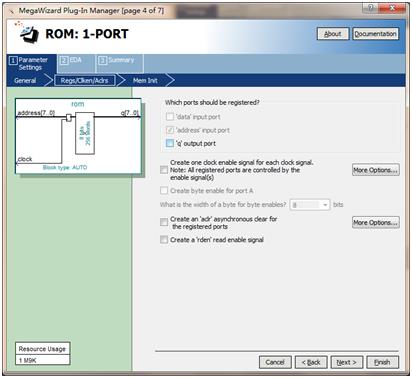

这里如何调用altera的ROM宏功能的过程就不详细说明了,这里简单说明ROM模块的参数设置,数据位宽为8bit,存储深度为256,如下图所示。

数据输出不经过寄存器

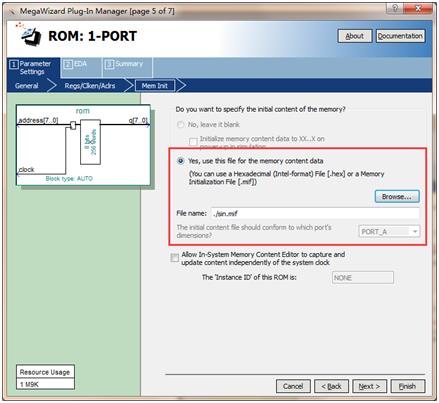

对ROM的原始存储文件进行设置,将sin.mif文件作为原始存储数据,sin.mif文件存储256个正弦波的数据,数据位宽和ROM的数据位宽一致。

编写顶层RTL文件,将两个模块连接起来,代码如下所示

|

module rom_top( clk, reset_n, rom_data ); input clk; input reset_n; output [7:0]rom_data;

wire[7:0]counter_out; counter counter_1( .clk (clk), .reset_n (reset_n), .counter_out(counter_out) ); rom rom_1( .address (counter_out), .clock (clk), .q (rom_data) ); endmodule |

编写testbench代码

Testbench文件采用1 ns/ 10 ps的时间单位和时间精度,该文件的激励输入信号只需要对时钟信号和复位信号进行赋值,同时输出信号是rom中存储的正弦信号。如下所示。

Testbench代码:

|

`timescale 1 ns/ 10 ps module rom_tst(); // constants // general purpose registers // test vector input registers reg clk; reg reset_n; // wires wire [7:0]rom_data;

rom_top rom_top_1( .clk (clk), .reset_n (reset_n), .rom_data (rom_data) ); initial begin // code that executes only once // insert code here --> begin clk<=1\'b0; reset_n<=1\'b0; // --> end $display("Running testbench"); end

always // optional sensitivity list // @(event1 or event2 or .... eventn) begin // code executes for every event on sensitivity list // insert code here --> begin #10 clk<=~clk; reset_n<=1\'b1; // --> end end endmodule |

创建工程

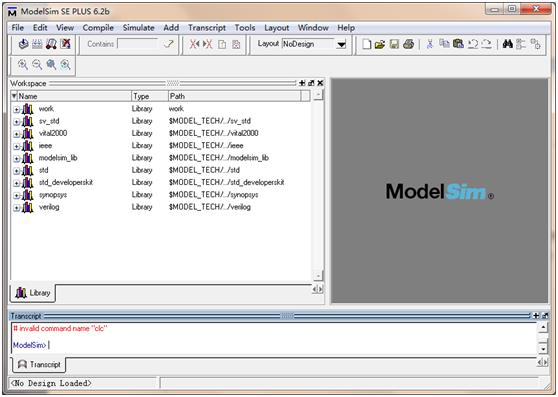

运行 ModelSim,方法是点击开始->程序->ModelSim SE->ModelSim 或双击桌面上的快捷方式,会出现如下图所示的界面,如果上一次使用ModelSim 建立过工程,这时候会自动打开上一次所建立的工程;

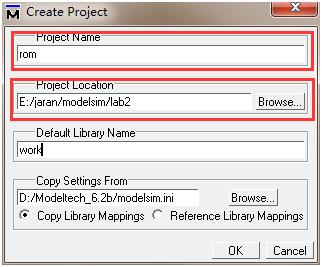

点击 File->New->Project,会出现如下图所示的界面。

选择project后,会出现如下界面在 Project Name 中我们输入建立的工程名字为rom,在Project Location 中点击browse按键,选择工程保存的路径,注意 ModelSim 不能为一个工程自动建立一个目录,这里最好是选择已经创建好的一个工程文件夹作为目录,在 Default Library Name 中为我们的设计编译到哪一个库中,这里使用默认值,这样,在编译设计文件后,在 Workspace 窗口的 Library中就会出现 work 库。这里我们输入完以后,点击 OK。

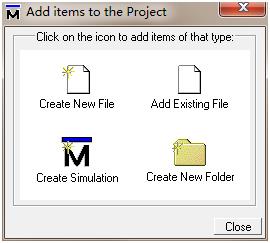

在点击OK按键后会出现选择仿真文件的界面,如下图所示,可以点击不同的图标来为工程添加不同的项目,点击 Create New File 可以为工程添加新建的文件, 点击 Add Existing File为工程添加已经存在的文件,点击 Create Simulation 为工程添加仿真,点击Create New Folder 可以为工程添加新的目录。这里我们点击Add Existing File;

这里将前面设计的counter.v文件、rom.v、rom_top.v、rom_tst.v 文件包含进工程里面,同时由于调用了Altera的IP核所以需要将IP核库文件包含进行来,该文件为altera_mf.v也包含到工程中(可以在quartus的安装目录下的eda/sim_lib文件夹下面找到这个文件)。点击browse按键,将文件包含进来,如下图所示,然后点击ok按键。

接着会在modelsim的工程工作窗口出现如下图所示,即已经将两个文件包含进来,其中在状态那一栏出现问号,表明文件包含进来了,还没有进行编译。

大西瓜FPGA-->https://daxiguafpga.taobao.com

博客资料、代码、图片、文字等属大西瓜FPGA所有,切勿用于商业! 若引用资料、代码、图片、文字等等请注明出处,谢谢!

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

以上是关于调用altera IP核的仿真流程—上的主要内容,如果未能解决你的问题,请参考以下文章

用Modelsim SE 直接仿真 Altera(Intel PSG) IP核 需要注意的问题