[转帖]你不曾见过的国产CPU:可能是最全的龙芯系列芯片家谱(下)

Posted jinanxiaolaohu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了[转帖]你不曾见过的国产CPU:可能是最全的龙芯系列芯片家谱(下)相关的知识,希望对你有一定的参考价值。

你不曾见过的国产CPU:可能是最全的龙芯系列芯片家谱(下)

https://www.ijiwei.com/html/news/newsdetail?source=pc&news_id=717789

欢迎回到下半场,更多龙芯系列处理器等着我们去认识。

2.6 龙芯2G/2G+/2GQ/2G-2000

龙芯2G是在“龙芯安全适用计算机CPU研制与应用”核高基重大专项课题支持下研发的,2008年开始投入设计,但由于龙芯当时2G项目和3A项目同时进行,存在重叠,影响了研发进度。2010年研制成功。龙芯2G采用65纳米工艺,主频1.0GHz,晶体管数目1亿,指令集兼容MIPS64,且增加了X86二进制翻译加速指令,以及龙芯媒体扩展指令,有64KB的指令和64KB数据的L1缓存,以及1MB的L2缓存,功耗3W。

在该处理器上,使用了X86二进制翻译技术,提出了在MIPS平台上实现X86动态二进制翻译的方法。

龙芯2G相当于龙芯3A1000的单核版本。

龙芯2GQ是龙芯2G的量产版,是一款四核处理器。龙芯2GQ与龙芯3A1000的区别在于龙芯2GQ不支持多路互联。

龙芯2GP后来更名为龙芯2I。

龙芯2G▲

搭载龙芯2GQ的笔记本电脑▲

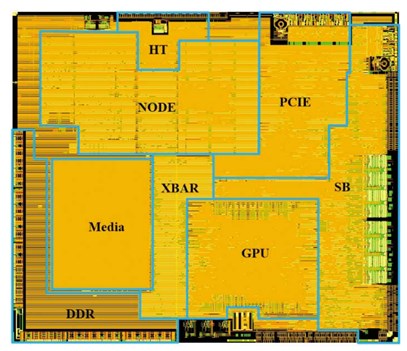

2.7 龙芯2H

龙芯2H是龙芯2G处理器与龙芯1A(2F南桥)的后继产品,其目标是为安全适用计算机提供单片解决方案。龙芯2H采用65nm工艺实现,主频达1GHz以上。主要用于网络设备等。兼容MIPS64指令集,支持X86二进制翻译指令集。有64KB的指令L1 cache和64KB的数据L1 cache,512KB的L2 cache。集成了GS232V媒体处理IP。

龙芯2H最初设想的应用是上网本,但随着上网本市场的消失,并没有在该领域应用。龙芯2H主要用在工控领域,以及包括防火墙在内的网络安全领域。

龙芯2H于2012年流片,2013年提供样片,2014年提供产品。龙芯2H的流片标志着龙芯全面掌握了复杂SOC的设计能力。龙芯2H的特点是大而全,集成了很多的功能,芯片设计很复杂,但缺少对特定应用的优化。

龙芯2H既可以作为独立SOC,还可以作为HT接口的南桥芯片。

龙芯2H▲

龙芯2H版图▲

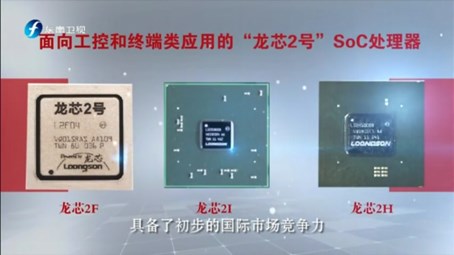

2.8 龙芯2I

根据龙芯内核资深维护者flygoat的分析,龙芯2I是龙芯2GP0800D的另外一个代号。关于龙芯2I的资料很少,下图为《中国正在说:芯芯之火可以燎原》节目中的截图,其中提到了龙芯2I。

龙芯2I▲

2.9 龙芯2J0800

龙芯2J是JP处理器,按JF需求定制,使用65纳米工艺流片,集成了一个四发射乱序执行GS464处理器核,主频800MHz。有64KB的L1指令缓存和64KB L1数据缓存,1MB的L2缓存,集成了2个GMAC控制器,64+8位DDR2/3内存控制器,32位PCI/PCIX控制器,LPC、SPI、UART等接口。龙芯2J是被用户单位总师评价为,“已知范围内性能最高,设计最复杂的JP CPU”。该处理器没有可公开的清晰照片。

龙芯2J0800▲

龙芯2J▲

2.10 龙芯2J1500

龙芯2J1500是龙芯2J的升级版,集成1个四发射乱序执行单核处理器核。和2J0800相比,处理器核从GS464升级到GS464E,工艺从65纳米提升到40纳米,性能有了很大的提升,虽然主频仍为800MHz,但计算能力提高1~2倍,功耗大大降低。2016年提供样片。

该处理器同样没有任何可以公开的清晰照片。

龙芯2J1500▲

2.11 龙芯2K1000

龙芯2K1000是一款双核处理器,采用了双发射64位的GS264微结构,40nm工艺生产,商业级芯片主频1GHz,工业级芯片主频800MHz。龙芯2K1000处理器是龙芯2H的升级芯片,其计算性能和IO带宽比龙芯2H都大幅提高。龙芯2K1000主要面向网络通信应用,兼顾平板及工业控制领域。

集成了64位DDR3控制器,2个GMAC控制器,2个X4 PCIE控制器,可以配置为6个X1模式。

集成共享的1MB二级cache;集成GPU,显示控制器,支持双路DVI显示。集成64位533MHz以上的DDR2/3控制器,1个SATA 2.0接口,4个USB 2.0接口,2个RGMII千兆网接口,集成HDA/AC97/I2S接口,集成RTC/HPET模块。集成最多4个UART控制器,1个NAND控制器,2个CAN控制器,1个SDIO控制器。

龙芯LS2K1000A▲

龙芯LS2K1000B▲

2.12 龙芯2K2000

龙芯2K2000是计划中龙芯2K1000的升级版,预计采用28纳米工艺生产,主频将达到2GHz。

3. 龙芯3号系列

龙芯3号处理器均为4发射64位多核处理器。目前,除了龙芯3B1500处理器为8核,其他的龙芯3号处理器均为4核。龙芯3C5000处理器会将处理器核数提高到16。

龙芯3号处理器的微结构分为GS464, GS464E,GS464V以及GS464EV。

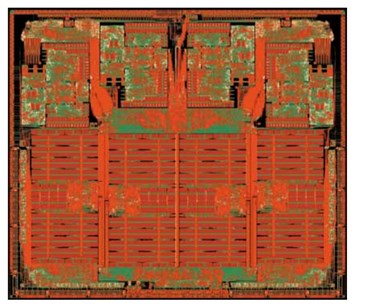

3.1 龙芯3A1000

龙芯3A1000于2008年底交付流片,采用意法半导体的65nm工艺流片. 2009年5月20日龙芯3A1000晶圆生产下线,9月28日样片回来,成功启动操作系统,主频800MHz-1GHz

龙芯3A1000进行了第一次改版并于2010年5月中旬流片,10月底第一次改版流片成功。3A1000的第二次改版于2012年2月下旬流片,2012年8月中旬流片成功。

龙芯3A1000集成了4个四发射乱序执行的GS464核,9级流水线,有64KB一级数据cache和64KB一级指令cache,4MB共享二级cache,最高主频1GHz,功耗15w(支持动态降频),芯片面积174mm2,晶体管数目4.25亿。每个CPU核包含两个浮点乘加部件,双精度浮点性能峰值为16GFlops。在龙芯3A1000处理器中,实现了x86二进制翻译加速指令。

3A100集成了HT1.0*2,PCI控制器、LPC、SPI、UART、GPIO。集成72位DDR2/3控制器,引脚1121个,封装方式40mmx40mm FCBGA。

龙芯龙芯3A1000 01版本▲

龙芯龙芯3A1000 02版本▲

龙芯3A芯片版图▲

图片来源:中科院计算所2009年成果年报

3.2 龙芯3B1000

龙芯3B1000于2010年6月20日左右流片,2010年11月底回来第一批芯片

3B1000的第一次改版2011年2月初流片,7月初回来。龙芯3B1000进行了第二次改版,于2011年12月初流片,2012年4月底回来。

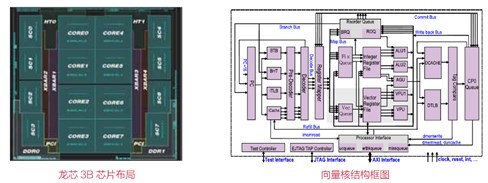

龙芯3B由核高基项目课题“高性能多核CPU研发与应用”支持,采用意法半导体65纳米工艺设计,主频1GHz,功耗25W,片内集成8个64位四发射乱序执行龙芯向量处理器核GS464V,4MB的二级cache,每个核包含两个256位向量部件,峰值浮点性能达到128GFLOPS。。

龙芯3B的最大特色是龙芯向量处理器核的设计,该处理器核将GS464核的的浮点部件和浮点寄存器堆替换为2个256位的向量处理部件和1个128x256位的向量寄存器堆,使龙芯3B在1GHz下的峰值双精度浮点计算能力达到128GFlops。在龙芯3B处理器中,实现了300多条专用的向量处理指令。

龙芯3B芯片面积300mm2,晶体管数目接近6亿。

龙芯3B1000▲

龙芯3B1000芯片布局和向量核结构框图▲

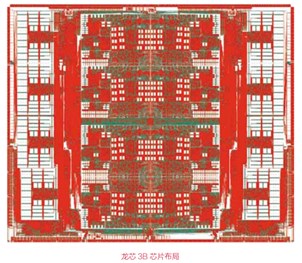

龙芯3B芯片布局▲

3.3 龙芯3B1500

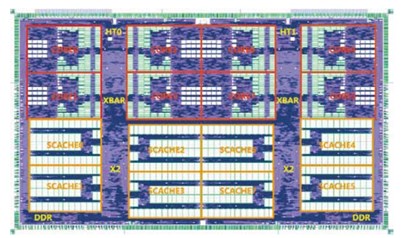

龙芯3B1500在2012年1月中旬完成设计并交付流片。2012年8月底拿到样片。后来,工艺从32nm迁移到28nm,于2013年4月底流片,10月底收到样片,但流片并不成功,后来又恢复到32nm工艺流片,并以某种方式补偿此次流片费用,于是又再次改版,于2015年1月底流片,2015年6月下旬收到样片。

龙芯原本计划推出一款16核的龙芯3C处理器,后来由于战略调整,取消了原龙芯3C的研发,缩水成8核的龙芯3B1500。龙芯3B1500集成了8个四发射乱序执行的64位GS464V处理器核,9级流水线,每个处理器核有64KB的私有一级指令cache和64KB的私有一级数据cache,128KB私有二级cache,有8MB三级共享cache,采用中芯国际32纳米工艺生产,芯片面积180mm2,晶体管数11亿,主频1.5GHz,采用倒装焊球栅阵列(Flip-Chip BGA)封装,芯片引脚数1121,封装大小40mm×40mm。单芯片双精度浮点计算能力达到192GFlops。功耗30w(典型)/60w(向量)。

在接口上,有HT2.0*2,PCI、LPC、SPI、UART、GPIO,72位DDR2/3控制器。

龙芯3B1500▲

龙芯3B1500版图▲

3.4 龙芯3A2000/3B2000

龙芯3A2000于2014年11月初交付流片;2015年4月10日,拿到盲封样片。2015年8月18日,龙芯召开发布会,正式发布新产品。2015年9月和2016年3月分别进行了第一次改版设计和第二次的改版设计。

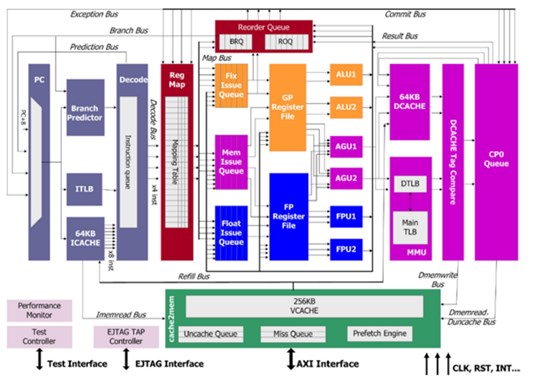

龙芯3A2000处理器集成了4个四发射乱序执行64位GS464E处理器核,也是首款采用GS464E微结构的处理器。采用中芯国际40纳米CMOS工艺生产,主频800~1000MHz,在1GHz下SPEC CPU2006分数为6.9分。封装方式FCBGA,1121引脚,封装大小40mm×40mm。

GS464E处理器核是GS464的改进版,集成了64KB一级指令cache,64KB一级数据cache,256KB二级cache和4MB三级cache。特别需要指出的是,GS464E处理器核的stream性能有了大幅提升,单核STREAM性能达到6.3GB/s,是龙芯3A1000的20倍。流水线从GS464的9级提高到了12级。峰值浮点性能16GFlops。

在接口上,龙芯3A200集成了两个HT3.0接口,PCI控制器、LPC、SPI、UART、GPIO,72位DDR2/3-1333×2控制器。

龙芯3A200A▲

龙芯3A2000B▲

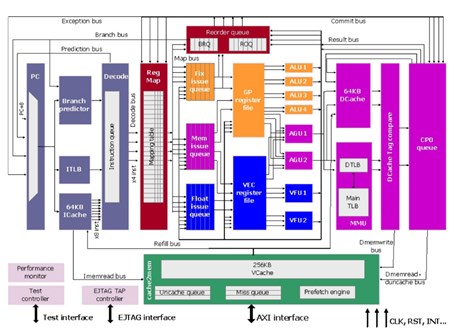

GS464E微结构图▲

3.5 龙芯3A1500

龙芯3A1500是龙芯3A2000的陶封版本,是工业级和JP级芯片,采用中芯国际40纳米LL技术流片,主频为700~1000MHz,推荐工作主频800MHZ。由于该芯片是JP芯片,没与可以公开的图片。

3.6 龙芯3A3000/3B3000

龙芯3A3000于2016年2月中旬交付流片, 6月中旬拿到盲封芯片.2016年10月17日,龙芯3A3000可以进入批量生产状态.

2017年4月26日,龙芯公司召开发布会,正式发布龙芯3A3000处理器。

龙芯3A3000/3B3000主频1.2Hz–1.5GHz,为4核处理器,采用4个四发射乱序执行的64位超标量处理器核(GS464E),支持MIPS64指令集,支持龙芯扩展指令集,采用12级超标量流水线;每核有2个定点单元、2个浮点单元和2个访存单元。每个处理器核包含64KB私有一级指令缓存和64KB私有一级数据缓存;每个处理器包含256KB私有二级缓存;所有处理器核共享8MB三级缓存。

和龙芯3A2000相比,除了流片工艺从中芯国际的40纳米提升到意法半导体的28纳米CMOS工艺,处理器的三级cache也从4MB提高到8MB。峰值浮点性能24GFlops。封装40mm*40mm BGA封装,1121个引脚,典型功耗<40W@1.5GHz。

集成的接口有HT3.0*2,PCI控制器、LPC、SPI、UART、GPIO,72位DDR2/3-1600*2,支持ECC。

龙芯3A3000的综合性能相当于Intel J1900处理器。

龙芯3A3000处理器▲

龙芯3B3000处理器▲

3.7 龙芯3A4000/3B4000

龙芯下一代高性能处理器,采用龙芯最新研发的GS464EV微结构。尽管龙芯3A4000仍然采用28nm工艺,但主频提高到2.0GHz,综合性能是上一代3A3000的两倍。目前已经流片成功,正在进行测试。据小道消息,龙芯3A4000进展顺利。

龙芯3A4000采用的GS464EV微结构▲

3.8 龙芯3A5000/3C5000

龙芯下一代高性能,预计2019年年底或2020年年初流片.采用3A4000的处理器微结构GS464EV,采用14/12nm工艺流片,主频提升到2.5GHz。3A5000依然是4核处理器,而3C5000将是一款16核处理器。

4. 龙芯桥片

4.1 龙芯7A1000

龙芯7A1000型桥片是龙芯3号处理器的第一款芯片组产品,目标是替代AMD RS780+SB710芯片组,为龙芯处理器提供南北桥功能。主要特点为:

16位HT 3.0接口,2D/3D GPU,显示控制器,支持双路DVO显示,16位DDR3显存控制器,3个X8 PCIE 2.0接口,每个X8接口都可以拆分为2个独立的X4接口。2个X4 PCIE 2.0接口,可以拆分为6个独立X1接口。3个SATA 2.0, 6个USB 2.0, 2个RGMII千兆网接口,HDA/AC97,RTC/HPET模块,1个全功能UART控制器,6个I2C控制器,1个LPC控制器,1个SPI控制器,多个GPIO引脚。

即将发布的龙芯3A4000将不再采用AMD的RS780芯片组,而采用龙芯7A作为桥片,避免在桥片的选择上受制于AMD。

龙芯7A1000桥片▲

5. 龙芯从未公布的隐藏处理器

除了龙芯1号、2号、3号三个系列的处理器,在龙芯的发展过程中还开发了一些实验型的处理器,并没有量产,有些甚至没有流片。我们找到了几个这样的处理器。

5.1 Godson-T

龙芯处理器在发展过程中,一度想要用做超算处理器,希望开发一款64核的众核处理器,命名为Godson-T。Godson-T由计算所先进微系统研究组研发,2008年已经在进行RTL验证在2008年12月开始RTL代码编写。2010年5月,GodSon-T的原型芯片16核GodSon-TI交付流片,采用130纳米工艺。2010年10月17日,调试成功。

由于龙芯将研发重点重新转向提高处理器单核性能,Godson-T处理器研发中止。

Godson-T处理器▲

5.2 Godson-X

龙芯所有量产的处理器,均采用的是MIPS指令集。但是,由于主流桌面处理器市场上使用的是x86指令集,基于知识产权和专利等原因,龙芯无法使用x86指令集。为了实现对现有生态的兼容,龙芯3A系列实现了针对x86指令和arm指令的二进制翻译指令。在研发过程中,龙芯开发了使用x86指令集的处理器原型Godson-X。。

这个项目从2005年7月开始。Godson-X处理器的设计初步目标是与x86指令兼容的FPGA原型处理器,并能在FPGA原型处理器中启动Windows XP。因此第一步,先进微系统研究组精心设计了微架构的Godson-X。Godson-X是一款基于Godson-2设计的4发射超标量X86处理器。它与x86兼容,并支持英特尔MMX指令,SSE指令集和x87浮点指令。第二步,通过Cycle级的模拟程序实现,模拟了处理器中每一拍运行的状态。在此之后,先进微系统研究组用模拟器尝试启动Windows XP。最后,先进微系统研究组的RTL调整和FPGA仿真完成时间为2006年7月。该处理器只有FPGA原型,从未流片。

5.3 龙梦一号

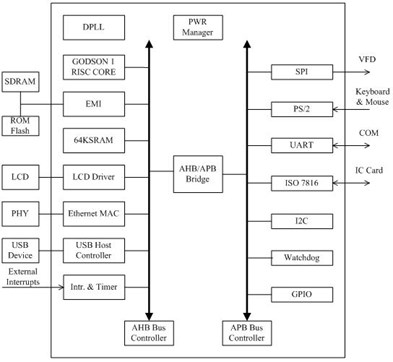

中科龙梦(现更名为航天龙梦)使用早期的龙芯1号的IP核,开发了龙梦一号SOC,用于税控机(Fiscal controller register)。该税控SoC专用芯片以“龙芯1”处理器核作为MCU,采用AHB(the Advanced High performance Bus)+APB(the Advanced Peripheral Bus)为片上总线。

集成的其余IP模块如表所示。

税控SoC体系结构▲

龙梦1号▲

5.4 GS32I-400 SOC

GS32I是根据龙芯2号设计的一款SOC芯片,主频400MHz,集成16K数据缓存和16K指令缓存,封装大小19mmx19mm,424针BGA封装。内部接口上,集成了PCI控制器,两个百兆网控制器,USB,AC97控制器,PCMCIA控制器,SDRAM控制器和EPROM控制器。

GS32i-400处理器▲

总结

综上所述,龙芯在其18年发展历程中,形成了一个相对完整的处理器家族,龙芯处理器可以应用于智能水表、智能门锁、航天应用、石油钻探、工业控制、网络安全、桌面办公等各种领域,为我国军工、航天、石油勘探等领域提供了重要的技术支持。期待下一代龙芯的高性能处理器龙芯3A4000早日发布,期待更高性能的3A5000和3C5000处理器早日流片。

以上是关于[转帖]你不曾见过的国产CPU:可能是最全的龙芯系列芯片家谱(下)的主要内容,如果未能解决你的问题,请参考以下文章