STA之PVT

Posted lelin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STA之PVT相关的知识,希望对你有一定的参考价值。

在STA星球,用library PVT、RC corner跟OCV来模拟这些不可控的随机因素。在每个工艺结点,通过大量的建模跟实测,针对每个具体的工艺,foundary厂都会提供一张推荐的timingsignoff表格, 建议需要signoff的corner及各个corner需要设置的ocv跟margin。这些corner能保证大部分芯片可以承受温度、电压跟工艺偏差,一个corner=libraryPVT+ RC corner + OCV,本文将关注于library PVT。

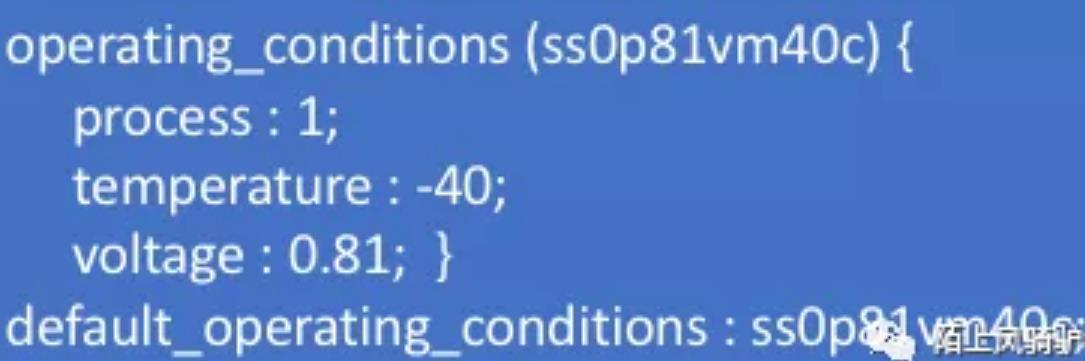

PVT也称为Operating condition,是STA一个基本且重要的概念,在library的表头会有operating condition的定义,如下图,其中『ss0p81vm40c』是这个operating condition的名字,通常这个名字是有意义的,它会标示出该lib对应的电压跟温度,如0p81对应于voltage:0.81,m40c对应于temperature:-40度。

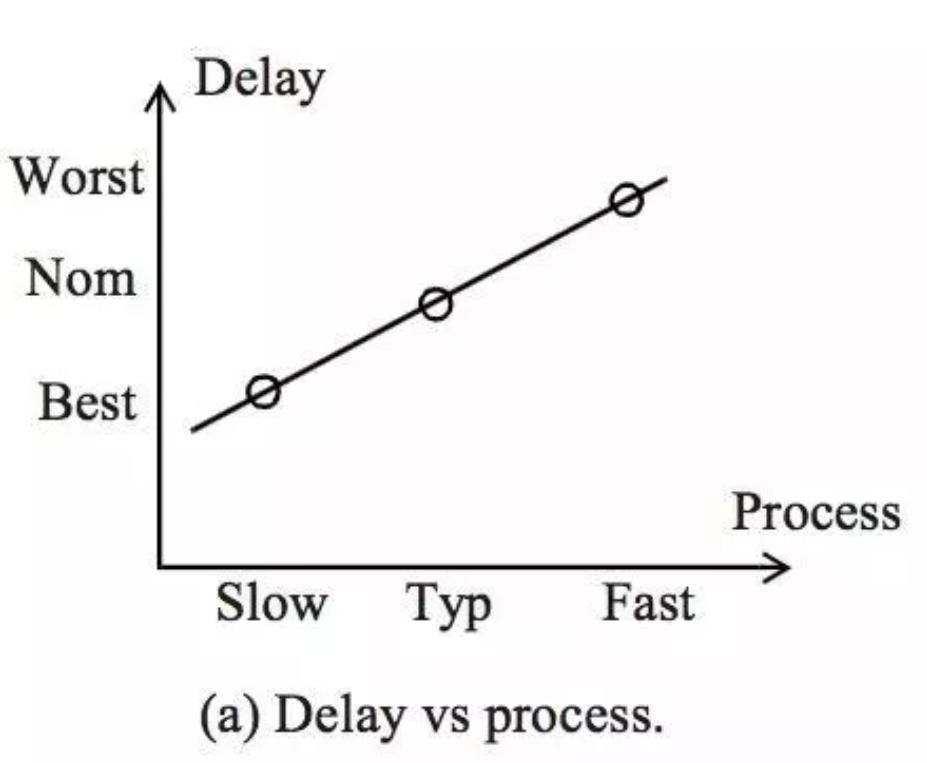

P-process:IC制造工艺本身的不完美,使得制造偏差不可避免,在library中会用一个百分比来表示工艺偏差,如process:1表示没偏差。在沉积或参杂过程中,杂质浓度密度、氧化层厚度、扩散深度都可能发生偏差,从而导致管子的电阻跟阈值电压发生偏差;光刻过程中由于分辨率的偏差会导致管子的宽长比产生偏差。而这些偏差,都会导致管子性能的差异。

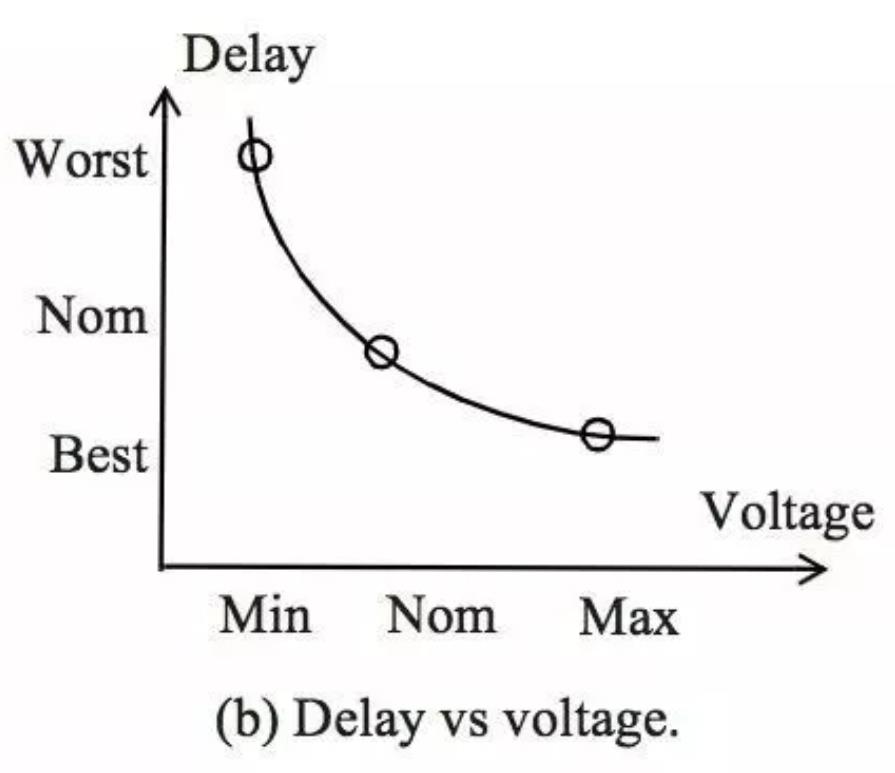

V-voltage:管子的延时取决于饱和电流,而饱和电流取决于供电电压。且不论多电压域芯片,就单电压芯片而言,电池的供电电压本身就在一个范围内变化,再加上片外或片上voltage regulator的误差、再加上IR,一个芯片上的每个管子都可能工作在不同电压下,从而性能也有所差别。

T-temperature:在日常操作中,IC芯片必须适应温度不恒定的环境,当芯片运行时,由于开关功耗、短路功耗和漏电功耗会使芯片内部的温度发生变化。温度波动对性能的影响通常被认为是线性的,但在深亚微米温度对性能的影响是非线性的。对于一个管子,当温度升高,空穴/电子的移动速度会变慢,使延时增加,而同时温度的升高也会使管子的阈值电压降低,较低的阈值电压意味着更高的电流,因此管子的延时减小。而通常温度升高对空穴/电子移动速度的影响会大于对阈值电压的影响,所以温度升高管子的延时呈增加趋势。但是并不是温度越低管子的延时就越小,晶体管有温度翻转效应,当温度低到某个值之后,随着温度的降低,管子的延时会增加,至于温度翻转点跟具体的工艺相关。

在做STA分析时,operating condition通常通过lib读入,如果多个library中的operating condition不同,通常用第一个读入的library中定义的operating condition。也可以用命令设置/定义operating condition,不同的工具有不同的实现方式,如:set_operating_condition。在debug环境时可以report_design来check当前所用的operating condition。

以上是关于STA之PVT的主要内容,如果未能解决你的问题,请参考以下文章