ZYNQ随笔——简述

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ZYNQ随笔——简述相关的知识,希望对你有一定的参考价值。

1. 硬核处理器与软核处理器在芯片内的硅片上通过划分一定的区域来实现处理器功能称为硬核处理器。

在一些对处理器性能要求不高的场合,通过使用FPGA内部资源搭建一个处理器功能称为软核处理器。

如果采用硬核处理器,整个芯片的成本会较高,且灵活性相对较差,但性能较高。如果采用软核处理器,成本较低,同时灵活性较高,但性能较低。

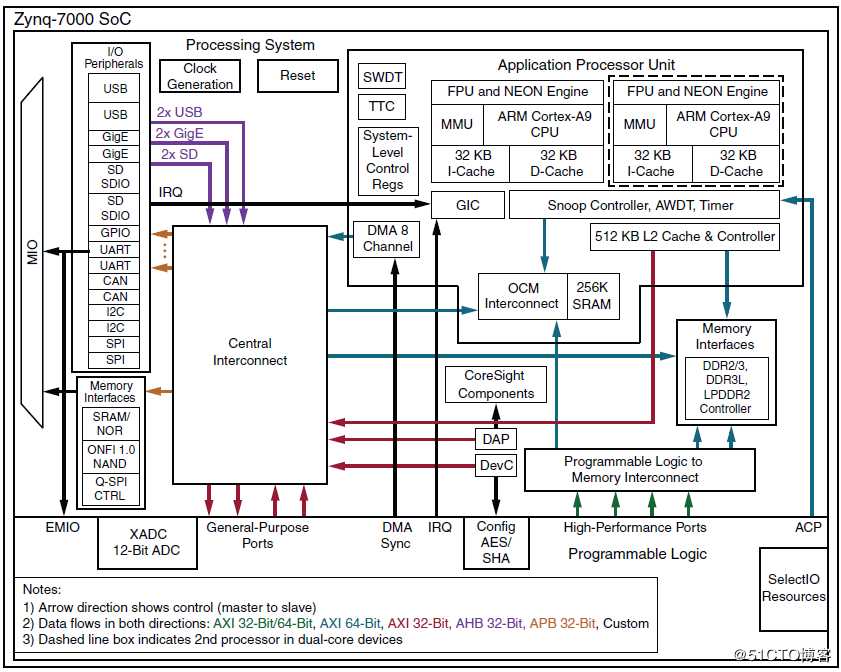

2. Zynq-7000 SOC功能结构

Zynq-7000由PS(Processing System)和PL(Programmable Logic)组成,内部结构图如下图所示。

- 应用处理器单元APU(Application Processor Unit):

双核A9(ARM V7),允许单个处理器,以及对称或非对称的多处理配置。 - 存储接口:

DDR控制器,支持DDR2/DDR3等存储器。

SMC(Static Memory Controller)静态存储控制器,支持NAND和并行SRAM/NOR存储器读写。 - I/O外设:

GPIO,PS提供54个GPIO信号,通过复用I/O模块MIO将这些信号连接到外部引脚,也可以通过拓展复用I/O模块EMIO将PS内的GPIO信号连接到PL端,

最多支持192个GPIO信号。

三速以太网控制器,在RGMII II模式时,使用MIO连接到外部PHY,在SGMII模式时,使用PL内部的GTX收发器模块,支持IEEE802.3和IEEE1588 V2.0协议。

USB控制器,支持OTG模式,只提供MIO引脚,内建DMA控制器,支持USB2.0高速设备,要求使用外部PHY。

SD/SDIO控制器,支持SD2.0规范,支持1~4位数据接口,低速时钟范围0~400KHz,高速时钟0~50MHz。

SPI控制器,UART控制器,CAN控制器,I2C控制器。 - PL逻辑资源:

CLB+BRAM+DSP48E1+DCM+SeletIO+XDAC+GTX+PCIE

以上是关于ZYNQ随笔——简述的主要内容,如果未能解决你的问题,请参考以下文章