ARM

Posted kele-dad

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARM相关的知识,希望对你有一定的参考价值。

1.1 ARM 分类

1.1.1 版本号分类

以前分类的是 ARM7,ARM9... ARM11,在 ARM11 之后,就是以 Cortex 系列分类了:

- Cortex-R:应用在实时系统上的系列

- Cortex-M:替代单片机的系列,M0 M3 M4 M7

- Cortex-A:A8 A9 A15 A72 A53

1.1.2 指令集分类

指令集原则上是向下兼容的。

指令集是根据核来分的,比如 ARMv7指令集、ARMv8指令集等等

1.2 ARM 商业模式及半导体公司

1.2.1 IP 核(知识产权)

ARM MIPS X86 PowerPC(IBM)

ARM 出卖 IP 而不卖芯片

1.2.2 半导体公司

主流的半导体公司有三星、高通、苹果、NXP(Freescale)、TI、ST、ATMEL、Ambarella、Amlogic、MTK、海思、全志、瑞芯微、展讯(基带)、炬力、联咏等等。

1.2.3 芯片、处理器和架构的联系

以 S3C2440 为例子:

1.3 ARM 处理器状态和处理器模式

在不同的体系下,有一些概念有所不同。这里主要以 S3C2440 为例子。

1.3.1 处理器状态

- 处理器状态有两种:

- ARM 状态:执行效率高

- THUMB 状态:代码密度好

- ARMV4 中,ARM 状态为32位,THUMB 状态为 16位,但是,在 ARMV7 中,ARM状态为32位,THUMB 状态为 16/32位状态,还有一种 THUMBEE状态,适用于 JAVA 运行的状态。

- 处理器状态的切换指令: BX BLX

- 指令集:

- ARM指令:32位

- THUMB指令:16位

- THUMB2:32/16位

- CORTEX-M 只是指令 THUMB2 指令子集

1.3.2 处理器模式

- 处理器模式共有 7 种:

- usr:用户模式

- fiq:快速中断模式

- irq:普通中断模式

- svc:保护/特权模式

- abt:异常模式

- sys:系统模式

- und:未定义模式

- 设计的目的:提高相应速度

- 注意:保护模式/特权模式,需要 MMU 和代码的支持

1.4 ARM 内部寄存器及 SFR

1.4.1 ARM 内部寄存器

- 此类寄存器设计在 CPU 内部,特点是速度快。

- 一共 37 个寄存器,31 个通用寄存器 和 6 个状态寄存器

- 通用寄存器:R0-R12,R13,R14,R15,R16

- R13(SP):栈指针,不同模式下栈空间是不一样的

- R14(LR):链接寄存器,存放断点,硬件自动完成

- R15(PC):程序指针,取指令的位置

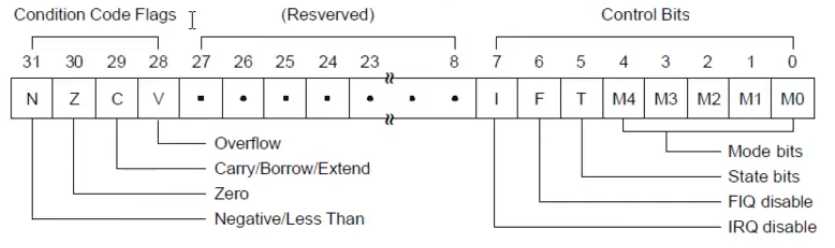

- 状态寄存器:PSR 分为 CPSR、SPSR

- 条件状态:NZCV

- 保留位

- IFT

- 模式位:M4-M0

- 通用寄存器:R0-R12,R13,R14,R15,R16

1.4.2 SFR 特殊功能寄存器

IO 端口/寄存器,它属于外设的组成部分。

ARM 是采用与存储器统一编址的方式使用软件编程控制某一硬件,起使就是编程读写该硬件的寄存器

1.5 ARM 异常处理和存储系统

1.5.1 模式与异常

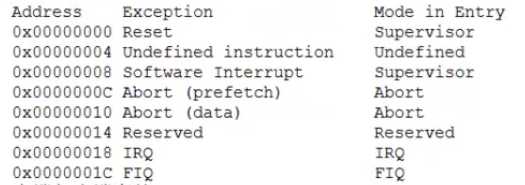

- 异常的类型:Reset、undefined instruction、swi、prefetch/bort、data/abort、Reserved、IRQ、FIQ

- 处理器的模式:每一个异常对应一种模式,但不是一一对应关系

1.5.2 中断向量表

1.5.3 大端与小端存储

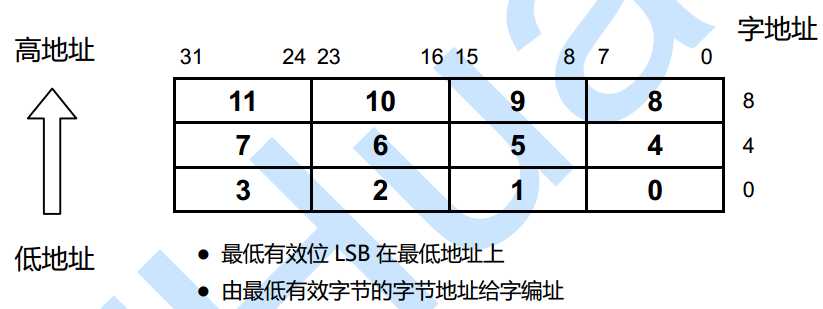

在大端格式中,字中最高有效位 MSB(Most Significant Byte)存储在编号最低的字节中,最低有效位 LSB(Least Significant Byte)存储在编号最高的字节中。因此存储器系统的字节 0 关联到数据行的 24 到 31。

在小端格式中,字中编号最低的字节被认为是最低有效位 LSB,编号最高的字节为最高有效位 MSB。因此存储器系统的字节 0 关联到数据行的 0 到 7。

以上是关于ARM的主要内容,如果未能解决你的问题,请参考以下文章