用Verilog语言设计一个3-8译码器

Posted toooney

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了用Verilog语言设计一个3-8译码器相关的知识,希望对你有一定的参考价值。

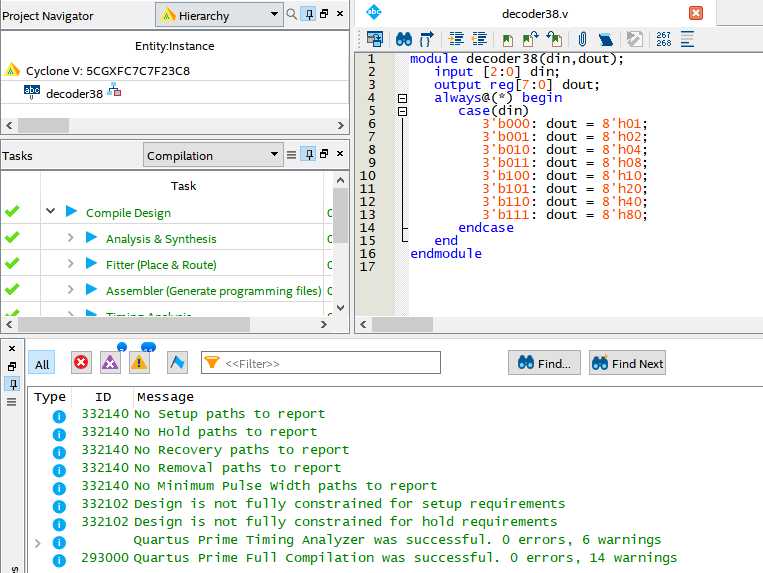

case语句

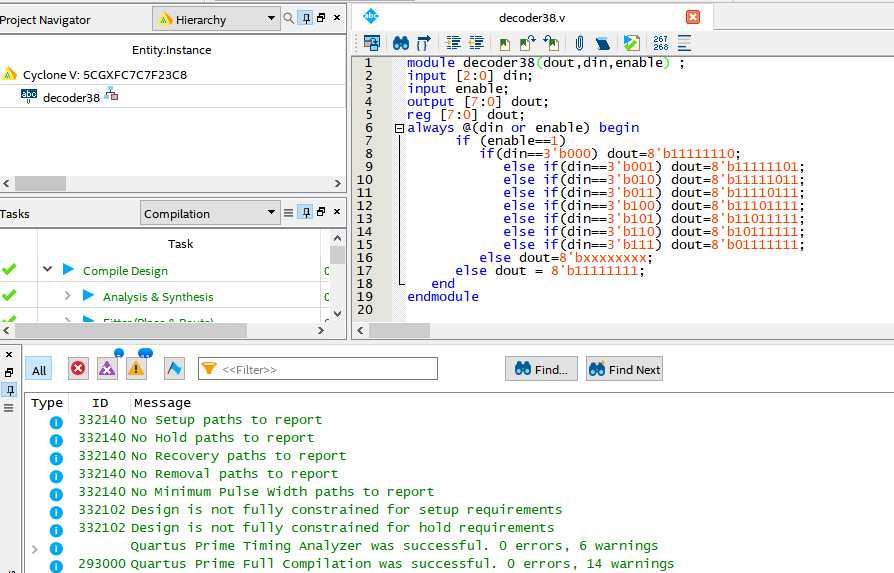

if_case语句

源代码

// case语句

module decoder38(din,dout);

input [2:0] din;

output reg[7:0] dout;

[email protected](*) begin

case(din)

3'b000: dout = 8'h01;

3'b001: dout = 8'h02;

3'b010: dout = 8'h04;

3'b011: dout = 8'h08;

3'b100: dout = 8'h10;

3'b101: dout = 8'h20;

3'b110: dout = 8'h40;

3'b111: dout = 8'h80;

endcase

end

endmodule

// if_case语句

module decoder38(dout,din,enable) ;

input [2:0] din;

input enable;

output [7:0] dout;

reg [7:0] dout;

always @(din or enable) begin

if (enable==1)

if(din==3'b000) dout=8'b11111110;

else if(din==3'b001) dout=8'b11111101;

else if(din==3'b010) dout=8'b11111011;

else if(din==3'b011) dout=8'b11110111;

else if(din==3'b100) dout=8'b11101111;

else if(din==3'b101) dout=8'b11011111;

else if(din==3'b110) dout=8'b10111111;

else if(din==3'b111) dout=8'b01111111;

else dout=8'bxxxxxxxx;

else dout = 8'b11111111;

end

endmodule

以上是关于用Verilog语言设计一个3-8译码器的主要内容,如果未能解决你的问题,请参考以下文章