分立元件封装尺寸及PCB板材工艺与设计实例

Posted Kevin_Hwang

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了分立元件封装尺寸及PCB板材工艺与设计实例相关的知识,希望对你有一定的参考价值。

分立元件封装尺寸

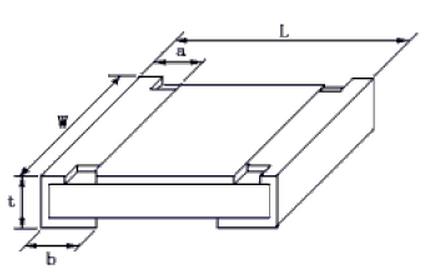

| inch | mm | (L)mm | (w)mm | (t)mm | (a)mm | (b)mm |

| 0201 | 0603 | 0.6±0.05 | 0.30±0.05 | 0.23±0.05 | 0.10±0.05 | 0.60±0.05 |

| 0402 | 1005 | 1.00±0.10 | 0.50±0.10 | 0.30±0.10 | 0.20±0.10 | 0.25±0.10 |

| 0603 | 1608 | 1.60±0.15 | 0.80±0.15 | 0.40±0.10 | 0.30±0.20 | 0.30±0.20 |

| 0805 | 2012 | 2.00±0.20 | 1.25±0.15 | 0.50±0.10 | 0.40±0.20 | 0.40±0.20 |

| 1206 | 3216 | 3.20±0.20 | 1.60±0.20 | 0.55±0.10 | 0.50±0.20 | 0.50±0.20 |

| 1210 | 3225 | 3.20±0.20 | 2.50±0.20 | 0.55±0.10 | 0.50±0.20 | 0.50±0.20 |

| 1812 | 4832 | 4.80±0.20 | 3.20±0.20 | 0.55±0.10 | 0.50±0.20 | 0.50±0.20 |

| 2010 | 5025 | 5.00±0.20 | 2.50±0.20 | 0.55±0.10 | 0.60±0.20 | 0.60±0.20 |

| 2512 | 6432 | 6.40±0.20 | 3.20±0.20 | 0.55±0.10 | 0.60±0.20 | 0.60±0.20 |

------------------------------------------------------------------------------------------------------------------------------------

板材工艺

以下参数或表格仅仅代表部分的板材工艺以及仿真选取参数,实际生产会有一定出入(但偏差不大!)

仿真计算软件使用polar的"Si9000"。

1oz=28.35g,1oz铜厚指1平方英尺的面积上平均铜箔的重量等于1oz的平均厚度,Hoz代表0.5oz。

1ft2=0.09290304m2,铜密度=8.9g/cm3。H=1oz/铜密度/1ft2。

计算得到H=34.3um,则1oz铜厚=H=34.3um=1.35mil。

但在PCB制作中,内层铜厚因为被打磨蚀刻而减少,外层则由电镀铜而加厚。

取内层1.2mil,外层1.8~2.1mil。

PCB芯板(core)厚度对照表:

| 芯板标称(mm) | 0.13 | 0.21 | 0.25 | 0.36 | 0.51 | 0.71 | / |

| 英标(mil) | 5 | 8 | 10 | 14 | 20 | 28 | |

| 芯板标称(mm) | 1.0 | 1.2 | 1.6 | 2.0 | 2.4 | 2.5 | 0.8 |

| 英标(mil) | 38.98 | 45.25 | 61.02 | 76.77 | 92.52 | 96.46 | 31.5 |

Note:第一行的芯板不含铜,第三行的芯板含铜。

半固化片材料(prepreg)的厚度以及介电常数对照表:

| 型号 | 厚度 | 介电常数 |

| 1080 | 2.8mil | 4.3 |

| 3313 | 3.8mil | 4.3 |

| 2116 | 4.5mil | 4.5 |

| 7628 | 6.8mil | 4.7 |

由于铜箔腐蚀的关系,导线的横截面不是矩形,而是梯形。

线条梯形截面参数对照表:

| 层 | 上线宽(mil) | 下线宽(mil) |

| 内层(0.5oz铜厚) | W-0.5 | W |

| 内层(1.0oz铜厚) | W-1 | W |

| 外层(0.5oz铜厚) | W-1 | W |

| 外层(1.0oz铜厚) | W-0.8 | W-0.5 |

------------------------------------------------------------------------------------------------------------------------------------

PCB叠层设计实例

以下是本人工作6层阻抗板叠层设计的案例,对于每个板厂材料的差异,仿真计算有一定出入。

设计要求:板厚1.0mm,单端阻抗50Ohm±10%,差分阻抗90Ohm±10%和100Ohm±10%。

叠层设计signal(L1)--gnd(L2)--signal(L3)--signal(L4)--power(L5)--signal(L6)。

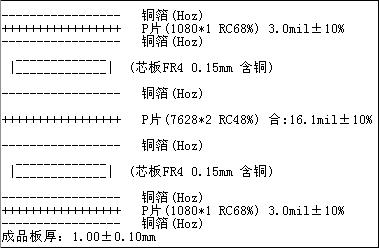

PCB供应商提供板材压合图:

L1/L6参考平面分别为L2/L5,L3/L4参考平面分别是L2(主要)&L4和L3&L5(主要)。

以下计算均是板厂提供的模型和参数计算所得,每个板厂均有差异,最好设计前与板厂取得相关参数。调整板层压合和线宽达到阻抗要求。

若没有固定供应商,则需选取一个合适的板层压合结构并且按照相近的参数,最后与板厂微调线宽达到设计要求(阻抗)。

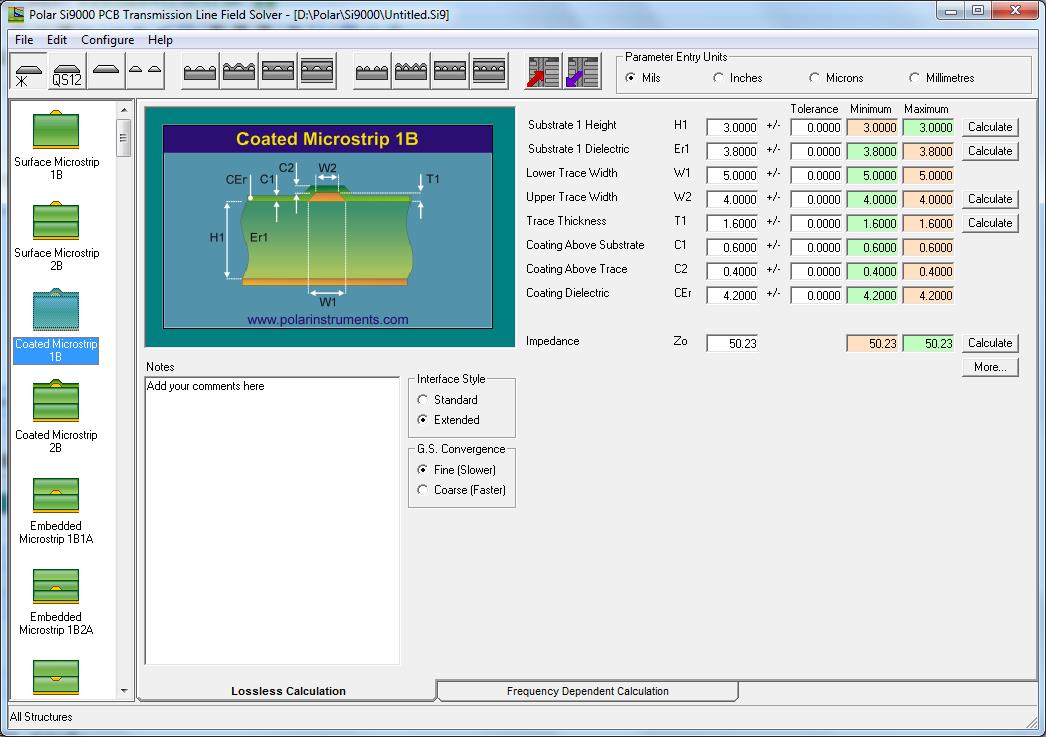

L1/L6单端50Ohm,PCB线宽为5mil,仿真如下图:

L1/L6差分90Ohm,PCB线宽为5mil&线距6mil,仿真如下图:

L3/L4差分90Ohm,PCB线宽为5.3mil&线距6mil,仿真如下图:

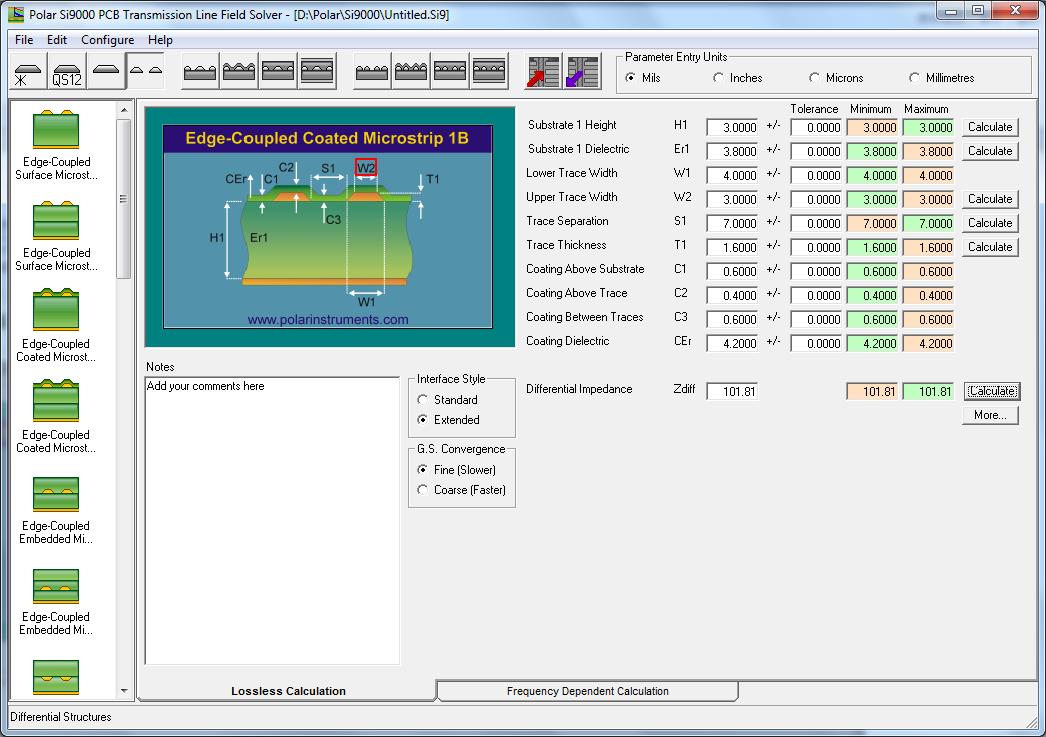

L1/L6差分100Ohm,PCB线宽为4mil&线距7mil,仿真如下图:

L3/L4差分100Ohm,PCB线宽为4.5mil&线距7mil,仿真如下图:

以上是关于分立元件封装尺寸及PCB板材工艺与设计实例的主要内容,如果未能解决你的问题,请参考以下文章