FPGAer:静态数码管显示实战

Posted fpgaer

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGAer:静态数码管显示实战相关的知识,希望对你有一定的参考价值。

想在一个六位的共阳极数码管上面显示数字,从000000依次显示到FFFFFF。

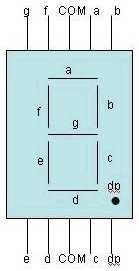

本次实战采用六位数码管,下面简单介绍一下共阳极数码管:

由图可知共阳极数码管由七段码abcdefg和一个小数点组成,并且引脚共同连接电压。也正是从这个内部结构可以知道,要想发光二极管点亮,那么引脚另外一端必须是低电平。

当然位选也是低电平有效的。

逻辑设计-Verilog代码编写:在这里考虑到逻辑不是很复杂,因此全部程序只有一个模块。一个模块中包含了三个always语句块:

①需要编写一个计数器,时间0.5s数字变化一次。同时时间到达之后,需要触发一个信号让数码管切换数字。

②让六个数码管的位选信号全部低电平。

③控制段码的高低电平,显示数字。

总结下来,静态数码管的代码实现简单。

以上是关于FPGAer:静态数码管显示实战的主要内容,如果未能解决你的问题,请参考以下文章

8051单片机实战分析(以STC89C52RC为例) | 05 - 静态数码管驱动