第三章 存储器(重点)

Posted by1314

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了第三章 存储器(重点)相关的知识,希望对你有一定的参考价值。

3.1 概述

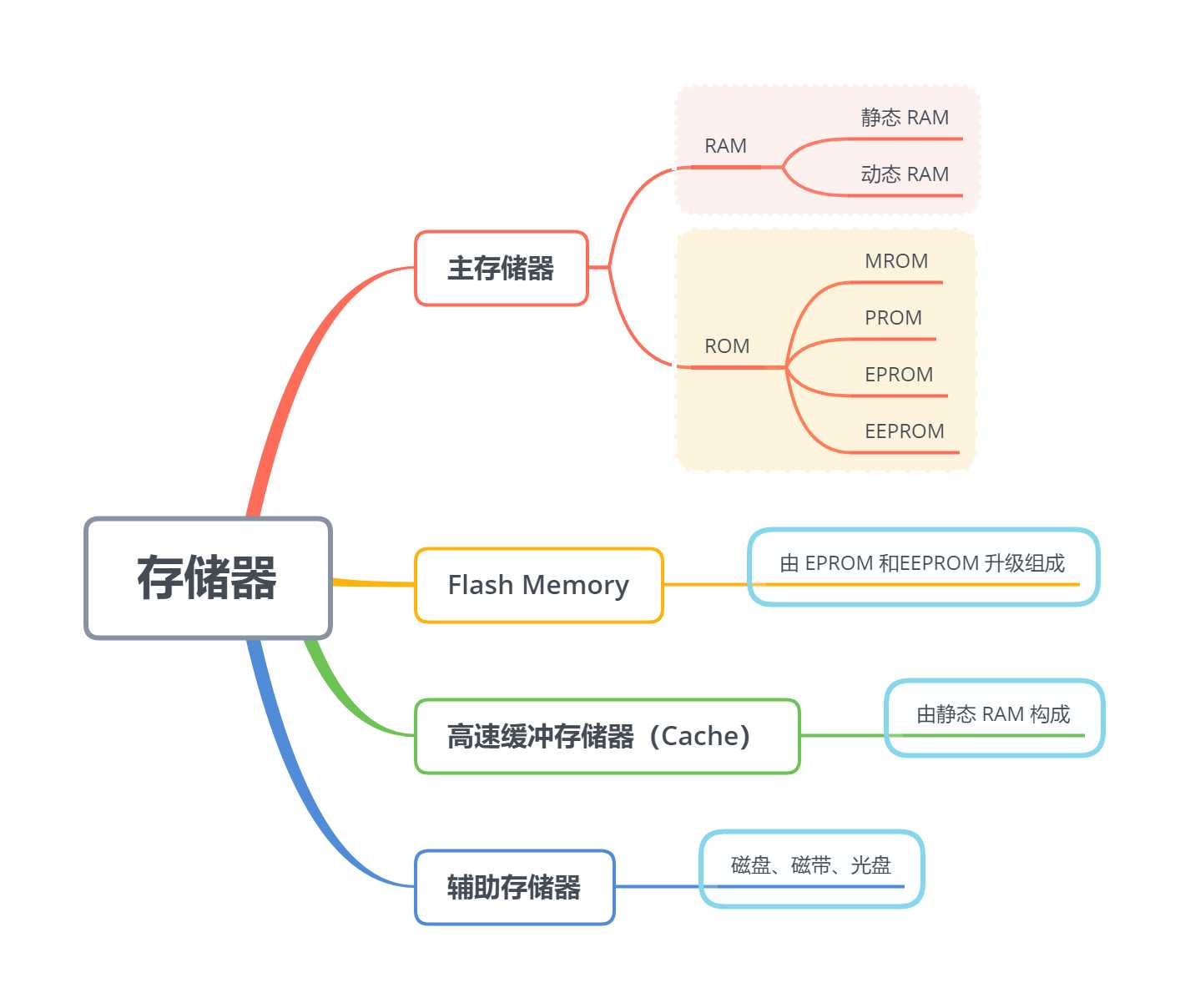

一、存储器分类

1. 按存储介质分类

易失

- 半导体存储器 ------> 双极性TTL、MOS(得有电)

不易失 - 磁表面存储器 -----> 磁头、载磁体

- 磁芯存储器 -------> 硬磁材料、环状元件

- 光盘存储器 --------> 激光、磁光材料

2. 按存取方式分类

(1)存取时间与物理地址无关(随机访问)

- 随机存储器(RAM):在程序的执行过程中可读、可写

- 只读存储器(ROM):在执行过程中只读

(2)存取时间与物理地址有关(串行/顺序访问) - 顺序存取存储器 磁带

- 直接存取存储器 磁盘(CHS)

- 相联存储器 ————> 用于快表(TLB),按内容寻址

3. 按计算机中的作用分类

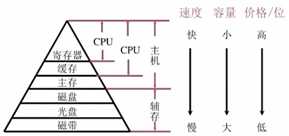

二、存储器的层次结构

1. 存储器三个主要特性关系

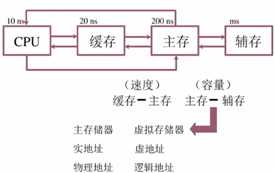

2. 缓存—主存层次 和 主存—辅存层次

注:

(1)辅存:固态硬盘(SSD)

(2)实地址、物理地址是一个概念

(3)虚地址、逻辑地址一个概念,可以用于程序设计

(4)虚拟存储器是操作系统干的活

(5)CPU不能直接访问辅存,可以利用操作系统(OS)来访问

(6)缓存—主存由硬件来完成,主存—辅存由OS来完成

(7)缓存相当于是备份了一小部分的主存中的内容

(7)操作系统(OS)通过缺页异常来完成主存和辅存之间数据的交换功能

(8)CPU取数据:CPU访问的永远是逻辑地址,操作系统要对逻辑地址判断是否在主存中,如果是还要判断是否在缓存中,若缓存中没有就要去主存中找,主存没有就去辅存。而 CPU 不能直接访问辅存,借用 OS 的缺页异常来把虚拟存储中的数据装入主存中,从而获得主存地址让CPU访问。

3.2 主存储器

一、概念

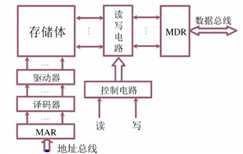

1. 主存储器的基本组成

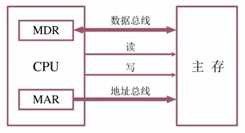

2. 主存和 CPU 的联系

3. 主存中存储单元地址的分配

注:

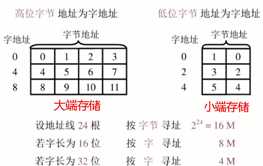

(1)注意是按字编址,还是按字节编址

(2)存储字为由高到低,当首字节存储的是高位的时候是大端存储,当首字节存储的是低位的时候是大小端存储。

4. 主存的技术指标

- 存储容量:主存存放二进制代码的总位数

- 存储速度:

- 存储时间:存储器的访问时间,读出时间、写入时间(一般读入快,写入慢)

- 存取周期:连续两次独立的存储器操作(读或写)所需的最小间隔时间,读周期、写周期

- 存储器的宽带:单位时间内从存储体存储的信息量(位/秒)

二、半导体存储芯片简介

1. 半导体存储芯片的基本结构

注:

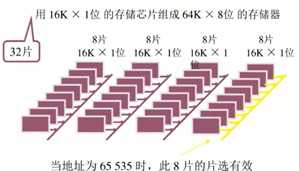

(1)芯片容量 = 2地址线个数 * 数据线数;ps:10根地址线有210个单元,每根数据线 1 bit

(2)片选线:低电位有效CS、CE

(3)读/写控制线:WE(低电平写、高电平读)、OE(允许读)、WE(允许写)

(4)片选线不在存储芯片内,芯片内只有地址线、数据线,片选线只是一个引脚。作用:选中多位芯片,用于芯片的扩展

2. 半导体存储芯片的译码驱动方式

?译码驱动:对于用户来提供地址线,来找对应的“房间号”。

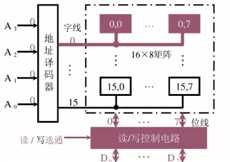

(1)线选法 16 * 8 bit 存储芯片

解析上图:只需要4根地址线通过地址译码器来找这16个“房间”。缺点:“房间”要是多了,连接“房间”的线太多

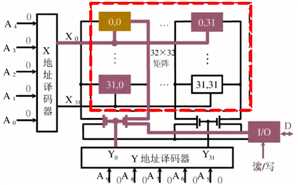

(2)重合法 1k * 1 bit 存储芯片

解析上图:采用矩阵(线代)的思想,1k * 1bit=1024bit,1024 = 210 = 25 * 25 = 32 * 32;————> 行地址只需5根地址线,来通过32根线来连接“房间”。同理列地址也是如此(18年408)

三、随机存储器(RAM)

1. 静态RAM(SRAM)——>了解为主

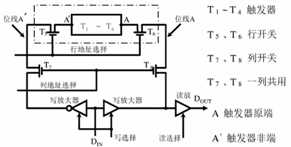

1.1 静态RAM基本电路

这里电路408考试过去11年没有出过题目,自主命题看高校

图片解析:

- T1 ~ T4四个管构成双稳态管,原端与非端存储相反且保持不变,除非进行写操作和掉电。

- 类似T5,若下端给高电位则导通,低电位阻塞。

- 缺点:能耗较高

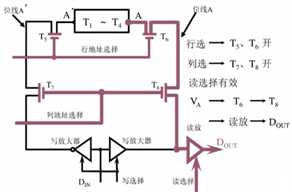

1.2 静态RAM基本电路的读操作

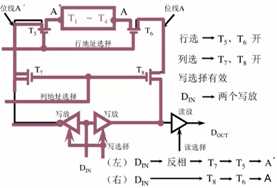

1.3 静态RAM基本电路的读操作

(2)SRAM 芯片举例(可能会考该芯片的存储容量)

外部特点:

读写:WE、片选线:CS、地址线、数据线

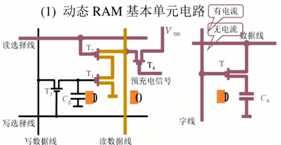

2. 动态RAM(DRAM)——>了解为主

| 三管式 | 单管式 |

|---|---|

| 读入与原存信息相反 | 读出时数据线有电流,为“1” |

| 写入与输入信息相同 | 写入时CS充电为“1”,放电为“0” |

注:DRAM电容有再生(刷新)的问题,优点:能耗较低

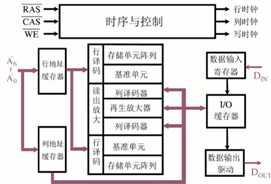

2.1 单管动态RAM4116(16k * 1bit)外特性(很重要)

图片解析:

(1)行选信号RAS,列选信号CAS,地址线为什么7根?可以联系重合法

(2)行、列地址分开传送

| 读时序 | 写时序 |

|---|---|

| 行地址RAS低电平有效 | 行地址RAS低电平有效 |

| 写允许WE有效(高) | 写允许WE有效(低) |

| 列地址CAS低电平有效 | 数据DIN有效 |

| 数据DOUT有效 | 列地址CAS低电平有效 |

2.2 动态RAM刷新 ——> 刷新与行地址有关

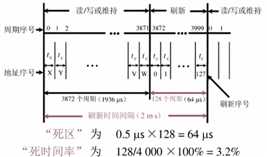

(1)集中刷新

?以 128 * 128 矩阵为例(存取周期为 0.5 μs)

死区:刷新区间不能向外提供服务。

4000=刷新时间间隔/存取周期

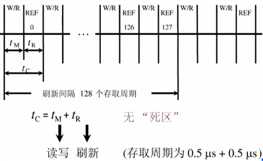

(2)分散刷新

?以 128 * 128 矩阵为例(存取周期为 1 μs)

代价:存取周期加长

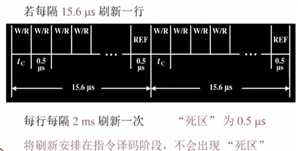

(3)分散刷新与集中刷新相结合(异步刷新)

?以 128 * 128 矩阵为例(存取周期为 0.5 μs)

每个多长时间刷新一行(15.6 μs) = 时间间隔(2ms)/行数(128)

3. 动态RAM和静态RAM的比较

| DRAM(主存) | SRAM(缓存) | |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

以上是关于第三章 存储器(重点)的主要内容,如果未能解决你的问题,请参考以下文章