NVDIMM编程模型原理大概推导梳理

Posted 资质平庸的程序员

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了NVDIMM编程模型原理大概推导梳理相关的知识,希望对你有一定的参考价值。

NVDIMM编程模型原理大概推导梳理2021

1 NVDIMM 简介

NVDIMM(Non-Volatile DIMM) 非易失性DIMM(Dual In-line Memory Module,双列直插式内存模块),即

- 掉电不丢失数据;

- 兼容 DIMM 插槽(通过插入内存条插槽接入计算机使用);

故俗称 pmem(persistent memory)。

2 NVDIMM 编程模型原理推导梳理

原理上 NVDIMM 可直接作为一段物理内存使用——就像一块 DRAM 一样,此时可能需要注意

- NVDIMM 比 DIMM 还是要慢一些;

- NVDIMM 不丢失数据,进程重启后考虑清理重启前的程序状态。

着重掉电不丢失数据,不抢占 DRAM 原本角色,将 NVDIMM 作为持久性外设使用更为常见 —— 操作系统通过内存映射(mmap)的方式对外呈现提供使用。

① 将 pmem 外设转换为文件访问;

② 在用户程序进程地址空间中分配大小为 m 的虚拟地址空间段与 fd 对应设备的容量空间形成映射关系。当指定 MAP_SYNC 等标识时表示用户程序用mmap分配的虚拟地址空间直接映射真实设备,数据读写发生于数据原所在 DRAM 内存段与真实设备之间(CPU直接将原内存中的数据通过硬件路线写于真实设备,或通过硬件线路读真实设备数据于指定内存中,由于pmem位于内存插槽中,硬件线路速度很快);

③ - ④若无指定 MAP_SYNC 等标识时,用户程序用mmap分配虚拟地址空间还将与 DRAM 物理内存页映射。当访问用户虚拟地址时,内核会分配 DRAM 内存页与用户虚拟地址空间对应,用户的数据读写在数据原在内存与mmap映射的DRAM内存页之间发生。用户程序通过调用 msync 显式地将 DRAM 内存页中的内容刷到真实设备上。 用户程序读真实设备时,CPU将数据读到 mmap虚拟地址空间对应的DRAM内存页供用户程序访问。

3 稍微再多一点点 —— CPU 缓存

mmap DAX 省去了内存层面的数据同步问题,但需在 CPU 缓存层面考虑数据同步问题,主要包括

- 数据同步(Cache Line到设备);

- 数据顺序(多核);

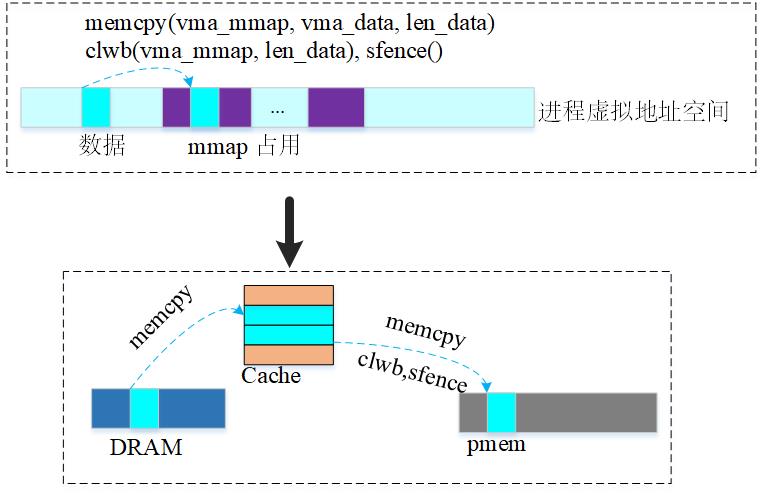

将 CPU 缓存考虑在内,mmap DAX 数据读写大概如以下简述。

memcpy 将 DRAM 中的数据读到 pmem 时会经过 CPU Cache,CPU Cache 中的数据未必都会立即回写到 pmem 中。为了保证 memcpy 的数据落到 pmem 中,需将 CPU Cache 中的数据回写到 pmem (如CLFLUSH/CLFLUSHOPT/CLWB),若需在写其他数据前保证此次数据被全部写到 pmem 中还需使用屏障指令(如SFENCE)等待 此次 CPU Cache 回写。另外,pmem一次所能接受或输出的最大数据(如32位,64位)将是硬件层面的一次原子操作。

以上是没看什么资料大概脑补的,以下是而后看到的更好的。

以上是关于NVDIMM编程模型原理大概推导梳理的主要内容,如果未能解决你的问题,请参考以下文章