Xilinx Vivado CORDIC IP核求解atan 反正切

Posted yuya-memeda

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Xilinx Vivado CORDIC IP核求解atan 反正切相关的知识,希望对你有一定的参考价值。

赛灵思官方提供了cordic(coordinate rotational digital computer) ip核实现直角坐标极坐标变化,三角函数的操作。我介绍下它进行反正切求解的使用:

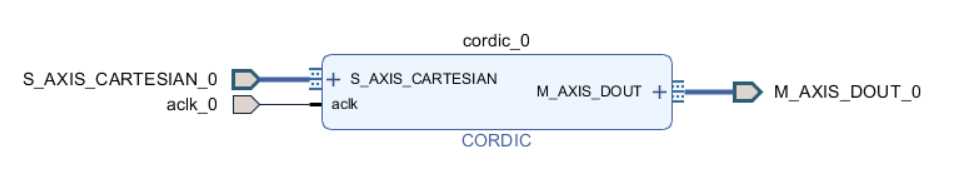

新建个简单工程:bd如下

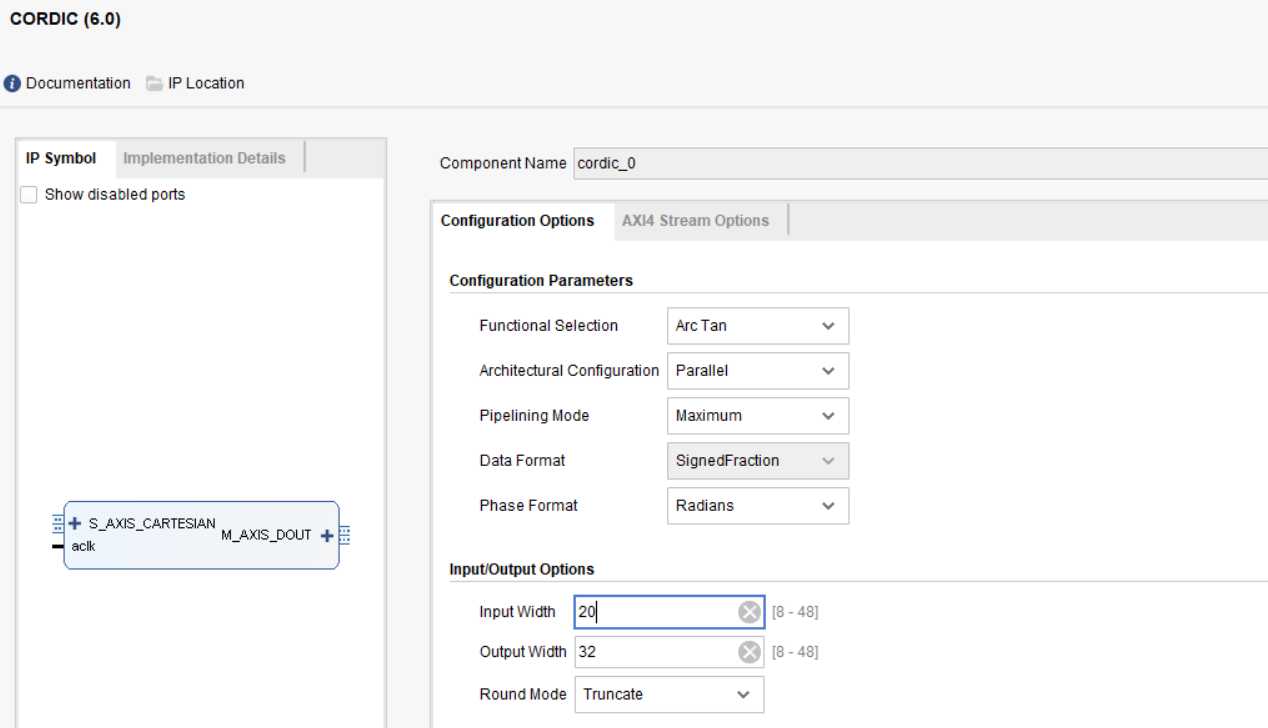

进行ip设置,选择运算位反正切后,ip端口回自动变为上图,再引出2个总线和时钟,xilinx的ip核不少是基于AXI4-Stream总线,这里使用并不复杂,默认只有2个信号,一个数据线tdata,一个握手信号tvalid,tvalid拉高时数据信号有效。

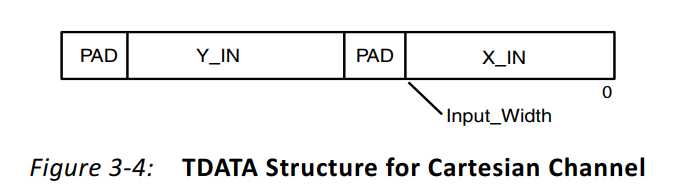

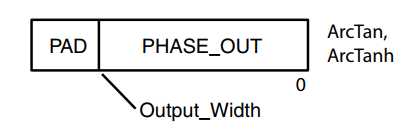

确定了输入输出位宽后,系统会自动求解出需要的延时latency。这里说一句,AXI-Stream总线收发基于byte的,无论输入什么位宽最后都是8的整数倍。所以需要参照UG,放置好有效输入位和分解输出位。

如果输入输出位宽恰好不是8的倍数,那么tdata位宽是大于设定的值的。所以需要上图提到进行填充(PAD),比如我输入20位,x和y加起来40位,那么输入S_AXIS的位宽是48,我要在0-19放x,20-23放填充数据(随意,我用0),24-43放y,44-47放填充数据。必须保证0-19和24-25分别是我的x和y。

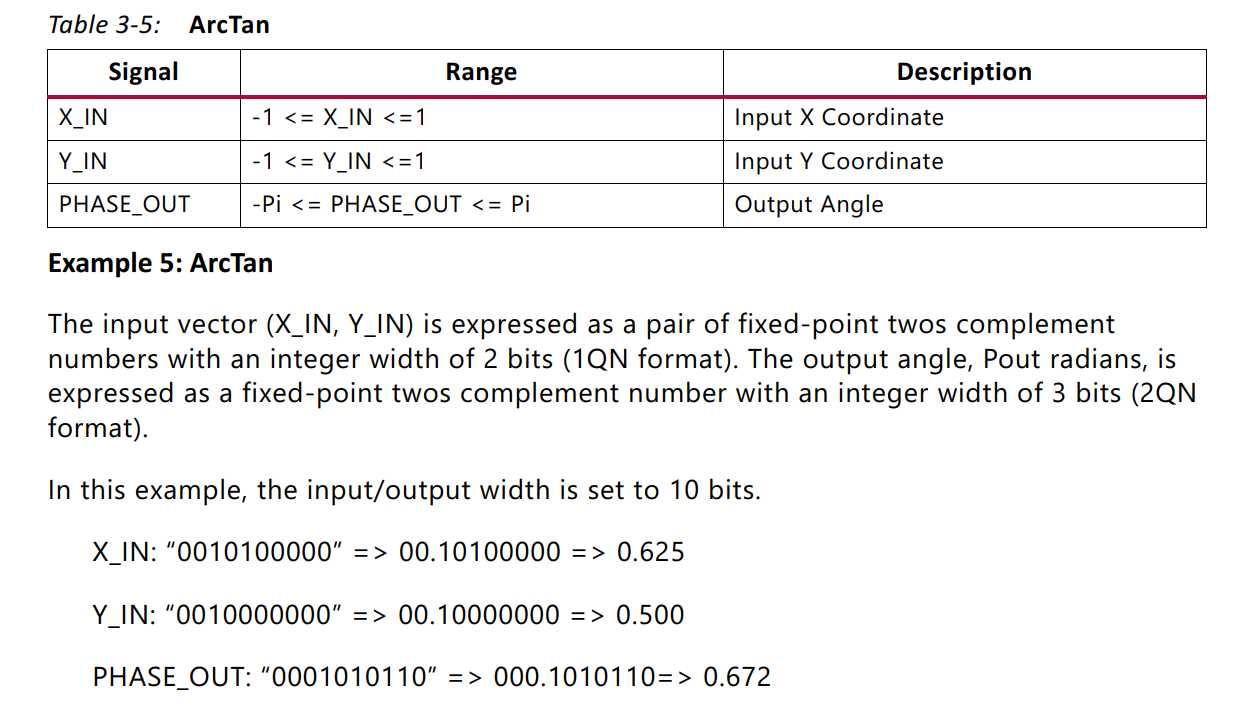

atan=y/x,要求输入必须是[-1,1],所以如果数据不是这个区间还需要进行归一化处理(可以用除法器div_gen ip核,这里不做介绍了)。上图是一个简单的示例,介绍输入输出的定点小数格式。整数部分的第一位是符号位,小数部分没有符号位是正的。

这里关于二进制小数表示,可以看下这个https://blog.csdn.net/AaricYang/article/details/87882868。整数的每一位权重是2^(n-1) 111就是2^2+2^1+2^0=7,小数部分的权重是2^(-n) 0.111就是2^(-1)+2^(-2)+2^(-3)=0.875

`timescale 1 ns / 1 ps module cordic_tb_top; reg aclk; wire [31:0]M_AXIS_DOUT_0_tdata; wire M_AXIS_DOUT_0_tvalid; reg [47:0]S_AXIS_CARTESIAN_0_tdata; reg S_AXIS_CARTESIAN_0_tvalid; integer handle; initial begin aclk=0; S_AXIS_CARTESIAN_0_tvalid=1‘b0; S_AXIS_CARTESIAN_0_tdata=‘b0; end initial handle = $fopen("D:/FPGAcode/_file/cordic.txt");//打开文件 always #10 aclk=~aclk; localparam PAD=(48-20*2)/2; always@(posedge aclk) begin S_AXIS_CARTESIAN_0_tvalid<=1‘b1; S_AXIS_CARTESIAN_0_tdata<={{PAD{1‘b0}},{3‘b000,17‘b0},{PAD{1‘b0}},{3‘b111,17‘b0}}; end always@(posedge aclk) begin if(M_AXIS_DOUT_0_tvalid) $fdisplay(handle,"%b",M_AXIS_DOUT_0_tdata);//写数据 end design_1_wrapper design_1_i (.M_AXIS_DOUT_0_tdata(M_AXIS_DOUT_0_tdata), .M_AXIS_DOUT_0_tvalid(M_AXIS_DOUT_0_tvalid), .S_AXIS_CARTESIAN_0_tdata(S_AXIS_CARTESIAN_0_tdata), .S_AXIS_CARTESIAN_0_tvalid(S_AXIS_CARTESIAN_0_tvalid), .aclk_0(aclk)); endmodule

给个简单的testbench

如果自己参考文献,用HDL实现一个CORDIC算法的模块,应该是很不错了。但是我偷懒直接用现成IP了

以上是关于Xilinx Vivado CORDIC IP核求解atan 反正切的主要内容,如果未能解决你的问题,请参考以下文章

FPGA教程案例15基于vivado核的Cordic算法设计与实现