Transistor count

Posted ztguang

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Transistor count相关的知识,希望对你有一定的参考价值。

https://en.wikipedia.org/wiki/Transistor_count

Transistor count

From Wikipedia, the free encyclopedia

Jump to navigationJump to search

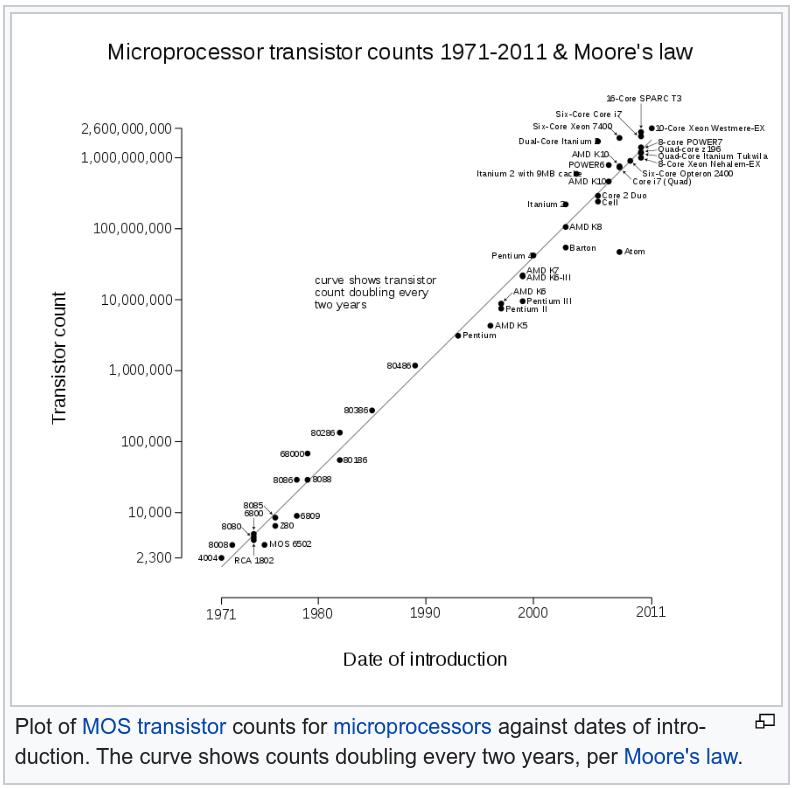

Plot of MOS transistor counts for microprocessors against dates of introduction. The curve shows counts doubling every two years, per Moore's law.

The transistor count is the number of transistors on an integrated circuit (IC). It typically refers to the number of MOSFETs (metal-oxide-semiconductor field-effect transistors, or MOS transistors) on an IC chip, as all modern ICs use MOSFETs. It is the most common measure of IC complexity (although the majority of transistors in modern microprocessors are contained in the cache memories, which consist mostly of the same memory cell circuits replicated many times). The rate at which MOS transistor counts have increased generally follows Moore's law, which observed that the transistor count doubles approximately every two years.

As of 2019, the largest transistor count in a commercially available microprocessor is 39.54 billion MOSFETs, in AMD's Zen 2 based Epyc Rome, which is a 3D integrated circuit (with eight dies in a single package) fabricated using TSMC's 7 nm FinFET semiconductor manufacturing process.[1][2] As of 2018, the highest transistor count in a graphics processing unit (GPU) is Nvidia's GV100 Volta with 21.1 billion MOSFETs, manufactured using TSMC's 12 nm FinFET process.[3] As of 2019, the highest transistor count in any IC chip is Samsung's 1 TB eUFS (3D-stacked) V-NAND flash memory chip, with 2 trillion floating-gate MOSFETs (4 bits per transistor).[4] As of 2019, the highest transistor count in a non-memory chip is a deep learning engine called the Wafer Scale Engine by Cerebras, using a special design to route around any non-functional core on the device; it has 1.2 trillion MOSFETs, manufactured using TSMC's 16 nm FinFET process.[5][6][7][8]

In terms of computer systems that consist of numerous integrated circuits, the supercomputer with the highest transistor count as of 2016 is the Chinese-designed Sunway TaihuLight, which has for all CPUs/nodes (1012 for the 10 million cores and for RAM 1015 for the 1.3 million GB) combined "about 400 trillion transistors in the processing part of the hardware" and "the DRAM includes about 12 quadrillion transistors, and that's about 97 percent of all the transistors."[9] To compare, the smallest computer, as of 2018 dwarfed by a grain of sand, has on the order of 100,000 transistors, and the one, fully programmable, with the fewest transistors ever has 130 transistors or fewer.

In terms of the total number of transistors in existence, it has been estimated that a total of 13 sextillion (1.3×1022) MOSFETs have been manufactured worldwide between 1960 and 2018, accounting for at least 99.9% of all transistors. This makes the MOSFET the most widely manufactured device in history.[10]

Contents

Transistor count

Part of an IBM 7070 card cage populated with Standard Modular System cards

Among the earliest products to use transistors were portable transistor radios, introduced in 1954, which typically used 4 to 8 transistors, often advertising the number on the radio's case. However, early junction transistors were relatively bulky devices that were difficult to manufacture on a mass-production basis, limiting the transistor counts and restricting their usage to a number of specialised applications.[11]

The MOSFET (MOS transistor), invented by Mohamed Atalla and Dawon Kahng at Bell Labs in 1959,[12] was the first truly compact transistor that could be miniaturised and mass-produced for a wide range of uses.[11] The MOSFET made it possible to build high-density integrated circuits (ICs),[13] enabling Moore's law[14][15] and very large-scale integration.[16] Atalla first proposed the concept of the MOS integrated circuit (MOS IC) chip in 1960, followed by Kahng in 1961, both noting that the MOSFET's ease of fabrication made it useful for integrated circuits.[11][17] The earliest experimental MOS IC to be demonstrated was a 16-transistor chip built by Fred Heiman and Steven Hofstein at RCA Laboratories in 1962.[15] Further large-scale integration was made possible with an improvement in MOSFET semiconductor device fabrication, the CMOS process, developed by Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor in 1963.[18]

Microprocessors[edit]

See also: Microprocessor chronology and Microcontroller

| This subsection needs additional citations for verification. Relevant discussion may be found on the talk page. Please help improve this article by adding citations to reliable sources. Unsourced material may be challenged and removed. |

A microprocessor incorporates the functions of a computer's central processing unit on a single integrated circuit. It is a multi-purpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and provides results as output.

The development of MOS integrated circuit technology in the 1960s led to the development of the first microprocessors.[19] The 20-bit MP944, developed by Garrett AiResearch for the U.S. Navy's F-14 Tomcat fighter in 1970, is considered by its designer Ray Holt to be the first microprocessor.[20] It was a multi-chip microprocessor, fabricated on six MOS chips. However, it was classified by the Navy until 1998. The 4-bit Intel 4004, released in 1971, was the first single-chip microprocessor. It was made possible with an improvement in MOSFET design, MOS silicon-gate technology (SGT), developed in 1968 at Fairchild Semiconductor by Federico Faggin, who went on to use MOS SGT technology to develop the 4004 with Marcian Hoff, Stanley Mazor and Masatoshi Shima at Intel.[19]

All chips over e.g. a million transistors have lots of memory, usually cache memories in level 1 and 2 or more levels, accounting for most transistors on microprocessors in modern times, where large caches have become the norm. The level 1 caches of the Pentium Pro die accounted for over 14% of its transistors, while the much larger L2 cache was on a separate die, but on-package, so it's not included in the transistor count. Later chips included more levels, L2 or even L3 on-chip. The last DEC Alpha chip made has 90% of it for cache.[21]

While Intel's i960CA small cache of 1 KB, at about 50,000 transistors, isn't a big part of the chip, it alone would have been very large in early microprocessors. In the ARM 3 chip, with 4 KB, the cache was over 63% of the chip, and in the Intel 80486 its larger cache is only over a third of it because the rest of the chip is more complex. So cache memories are the largest factor, except for in early chips with smaller caches or even earlier chips with no cache at all. Then the inherent complexity, e.g. number of instructions, is the dominant factor, more than e.g. the memory the registers of the chip represent.

| Processor | MOS transistor count | Date of introduction | Designer | MOS process | Area |

|---|---|---|---|---|---|

| MP944 (20-bit, 6-chip) | ? | 1970[20][a] | Garrett AiResearch | ? | ? |

| Intel 4004 (4-bit, 16-pin) | 2,250 | 1971 | Intel | 10,000 nm | 12 mm2 |

| Intel 8008 (8-bit, 18-pin) | 3,500 | 1972 | Intel | 10,000 nm | 14 mm2 |

| NEC μCOM-4 (4-bit, 42-pin) | 2,500[22][23] | 1973 | NEC | 7,500 nm[24] | ? |

| Toshiba TLCS-12 (12-bit) | 11,000+[25] | 1973 | Toshiba | 6,000 nm | 32 mm2 |

| Intel 4040 (4-bit, 16-pin) | 3,000 | 1974 | Intel | 10,000 nm | 12 mm2 |

| Motorola 6800 (8-bit, 40-pin) | 4,100 | 1974 | Motorola | 6,000 nm | 16 mm2 |

| Intel 8080 (8-bit, 40-pin) | 6,000 | 1974 | Intel | 6,000 nm | 20 mm2 |

| TMS 1000 (4-bit, 28-pin) | 8,000 | 1974[26] | Texas Instruments | 8,000 nm | 11 mm2 |

| MOS Technology 6502 (8-bit, 40-pin) | 4,528[b][27] | 1975 | MOS Technology | 8,000 nm | 21 mm2 |

| Intersil IM6100 (12-bit, 40-pin; clone of PDP-8) | 4,000 | 1975 | Intersil | ||

| CDP 1801 (8-bit, 2-chip, 40-pin) | 5,000 | 1975 | RCA | ||

| RCA 1802 (8-bit, 40-pin) | 5,000 | 1976 | RCA | 5,000 nm | 27 mm2 |

| Zilog Z80 (8-bit, 4-bit ALU, 40-pin) | 8,500[c] | 1976 | Zilog | 4,000 nm | 18 mm2 |

| Intel 8085 (8-bit, 40-pin) | 6,500 | 1976 | Intel | 3,000 nm | 20 mm2 |

| TMS9900 (16-bit) | 8,000 | 1976 | Texas Instruments | ||

| Motorola MC14500B (1-bit, 16-pin) | ? | 1977 | Motorola | ? | ? |

| Bellmac-8 (8-bit) | 7,000 | 1977 | Bell Labs | 5,000 nm | |

| Motorola 6809 (8-bit with some 16-bit features, 40-pin) | 9,000 | 1978 | Motorola | 5,000 nm | 21 mm2 |

| Intel 8086 (16-bit, 40-pin) | 29,000 | 1978 | Intel | 3,000 nm | 33 mm2 |

| Zilog Z8000 (16-bit) | 17,500[28] | 1979 | Zilog | ||

| Intel 8088 (16-bit, 8-bit data bus) | 29,000 | 1979 | Intel | 3,000 nm | 33 mm2 |

| Motorola 68000 (16/32-bit, 32-bit registers, 16-bit ALU) | 68,000[29] | 1979 | Motorola | 3,500 nm | 44 mm2 |

| Intel 8051 (8-bit, 40-pin) | 50,000 | 1980 | Intel | ||

| WDC 65C02 | 11,500[30] | 1981 | WDC | 3,000 nm | 6 mm2 |

| ROMP (32-bit) | 45,000 | 1981 | IBM | 2,000 nm | |

| Intel 80186 (16-bit, 68-pin) | 55,000 | 1982 | Intel | 3,000 nm | 60 mm2 |

| Intel 80286 (16-bit, 68-pin) | 134,000 | 1982 | Intel | 1,500 nm | 49 mm2 |

| WDC 65C816 (8/16-bit) | 22,000[31] | 1983 | WDC | 3,000 nm[32] | 9 mm2 |

| NEC V20 | 63,000 | 1984 | NEC | ||

| Motorola 68020 (32-bit; 114 pins used) | 190,000[33] | 1984 | Motorola | 2,000 nm | 85 mm2 |

| Intel 80386 (32-bit, 132-pin; no cache) | 275,000 | 1985 | Intel | 1,500 nm | 104 mm2 |

| ARM 1 (32-bit; no cache) | 25,000[33] | 1985 | Acorn | 3,000 nm | 50 mm2 |

| Novix NC4016 (16-bit) | 16,000[34] | 1985[35] | Harris Corporation | 3,000 nm[36] | |

| SPARC MB86900 (32-bit; no cache) | 110,000[37] | 1986 | Fujitsu | 1,200 nm | |

| NEC V60[38] (32-bit; no cache) | 375,000 | 1986 | NEC | 1,500 nm | |

| ARM 2 (32-bit, 84-pin; no cache) | 27,000[39][33] | 1986 | Acorn | 2,000 nm | 30.25 mm2 |

| Z80000 (32-bit; very small cache) | 91,000 | 1986 | Zilog | ||

| NEC V70[38] (32-bit; no cache) | 385,000 | 1987 | NEC | 1,500 nm | |

| Hitachi Gmicro/200[40] | 730,000 | 1987 | Hitachi | 1,000 nm | |

| Motorola 68030 (32-bit, very small caches) | 273,000 | 1987 | Motorola | 800 nm | 102 mm2 |

| TI Explorer's 32-bit Lisp machine chip | 553,000[41] | 1987 | Texas Instruments | 2,000 nm[42] | |

| DEC WRL MultiTitan | 180,000[43] | 1988 | DEC WRL | 1,500 nm | 61 mm2 |

| Intel i960 (32-bit, 33-bit memory subsystem, no cache) | 250,000[44] | 1988 | Intel | 1,500 nm[45] | |

| Intel i960CA (32-bit, cache) | 600,000[45] | 1989 | Intel | 800 nm | 143 mm2 |

| Intel i860 (32/64-bit, 128-bit SIMD, cache, VLIW) | 1,000,000[46] | 1989 | Intel | ||

| Intel 80486 (32-bit, 4 KB cache) | 1,180,235 | 1989 | Intel | 1000 nm | 173 mm2 |

| ARM 3 (32-bit, 4 KB cache) | 310,000 | 1989 | Acorn | 1,500 nm | 87 mm2 |

| Motorola 68040 (32-bit, 8 KB caches) | 1,200,000 | 1990 | Motorola | 650 nm | 152 mm2 |

| R4000 (64-bit, 16 KB of caches) | 1,350,000 | 1991 | MIPS | 1,000 nm | 213 mm2 |

| ARM 6 (32-bit, no cache for this 60 variant) | 35,000 | 1991 | ARM | 800 nm | |

| Hitachi SH-1 (32-bit, no cache) | 600,000[47] | 1992[48] | Hitachi | 800 nm | 10 mm2 |

| Intel i960CF (32-bit, cache) | 900,000[45] | 1992 | Intel | 125 mm2 | |

| DEC Alpha 21064 (64-bit, 290-pin; 16 KB of caches) | 1,680,000 | 1992 | DEC | 750 nm | 233.52 mm2 |

| Hitachi HARP-1 (32-bit, cache) | 2,800,000[49] | 1993 | Hitachi | 500 nm | 267 mm2 |

| Pentium (32-bit, 16 KB of caches) | 3,100,000 | 1993 | Intel | 800 nm | 294 mm2 |

| ARM700 (32-bit; 8 KB cache) | 578,977[50] | 1994 | ARM | 700 nm | 68.51 mm2 |

| MuP21 (21-bit,[51] 40-pin; includes video) | 7,000[52] | 1994 | Offete Enterprises | 1200 nm | |

| Motorola 68060 (32-bit, 16 KB of caches) | 2,500,000 | 1994 | Motorola | 600 nm | 218 mm2 |

| SA-110 (32-bit, 32 KB of caches) | 2,500,000[33] | 1995 | Acorn/DEC/Apple | 350 nm | 50 mm2 |

| Pentium Pro (32-bit, 16 KB of caches;[53] L2 cache on-package, but on separate die) | 5,500,000[54] | 1995 | Intel | 500 nm | 307 mm2 |

| AMD K5 (32-bit, caches) | 4,300,000 | 1996 | AMD | 500 nm | 251 mm2 |

| Hitachi SH-4 (32-bit, caches) | 10,000,000[55] | 1997 | Hitachi | 200 nm[56] | 42 mm2[57] |

| Pentium II Klamath (32-bit, 64-bit SIMD, caches) | 7,500,000 | 1997 | Intel | 350 nm | 195 mm2 |

| AMD K6 (32-bit, caches) | 8,800,000 | 1997 | AMD | 350 nm | 162 mm2 |

| F21 (21-bit; includes e.g. video) | 15,000 | 1997[52] | Offete Enterprises | ||

| AVR (8-bit, 40-pin; w/memory) | 140,000 (48,000 excl. memory[58]) | 1997 | Nordic VLSI/Atmel | ||

| Pentium II Deschutes (32-bit, large cache) | 7,500,000 | 1998 | Intel | 250 nm | 113 mm2 |

| ARM 9TDMI (32-bit, no cache) | 111,000[33] | 1999 | Acorn | 350 nm | 4.8 mm2 |

| Pentium III Katmai (32-bit, 128-bit SIMD, caches) | 9,500,000 | 1999 | Intel | 250 nm | 128 mm2 |

| Emotion Engine (64-bit, 128-bit SIMD, cache) | 13,500,000[59] | 1999 | Sony/Toshiba | 180 nm[60] | 240 mm2[61] |

| Pentium II Mobile Dixon (32-bit, caches) | 27,400,000 | 1999 | Intel | 180 nm | 180 mm2 |

| AMD K6-III (32-bit, caches) | 21,300,000 | 1999 | AMD | 250 nm | 118 mm2 |

| AMD K7 (32-bit, caches) | 22,000,000 | 1999 | AMD | 250 nm | 184 mm2 |

| Gekko (32-bit, large cache) | 21,000,000[62] | 2000 | IBM/Nintendo | 180 nm | 43 mm2 |

| Pentium III Coppermine (32-bit, large cache) | 21,000,000 | 2000 | Intel | 180 nm | 80 mm2 |

| Pentium 4 Willamette (32-bit, large cache) | 42,000,000 | 2000 | Intel | 180 nm | 217 mm2 |

| SPARC64 V (64-bit, large cache) | 191,000,000[63] | 2001 | Fujitsu | 130 nm[64] | 290 mm2 |

| Pentium III Tualatin (32-bit, large cache) | 45,000,000 | 2001 | Intel | 130 nm | 81 mm2 |

| Pentium 4 Northwood (32-bit, large cache) | 55,000,000 | 2002 | Intel | 130 nm | 145 mm2 |

| Itanium 2 McKinley (64-bit, large cache) | 220,000,000 | 2002 | Intel | 180 nm | 421 mm2 |

| DEC Alpha 21364 (64-bit, 946-pin, SIMD, very large caches) | 152,000,000[21] | 2003 | DEC | 180 nm | 397 mm2 |

| Barton (32-bit, large cache) | 54,300,000 | 2003 | AMD | 130 nm | 101 mm2 |

| AMD K8 (64-bit, large cache) | 105,900,000 | 2003 | AMD | 130 nm | 193 mm2 |

| Itanium 2 Madison 6M (64-bit) | 410,000,000 | 2003 | Intel | 130 nm | 374 mm2 |

| Pentium 4 Prescott (32-bit, large cache) | 112,000,000 | 2004 | Intel | 90 nm | 110 mm2 |

| SPARC64 V+ (64-bit, large cache) | 400,000,000[65] | 2004 | Fujitsu | 90 nm | 294 mm2 |

| Itanium 2 (64-bit;9 MB cache) | 592,000,000 | 2004 | Intel | 130 nm | 432 mm2 |

| Pentium 4 Prescott-2M (32-bit, large cache) | 169,000,000 | 2005 | Intel | 90 nm | 143 mm2 |

| Pentium D Smithfield (32-bit, large cache) | 228,000,000 | 2005 | Intel | 90 nm | 206 mm2 |

| Xenon (64-bit, 128-bit SIMD, large cache) | 165,000,000 | 2005 | IBM | 90 nm | |

| Cell (32-bit, cache) | 250,000,000[66] | 2005 | Sony/IBM/Toshiba | 90 nm | 221 mm2 |

| Pentium 4 Cedar Mill (32-bit, large cache) | 184,000,000 | 2006 | Intel | 65 nm | 90 mm2 |

| Pentium D Presler (32-bit, large cache) | 362,000,000 | 2006 | Intel | 65 nm | 162 mm2 |

| Core 2 Duo Conroe (dual-core 64-bit, large caches) | 291,000,000 | 2006 | Intel | 65 nm | 143 mm2 |

| Dual-core Itanium 2 (64-bit, SIMD, large caches) | 1,700,000,000[67] | 2006 | Intel | 90 nm | 596 mm2 |

| AMD K10 quad-core 2M L3 (64-bit, large caches) | 463,000,000[68] | 2007 | AMD | 65 nm | 283 mm2 |

| ARM Cortex-A9 (32-bit, (optional) SIMD, caches) | 26,000,000[69] | 2007 | ARM | 45 nm | 31 mm2 |

| Core 2 Duo Wolfdale (dual-core 64-bit, SIMD, caches) | 411,000,000 | 2007 | Intel | 45 nm | 107 mm2 |

| POWER6 (64-bit, large caches) | 789,000,000 | 2007 | IBM | 65 nm | 341 mm2 |

| Core 2 Duo Allendale (dual-core 64-bit, SIMD, large caches) | 169,000,000 | 2007 | Intel | 65 nm | 111 mm2 |

| Uniphier | 250,000,000[70] | 2007 | Matsushita | 45 nm | ? |

| SPARC64 VI (64-bit, SIMD, large caches) | 540,000,000 | 2007[71] | Fujitsu | 90 nm | 421 mm2 |

| Core 2 Duo Wolfdale 3M (dual-core 64-bit, SIMD, large caches) | 230,000,000 | 2008 | Intel | 45 nm | 83 mm2 |

| Core i7 (quad-core 64-bit, SIMD, large caches) | 731,000,000 | 2008 | Intel | 45 nm | 263 mm2 |

| AMD K10 quad-core 6M L3 (64-bit, SIMD, large caches) | 758,000,000[68] | 2008 | AMD | 45 nm | 258 mm2 |

| Atom (32-bit, large cache) | 47,000,000 | 2008 | Intel | 45 nm | 24 mm2 |

| SPARC64 VII (64-bit, SIMD, large caches) | 600,000,000 | 2008[72] | Fujitsu | 65 nm | 445 mm2 |

| Six-core Xeon 7400 (64-bit, SIMD, large caches) | 1,900,000,000 | 2008 | Intel | 45 nm | 503 mm2 |

| Six-core Opteron 2400 (64-bit, SIMD, large caches) | 904,000,000 | 2009 | AMD | 45 nm | 346 mm2 |

| SPARC64 VIIIfx (64-bit, SIMD, large caches) | 760,000,000[73] | 2009 | Fujitsu | 45 nm | 513 mm2 |

| 16-core SPARC T3 (64-bit, SIMD, large caches) | 1,000,000,000[74] | 2010 | Sun/Oracle | 40 nm | 377 mm2 |

| Six-core Core i7 (Gulftown) | 1,170,000,000 | 2010 | Intel | 32 nm | 240 mm2 |

| 8-core POWER7 32M L3 (64-bit, SIMD, large caches) | 1,200,000,000 | 2010 | IBM | 45 nm | 567 mm2 |

| Quad-core z196[75] (64-bit, very large caches) | 1,400,000,000 | 2010 | IBM | 45 nm | 512 mm2 |

| Quad-core Itanium Tukwila (64-bit, SIMD, large caches) | 2,000,000,000[76] | 2010 | Intel | 65 nm | 699 mm2 |

| 8-core Xeon Nehalem-EX (64-bit, SIMD, large caches) | 2,300,000,000[77] | 2010 | Intel | 45 nm | 684 mm2 |

| SPARC64 IXfx (64-bit, SIMD, large caches) | 1,870,000,000[78] | 2011 | Fujitsu | 40 nm | 484 mm2 |

| Quad-core + GPU Core i7 (64-bit, SIMD, large caches) | 1,160,000,000 | 2011 | Intel | 32 nm | 216 mm2 |

| Six-core Core i7/8-core Xeon E5 (Sandy Bridge-E/EP) (64-bit, SIMD, large caches) | 2,270,000,000[79] | 2011 | Intel | 32 nm | 434 mm2 |

| 10-core Xeon Westmere-EX (64-bit, SIMD, large caches) | 2,600,000,000 | 2011 | Intel | 32 nm | 512 mm2 |

| Atom "Medfield" (64-bit) | 432,000,000[80] | 2012 | Intel | 32 nm | 64 mm2 |

| SPARC64 X (64-bit, SIMD, caches) | 2,990,000,000[81] | 2012 | Fujitsu | 28 nm | 600 mm2 |

| 8-core AMD Bulldozer (64-bit, SIMD, caches) | 1,200,000,000[82] | 2012 | AMD | 32 nm | 315 mm2 |

| Quad-core + GPU AMD Trinity (64-bit, SIMD, caches) | 1,303,000,000 | 2012 | AMD | 32 nm | 246 mm2 |

| Quad-core + GPU Core i7 Ivy Bridge (64-bit, SIMD, caches) | 1,400,000,000 | 2012 | Intel | 22 nm | 160 mm2 |

| 8-core POWER7+ (64-bit, SIMD, 80 MB L3 cache) | 2,100,000,000 | 2012 | IBM | 32 nm | 567 mm2 |

| Six-core zEC12 (64-bit, SIMD, large caches) | 2,750,000,000 | 2012 | IBM | 32 nm | 597 mm2 |

| 8-core Itanium Poulson (64-bit, SIMD, caches) | 3,100,000,000 | 2012 | Intel | 32 nm | 544 mm2 |

| 61-core Xeon Phi (32-bit, 512-bit SIMD, caches) | 5,000,000,000[83] | 2012 | Intel | 22 nm | 720 mm2 |

| Apple A7 (dual-core 64/32-bit ARM64, "mobile SoC", SIMD, caches) | 1,000,000,000 | 2013 | Apple | 28 nm | 102 mm2 |

| Six-core Core i7 Ivy Bridge E (64-bit, SIMD, caches) | 1,860,000,000 | 2013 | Intel | 22 nm | 256 mm2 |

| 12-core POWER8 (64-bit, SIMD, caches) | 4,200,000,000 | 2013 | IBM | 22 nm | 650 mm2 |

| Xbox One main SoC (64-bit, SIMD, caches) | 5,000,000,000 | 2013 | Microsoft/AMD | 28 nm | 363 mm2 |

| Quad-core + GPU Core i7 Haswell (64-bit, SIMD, caches) | 1,400,000,000[84] | 2014 | Intel | 22 nm | 177 mm2 |

| Apple A8 (dual-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 2,000,000,000 | 2014 | Apple | 20 nm | 89 mm2 |

| 8-core Core i7 Haswell-E (64-bit, SIMD, caches) | 2,600,000,000[85] | 2014 | Intel | 22 nm | 355 mm2 |

| Apple A8X (tri-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 3,000,000,000[86] | 2014 | Apple | 20 nm | 128 mm2 |

| 15-core Xeon Ivy Bridge-EX (64-bit, SIMD, caches) | 4,310,000,000[87] | 2014 | Intel | 22 nm | 541 mm2 |

| 18-core Xeon Haswell-E5 (64-bit, SIMD, caches) | 5,560,000,000[88] | 2014 | Intel | 22 nm | 661 mm2 |

| Quad-core + GPU GT2 Core i7 Skylake K (64-bit, SIMD, caches) | 1,750,000,000 | 2015 | Intel | 14 nm | 122 mm2 |

| Dual-core + GPU Iris Core i7 Broadwell-U (64-bit, SIMD, caches) | 1,900,000,000[89] | 2015 | Intel | 14 nm | 133 mm2 |

| Apple A9 (dual-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 2,000,000,000+ | 2015 | Apple | 14 nm (Samsung) | 96 mm2 (Samsung) |

| 16 nm (TSMC) | 104.5 mm2 (TSMC) | ||||

| Apple A9X (dual core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 3,000,000,000+ | 2015 | Apple | 16 nm | 143.9 mm2 |

| IBM z13 (64-bit, caches) | 3,990,000,000 | 2015 | IBM | 22 nm | 678 mm2 |

| IBM z13 Storage Controller | 7,100,000,000 | 2015 | IBM | 22 nm | 678 mm2 |

| 32-core SPARC M7 (64-bit, SIMD, caches) | 10,000,000,000[90] | 2015 | Oracle | 20 nm | |

| Qualcomm Snapdragon 835 (octa-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 3,000,000,000[91][92] | 2016 | Qualcomm | 10 nm | 72.3 mm2 |

| 10-core Core i7 Broadwell-E (64-bit, SIMD, caches) | 3,200,000,000[93] | 2016 | Intel | 14 nm | 246 mm2[94] |

| Apple A10 Fusion (quad-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 3,300,000,000 | 2016 | Apple | 16 nm | 125 mm2 |

| HiSilicon Kirin 960 (octa-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 4,000,000,000[95] | 2016 | Huawei | 16 nm | 110.00 mm2 |

| 22-core Xeon Broadwell-E5 (64-bit, SIMD, caches) | 7,200,000,000[96] | 2016 | Intel | 14 nm | 456 mm2 |

| 72-core Xeon Phi (64-bit, 512-bit SIMD, caches) | 8,000,000,000 | 2016 | Intel | 14 nm | 683 mm2 |

| Zip CPU (32-bit, for FPGAs) | 1,286 6-LUTs[97] | 2016 | Gisselquist Technology | ||

| Qualcomm Snapdragon 845 (octa-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 5,300,000,000[98] | 2017 | Qualcomm | 10 nm | 94 mm2 |

| Qualcomm Snapdragon 850 (octa-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 5,300,000,000[99] | 2017 | Qualcomm | 10 nm | 94 mm2 |

| Apple A11 Bionic (hexa-core 64/32-bit ARM64 "mobile SoC", SIMD, caches) | 4,300,000,000 | 2017 | Apple | 10 nm | 89.23 mm2 |

| Zeppelin SoC Ryzen (64-bit, SIMD, caches) | 4,800,000,000[100] | 2017 | AMD | 14 nm | 192 mm2 |

| Ryzen 5 1600 Ryzen (64-bit, SIMD, caches) | 4,800,000,000[101] | 2017 | AMD | 14 nm | 213 mm2 |

| Ryzen 5 1600 X Ryzen (64-bit, SIMD, caches) | 4,800,000,000[102] | 2017 | AMD | 14 nm | 213 mm2 |

| IBM z14 (64-bit, |